User’s Hardware Manual_V1.5

Document classification: □ Top secret □ Secret □ Internal information ■ Open

Copyright

The copyright of this manual belongs to Baoding Folinx Embedded Technology Co., Ltd. Without the written permission of our company, no organizations or individuals have the right to copy, distribute, or reproduce any part of this manual in any form, and violators will be held legally responsible.

Forlinx adheres to copyrights of all graphics and texts used in all publications in original or license-free forms.

The drivers and utilities used for the components are subject to the copyrights of the respective manufacturers. The license conditions of the respective manufacturer are to be adhered to. Related license expenses for the operating system and applications should be calculated/declared separately by the related party or its representatives.

Revision History

Date |

User Manual Version |

SoM Version |

Carrier Board Version |

Revision History |

|---|---|---|---|---|

17/12/2025 |

V1.5 |

V1.1 |

V1.1 and above |

Adding SoM power management upgrade solution: |

21/11/2025 |

V1.4 |

V1.1 |

V1.1 and above |

Adding section 2.6.2: Design Guide for Vibration Resistance of the SoM |

12/06/2024 |

V1.3 |

V1.1 |

V1.1 and above |

1. Updating the manual format; |

24/07/2023 |

V1.3 |

V1.1 |

V1.1and above |

1. Updating the front photo of the development board; |

23/04/2023 |

V1.2 |

V1.1 |

V1.1 and above |

Adding an ESD characteristics section and increasing |

27/03/2023 |

V1.1 |

V1.1 |

V1.1 and above |

Correcting the description of the SoM pin functions. |

01/12/2022 |

V1.0 |

V1.1 |

V1.1 |

Initial Version |

Overview

This manual is designed to help users quickly familiarize themselves with the product, understand interface functions and configuration, and primarily discusses the interface functions of the development board, interface introductions, product power consumption, and troubleshooting issues that may arise during use. Some commands were commented to make it easier for you to understand (Adequate and practical for the purpose). For information on pin function multiplexing, hardware troubleshooting methods, etc., please refer to Forlinx’s “FET3588 Pin Function Comparison Table”.

There are total four chapters:

Chapter 1. is CPU overview, briefly introducing its performance and applications;

Chapter 2. is comprehensive introduction to the SoM, including connector pins explanations and function introductions;

Chapter 3. is comprehensive introduction to the development board, divided into multiple chapters, including both hardware principles and simple design ideas;

Chapter 4. mainly describes the board’s power consumption performance and other considerations.

A description of some of the symbols and formats associated with this manual:

Format |

Meaning |

|---|---|

Note |

Note or information that requires special attention, be sure to read carefully. |

📚 |

Relevant notes on the test chapters. |

🛤️ ️ |

Indicates the related path. |

1. RK3588 Description

The RK3588 is a general-purpose SoC with ARM architecture, integrating quad-core Cortex-A76 and quad-core Cortex-A55 CPU in a typical size core architecture, and the GPU is equipped with G610 MP4 GPU to run complex graphics processing smoothly. The embedded 3D GPU makes the RK3588 fully compatible with OpenGLES 1.1, 2.0, and 3.2, OpenCL up to 2.2, and Vulkan 1.2. The unique 2D hardware engine with MMU can maximize display performance and provide smooth operation. 6 TOPs NPU empowers various AI scenarios, offering a wide range of possibilities for applications such as local offline AI computing in complex scenarios and sophisticated video stream analysis. Built-in a variety of powerful embedded hardware engines, which supports 8K@60fps H.265 and VP9 decoder, 8K@30fps H.264 and 4K@60fps AV1 decoder, 8K@30fps H.264 and H.265 encoders, high-quality JPEG encoders/decoders, and specialized image pre-processors & post-processors.

The RK3588 introduces a new generation of fully hardware-based maximum 48-megapixel ISP, which implements many computing accelerators such as HDR,3A, LSC,3DNR, 2DNR, sharpening, dehaze, fish-eye correction, gamma correction, etc., and is widely-used in graphics post-processing. The RK3588 integrates a new generation NPU processor of Rockchip, which can support INT4/INT8/INT16/FP16 mixed operation; its powerful compatibility makes it easy to convert a series framework network models based on TensorFlow/ MXNet/PyTorch/Caffe etc. The RK3588 features high-performance, 4-channel external memory connectivity (LPDDR4/LPDDR4X/LPDDR5), which can support harsh memory bandwidths.

Target Applications:

Information Release Terminals

Intelligent Cabin

Smart Screen

AR/VR

Edge Computing

High-end IPC

Smart NVR

Premium Pad

ARM PC

……

RK3588 Block Diagram

2. FET3588-C SoM Description

2.1 FET3588-C SoM

Front

Back

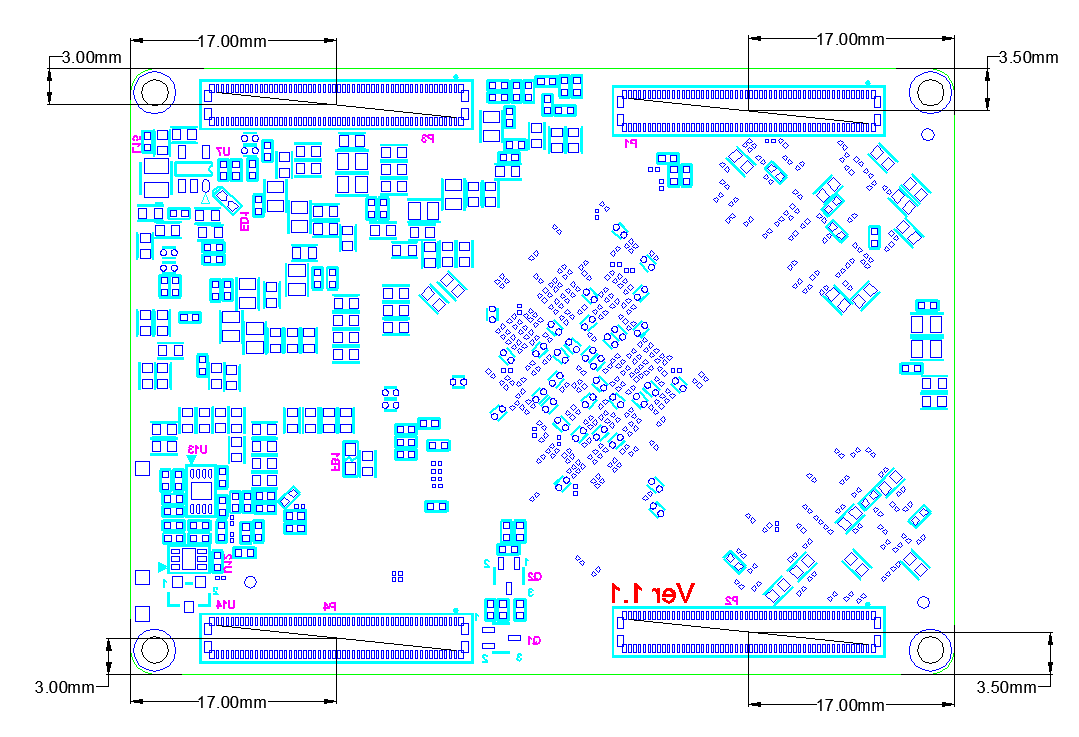

2.2 FET3588-C SoM Dimension Diagram

Top Layer Dimension Diagram

Bottom Layer Dimension Diagram

Structure size: 68mm × 50mm, dimensional tolerance ± 0.15mm, refer to DXF file for more dimensional information.

Plate making process: 1.6mm thickness, 10-layer immersion gold PCB.

Connectors: Four 0.4mm pitch, 100pin board-to-board connectors. See the appendix for the connector dimension drawing.

Four mounting holes with a diameter of 2.2 mm are reserved at the four corners of the core board. For use in a vibrating environment, fixing screws can be installed to improve the reliability of the product connection.

You can refer to the development board design and use M2, L=1.5mm patch nuts on the carrier board.

2.3 Performance Parameters

2.3.1 System Main Frequency

Name |

Specification |

Description |

|||

|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

||

System Frequency Arm® Cortex®-A76 |

- |

- |

2400 |

MHz |

- |

System Frequency Arm® Cortex®-A55 |

- |

- |

1800 |

MHz |

|

System Frequency Arm® Cortex®-M0 |

- |

- |

- |

- |

- |

2.3.2 Power Parameter

Parameter |

Pin Number |

Specification |

Description |

|||

|---|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

|||

Main Power Supply Voltage |

12V |

5V |

12 |

13V |

V |

- |

2.3.3 Operating Environment

Parameter |

Specification |

Description |

||||

|---|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

|||

Operating Temperature |

Operating environment |

0 |

25 |

+80 |

℃ |

Commercial level |

Storage Environment |

-40 |

25 |

+125 |

℃ |

||

Operating Environment |

-40 |

25 |

+85 |

℃ |

Industrial-grade |

|

Storage Environment |

-40 |

25 |

+125 |

℃ |

||

Humidity |

Operating Environment |

10 |

- |

90 |

%RH |

No condensation |

Storage Environment |

5 |

- |

95 |

%RH |

2.3.4 SoM Interface Speed

Parameter |

Specification |

Description |

|||

|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

||

Serial Port Communication Speed |

- |

115200 |

4M |

bps |

- |

SPI Clock Frequency |

- |

- |

50 |

MHz |

- |

I2C Communication Speed |

- |

100 |

400 |

Kbps |

- |

USB3.0 Interface Speed |

- |

- |

5 |

Gbps |

- |

USB2.0 Interface Speed |

- |

- |

480 |

Mbps |

- |

CAN Communication Speed |

- |

- |

1 |

Mbps |

- |

PCIe2.1 |

- |

- |

5 |

Gbps |

- |

PCIe3.0 |

- |

- |

8 |

Gbps |

- |

2.3.5 ESD Features

Parameter |

Specification |

Unit |

Application Scope |

|

|---|---|---|---|---|

Minimum |

Maximum |

|||

ESD HBM(ESDA/JEDEC JS-001-2017) |

-2000 |

2000 |

V |

Signals exported from SoM |

ESD CDM(ESDA/JEDEC JS-002-2018) |

-250 |

250 |

V |

Signals exported from SoM |

Note:

The above data is provided by Rockchip;

As all the signals exported from SoM are electrostatic sensitive signals, the interfaces should be well protected from static electricity in the carrier board design and the SoM transportation, assembling, and use.

2.4 SoM Interface Speed

Function |

Quantity |

Parameter |

|---|---|---|

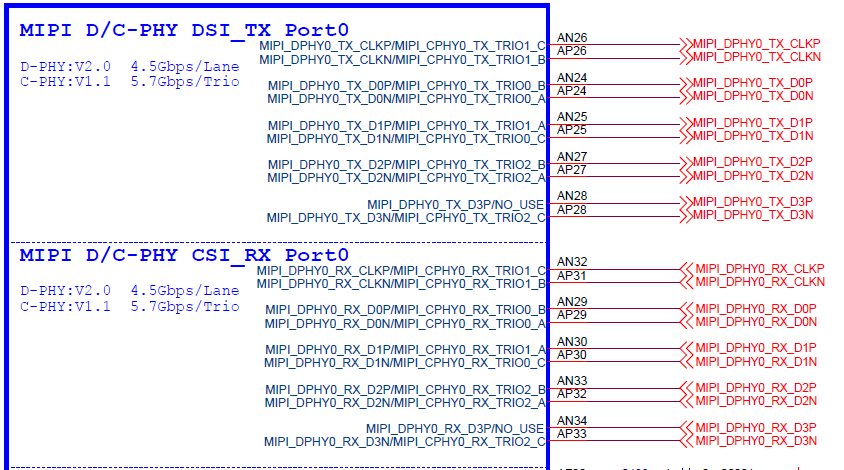

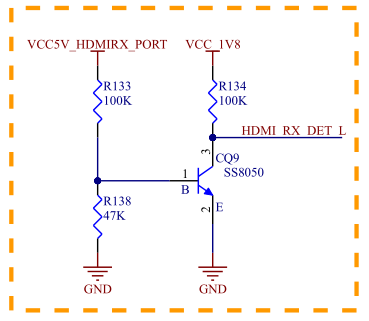

MIPI DC PHY |

2 |

• Supports DPHY or CPHY; |

MIPI CSI DPHY*1 |

4 |

• 2-lane MIPI DPHY V1.2, with a maximum data rate of 2.5 Gbps per lane; |

DVP |

1 |

•8/10/12/16-bit standard DVP interface, maximum data input of 150MHz; |

HDMI RX |

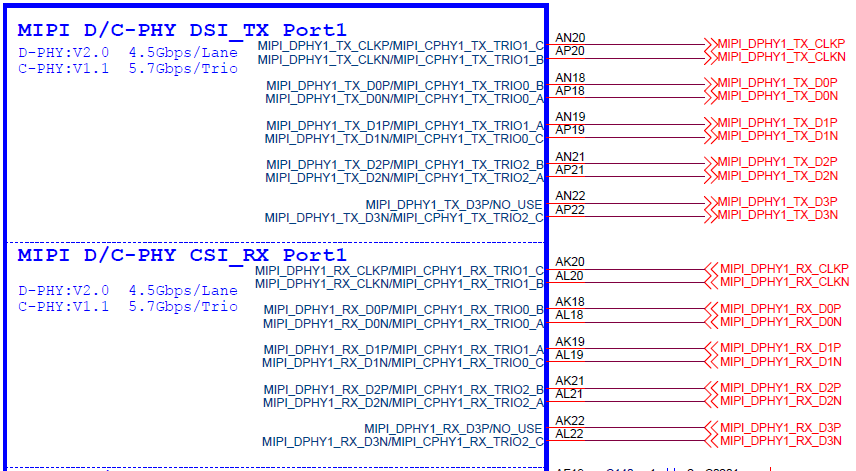

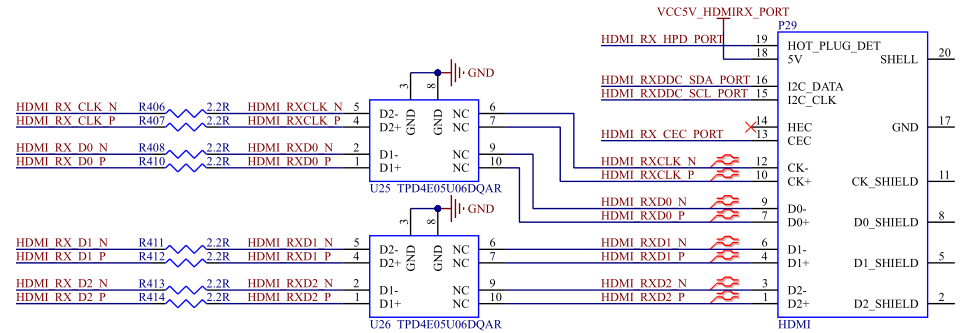

1 |

•Supports 3.4Gbps~6Gbps HDMI 2.0; |

HDMI/eDP TX |

≤2 |

• Supports 2 x combined HDMI/eDP TX interfaces (HDMI and eDP cannot operate simultaneously), with each interface supporting x1, x2, and x4 configurations; |

DP TX |

2 |

• Supports 2 x DP TX 1.4a interfaces, which can be connected to USB 3.1 Gen1 and support 1/2/4 lanes; |

MIPI DSI |

2 |

•Supports 2 x MIPI DPHY 2.0 or CPHY 1.1, with a resolution up to 4K@60Hz; |

BT.1120 Output |

1 |

•Supports RGB format (up to 8 bit), with a data speed up to 150 MHz; |

I2S |

≤4 |

•The sending and receiving clocks can reach up to 50 MHz; |

SPDIF |

2 |

•Supports 2 x 16bit audio data storage; |

PDM |

2 |

•Up to 8 channels, with audio resolution ranging from 16 to 24 bits and a sampling rate of up to 192 KHz; |

DSM PWM |

1 |

•Convert audio PCM data into direct bitstream digital coding to output 1bit signal data stream, and the output digital signal is filtered to obtain an audio signal; |

Ethernet |

2 |

•2 x GMAC, with led out RGMII / RMII interfaces ; |

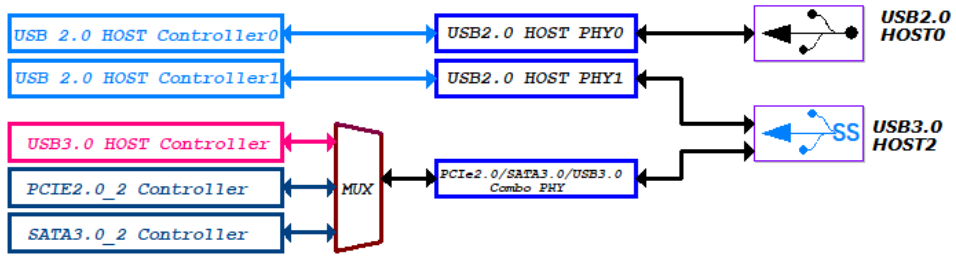

USB3.1 Gen1*2 |

3 |

•The USB3.1 Gen1 data rate can reach up to 5 Gbps; |

USB 2.0 Host |

2 |

•Supports 2 x USB2.0 Host; |

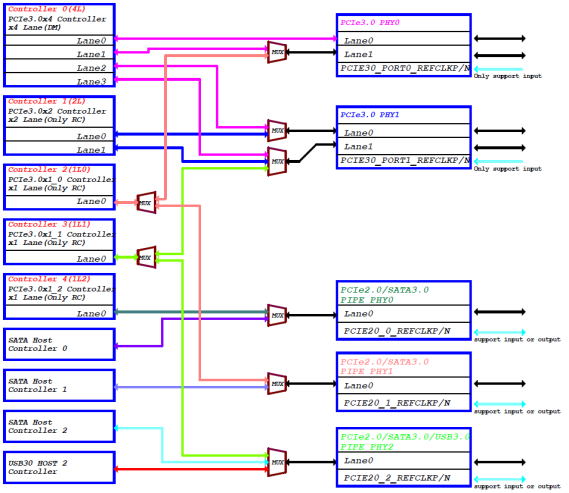

PCIe 2.0*2 |

≤3 |

•Each PCIe 2.1 interface supports 1 lane, with data rate up to 5 Gbps; |

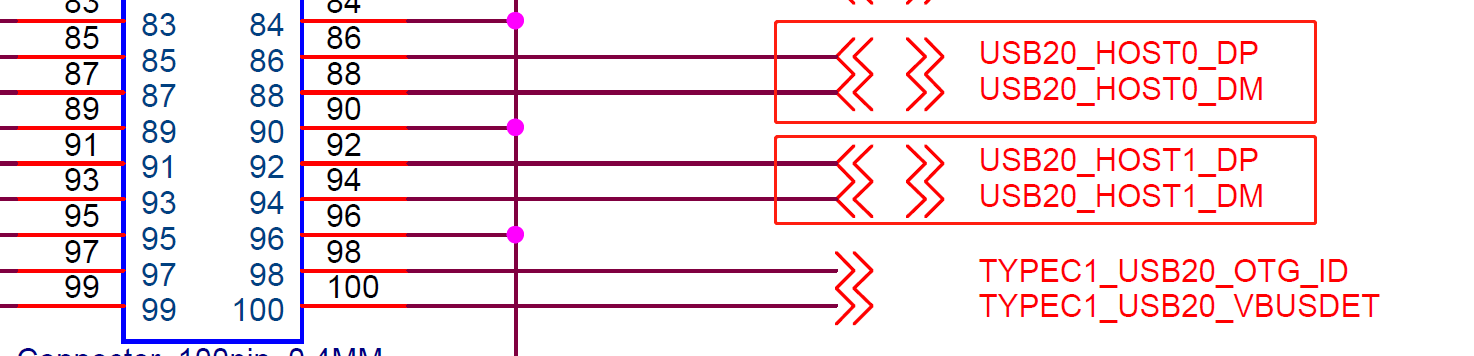

PCIe 3.0*2 |

≤4 |

•Supports RC and EP, with data rate up to 8 Gbps |

SDMMC |

1 |

•Integration of one SDMMC controller and one SDIO controller, both supporting SDIO 3.0 protocol, and MMC V4.51 protocol; |

SDIO |

1 |

|

SPI |

≤5 |

•Each controller supports two chip - select output channels; |

I2C |

≤9 |

•Supports both 7 - bit and 10 - bit address modes; |

UART |

≤10 |

•2 x built - in 64 - bit FIFO, which can be used for TX and RX respectively; |

SATA*2 |

≤3 |

•3 x SATA 3.0 controllers, which are multiplexed with PCIe and USB3_HOST2 controllers for PIPE PHY0/1/2; |

PWM |

≤16 |

•Support up to 16 on-chip PWM with interrupt-based operation and capture mode; |

ADC |

≤8 |

•Support 8 x12bit single-ended input SAR-ADC with sampling rate up to 1MS/s; |

Note: The interface number listed in the table is the hardware design or CPU theoretical maximum quantity, and most of the function pins are multiplexed. Please refer to the PinMux table for easy configuration.

1. Supported MIPI camera combination:

2 MIPI DCPHY + 4 x 2 lanes MIPI CSI DPHY

2 MIPI DCPHY + 1 x 4 lanes MIPI CSI DPHY

2 MIPI DCPHY + 2 x 4 lanes MIPI CSI DPHY

2. USB3.1, PCIe2.0 and SATA 3.0 are multiplexed, please refer to the following carrier board design chapters for more information.

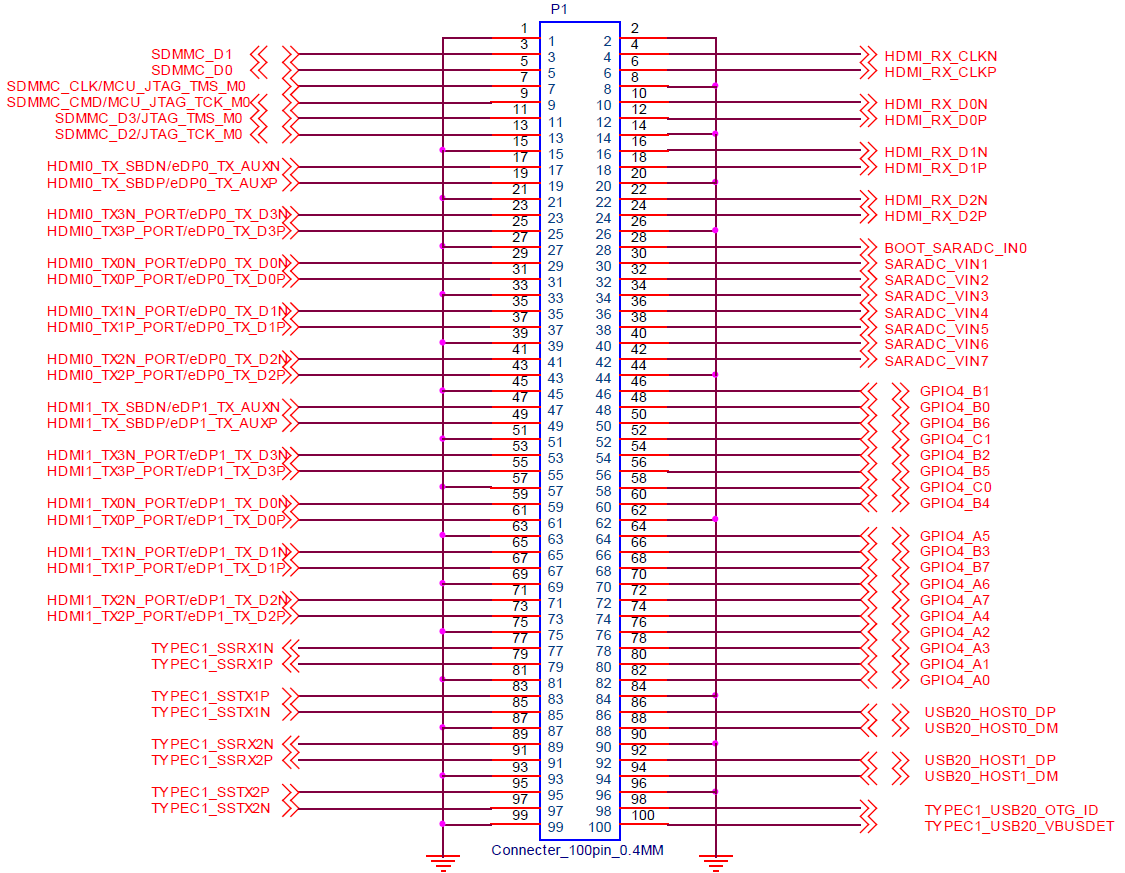

2.5 FET3588-C SoM Pins Definition

2.5.1 FET3588-C SoM Pins Schematic

2.5.2 FET3588-C SoM Pins Description

Note1:

Num ——SoM connector pin no.:

Ball —— CPU pin ball no.

GPIO ——CPU pin general I/O port serial number

Vol ——Pin signal level

Note 2:

Signal Name——SoM connector network name

Pin Description—— SoM Pin Signal Descriptions

Default Function——Please don’t make any modifications for all SoM pin functions regulated in the “default functions” of the following table, otherwise, it may have conflicts with the factory driver. Please contact us with any questions in time.

Note 3: The pins marked with “Do not use for carrier board” in the “Pin Description” are those used by the SoM, and should not be used in the carrier board design.

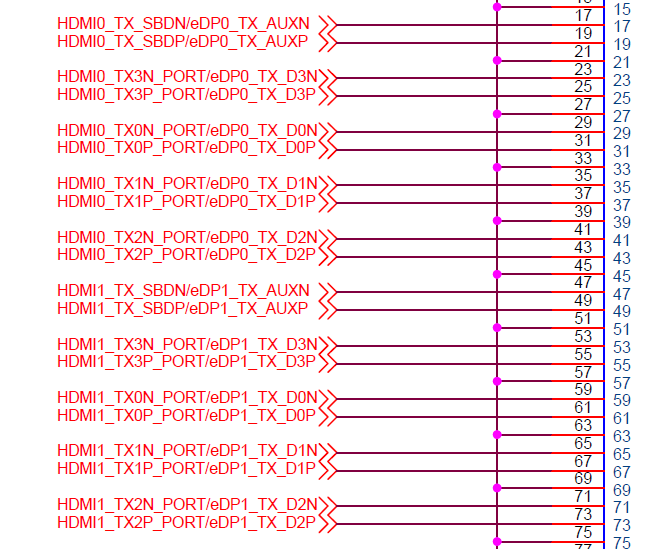

Table 1 RIGHT _ DOWN (P1) Connector Interface (Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

- |

GND |

- |

- |

Ground |

GND |

3 |

AD1 |

SDMMC_D1 |

GPIO4_D1_u |

3.3V |

SD/MMC Interface data signal 1 |

SDMMC_D1 |

5 |

AD2 |

SDMMC_D0 |

GPIO4_D0_u |

3.3V |

SD/MMC Interface data signal 0 |

SDMMC_D0 |

7 |

AE1 |

SDMMC_CLK/MCU_JTAG_TMS_M0 |

GPIO4_D5_d |

3.3V |

SD/MMC Interface clock signal |

SDMMC_CLK |

9 |

AE2 |

SDMMC_CMD/MCU_JTAG_TCK_M0 |

GPIO4_D4_u |

3.3V |

SD/MMC Interface order signal |

SDMMC_CMD |

11 |

AF1 |

SDMMC_D3/JTAG_TMS_M0 |

GPIO4_D3_u |

3.3V |

SD/MMC Interface data signal 3 |

SDMMC_D3 |

13 |

AF2 |

SDMMC_D2/JTAG_TCK_M0 |

GPIO4_D2_u |

3.3V |

SD/MMC Interface data signal 2 |

SDMMC_D2 |

15 |

- |

GND |

- |

- |

Ground |

GND |

17 |

AG1 |

HDMI0_TX_SBDN/EDP0_TX_AUXN |

- |

- |

HDMISBD signal- |

HDM0_TX0_SBD_N |

19 |

AG2 |

HDMI0_TX_SBDP/EDP0_TX_AUXP |

- |

- |

HDMISBD signal+ |

HDM0_TX0_SBD_P |

21 |

- |

GND |

- |

- |

Ground |

GND |

23 |

AH2 |

HDMI0_TX3N_PORT/EDP0_TX_D3N |

- |

- |

HDMI differential signal 3- |

HDMI_TX0_D3_N |

25 |

AH3 |

HDMI0_TX3P_PORT/EDP0_TX_D3P |

- |

- |

HDMI differential signal 3+ |

HDMI_TX0_D3_P |

27 |

- |

GND |

- |

- |

Ground |

GND |

29 |

AJ1 |

HDMI0_TX0N_PORT/EDP0_TX_D0N |

- |

- |

HDMI differential signal 0- |

HDMI_TX0_D0_N |

31 |

AJ2 |

HDMI0_TX0P_PORT/EDP0_TX_D0P |

- |

- |

HDMI differential signal 0+ |

HDMI_TX0_D0_P |

33 |

- |

GND |

- |

- |

Ground |

GND |

35 |

AK2 |

HDMI0_TX1N_PORT/EDP0_TX_D1N |

- |

- |

HDMI differential signal 1- |

HDMI_TX0_D1_N |

37 |

AK3 |

HDMI0_TX1P_PORT/EDP0_TX_D1P |

- |

HDMI Differential signal 1+ |

HDMI_TX0_D1_P |

|

39 |

- |

GND |

- |

- |

Ground |

GND |

41 |

AL1 |

HDMI0_TX2N_PORT/EDP0_TX_D2N |

- |

- |

HDMI differential signal 2- |

HDMI_TX0_D2_N |

43 |

AL2 |

HDMI0_TX2P_PORT/EDP0_TX_D2P |

- |

- |

HDMI differential signal 2+ |

HDMI_TX0_D2_P |

45 |

- |

GND |

- |

- |

Ground |

GND |

47 |

AP2 |

HDMI1_TX_SBDN/EDP1_TX_AUXN |

- |

- |

eDP auxiliary data- |

EDP_TX1_AUX_N |

49 |

AN2 |

HDMI1_TX_SBDP/EDP1_TX_AUXP |

- |

- |

eDP Auxiliary data + |

EDP_TX1_AUX_P |

51 |

- |

GND |

- |

- |

Ground |

GND |

53 |

AN3 |

HDMI1_TX3N_PORT/EDP1_TX_D3N |

- |

- |

eDP Differential signal 3- |

EDP_TX1_D3_N |

55 |

AM3 |

HDMI1_TX3P_PORT/EDP1_TX_D3P |

- |

- |

eDP Differential signal 3+ |

EDP_TX1_D3_P |

57 |

- |

GND |

- |

- |

Ground |

GND |

59 |

AP4 |

HDMI1_TX0N_PORT/EDP1_TX_D0N |

- |

- |

eDP Differential signal 0- |

EDP_TX1_D0_N |

61 |

AN4 |

HDMI1_TX0P_PORT/EDP1_TX_D0P |

- |

- |

eDP Differential signal 0+ |

EDP_TX1_D0_P |

63 |

- |

GND |

- |

- |

Ground |

GND |

65 |

AN5 |

HDMI1_TX1N_PORT/EDP1_TX_D1N |

- |

- |

eDP Differential signal 1- |

EDP_TX1_D1_N |

67 |

AM5 |

HDMI1_TX1P_PORT/EDP1_TX_D1P |

- |

- |

eDP Differential signal 1+ |

EDP_TX1_D1_P |

69 |

- |

GND |

- |

- |

Ground |

GND |

71 |

AP6 |

HDMI1_TX2N_PORT/EDP1_TX_D2N |

- |

- |

eDP Differential signal 2- |

EDP_TX1_D2_N |

73 |

AN6 |

HDMI1_TX2P_PORT/EDP1_TX_D2P |

- |

- |

eDP Differential signal 2+ |

EDP_TX1_D2_P |

75 |

- |

GND |

- |

- |

Ground |

GND |

77 |

AP8 |

TYPEC1_SSRX1N |

- |

- |

TYPEC1 Receiving differential signals1- |

TYPEC1_SSRX1_N |

79 |

AN8 |

TYPEC1_SSRX1P |

- |

- |

TYPEC1 Receiving differential signals 1+ |

TYPEC1_SSRX1_P |

81 |

- |

GND |

- |

- |

Ground |

GND |

83 |

AP9 |

TYPEC1_SSTX1P |

- |

- |

TYPEC1 Sending differential signals 1+ |

TYPEC1_SSTX1_P |

85 |

AN9 |

TYPEC1_SSTX1N |

- |

- |

TYPEC1 Sending differential signals 1- |

TYPEC1_SSTX1_N |

87 |

- |

GND |

- |

- |

Ground |

GND |

89 |

AP10 |

TYPEC1_SSRX2N |

- |

- |

TYPEC1 Receiving differential signals2- |

TYPEC1_SSRX2_N |

91 |

AN10 |

TYPEC1_SSRX2P |

- |

- |

TYPEC1 Receiving differential signals2+ |

TYPEC1_SSRX2_P |

93 |

- |

GND |

- |

- |

Ground |

GND |

95 |

AP11 |

TYPEC1_SSTX2P |

- |

- |

TYPEC1 Sending differential signals2+ |

TYPEC1_SSTX2_P |

97 |

AN11 |

TYPEC1_SSTX2N |

- |

- |

TYPEC1 Sending differential signals2- |

TYPEC1_SSTX2_N |

99 |

- |

GND |

- |

- |

Ground |

GND |

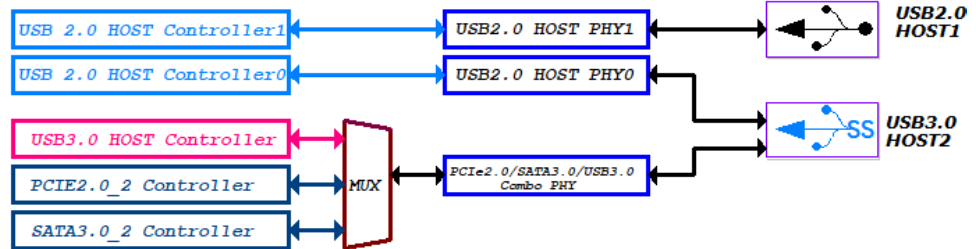

Table 2 RIGHT _ DOWN (P1) Connector Interface (Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

AF5 |

HDMI_RX_CLKN |

- |

- |

HDMI Differential Clock Signals- |

HDMI_RX_CLK_N |

6 |

AF6 |

HDMI_RX_CLKP |

- |

- |

HDMI Differential Clock Signals+ |

HDMI_RX_CLK_P |

8 |

- |

GND |

- |

- |

Ground |

GND |

10 |

AG4 |

HDMI_RX_D0N |

- |

- |

HDMI Receiving differential signals0- |

HDMI_RX_D0_N |

12 |

AG5 |

HDMI_RX_D0P |

- |

- |

HDMI Receiving differential signals 0+ |

HDMI_RX_D0_P |

14 |

- |

GND |

- |

- |

Ground |

GND |

16 |

AH5 |

HDMI_RX_D1N |

- |

- |

HDMI Receiving differential signals1- |

HDMI_RX_D1_N |

18 |

AH6 |

HDMI_RX_D1P |

- |

- |

HDMI Receiving differential signals 1+ |

HDMI_RX_D1_P |

20 |

- |

GND |

- |

- |

Ground |

GND |

22 |

AJ4 |

HDMI_RX_D2N |

- |

- |

HDMI Receiving differential signals2- |

HDMI_RX_D2_N |

24 |

AJ5 |

HDMI_RX_D2P |

- |

- |

HDMI Receiving differential signals 2+ |

HDMI_RX_D2_P |

26 |

- |

GND |

- |

- |

Ground |

GND |

28 |

AM16 |

BOOT_SARADC_IN0 |

- |

1.8V |

BOOT start configuration input |

BOOT_SARADC_IN0 |

30 |

AL16 |

SARADC_VIN1 |

- |

1.8V |

General ADC1 |

SARADC_VIN1_KEY/RECOVERY |

32 |

AK16 |

SARADC_VIN2 |

- |

1.8V |

General ADC2 |

SARADC_VIN2 |

34 |

AN17 |

SARADC_VIN3 |

- |

1.8V |

General ADC3 |

SARADC_VIN3_HP_HOOK |

36 |

AM17 |

SARADC_VIN4 |

- |

1.8V |

General ADC4 |

SARADC_VIN4 |

38 |

AK15 |

SARADC_VIN5 |

- |

1.8V |

General ADC5 |

SARADC_VIN5 |

40 |

AL17 |

SARADC_VIN6 |

- |

1.8V |

General ADC6 |

SARADC_VIN6 |

42 |

AK17 |

SARADC_VIN7 |

- |

1.8V |

General ADC7 |

SARADC_VIN7 |

44 |

- |

GND |

- |

- |

Ground |

GND |

46 |

AL24 |

GPIO4_B1 |

GPIO4_B1_u |

3.3V |

HDMI0_TX ON signal |

HDMI0_TX_ON_H |

48 |

AK26 |

GPIO4_B0 |

GPIO4_B0_d |

3.3V |

TYPEC0_SBU2 signal |

TYPEC0_SBU2_DC |

50 |

AJ27 |

GPIO4_B6 |

GPIO4_B6_d |

3.3V |

PCIE30X4 Reset |

PCIE30X4_PERSTn_M1_L |

52 |

AK24 |

GPIO4_C1 |

GPIO4_C1_d |

3.3V |

HDMICEC signal |

HDMITX0_CEC_M0 |

54 |

AK25 |

GPIO4_B2 |

GPIO4_B2_u |

3.3V |

CAN1 data receiving |

CAN1_RX_M1 |

56 |

AJ26 |

GPIO4_B5 |

GPIO4_B5_d |

3.3V |

PCIE30X4 link insertion detection |

PCIE30X4_WAKEn_M1_L |

58 |

AJ25 |

GPIO4_C0 |

GPIO4_C0_u |

3.3V |

HDMI serial data |

HDMITX0_SDA_M0 |

60 |

AL26 |

GPIO4_B4 |

GPIO4_B4_u |

3.3V |

PCIE30X4_CLKREQn signal |

PCIE30X4_CLKREQn_M1_L |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

AK27 |

GPIO4_A5 |

GPIO4_A5_d |

3.3V |

PCIEx1 Reset |

PCIEx1_0_PERSTn_M1_L |

66 |

AM25 |

GPIO4_B3 |

GPIO4_B3_u |

3.3V |

CAN1 data sending |

CAN1_TX_M1 |

68 |

AJ28 |

GPIO4_B7 |

GPIO4_B7_u |

3.3V |

HDMI Serial clock |

HDMITX0_SCL_M0 |

70 |

AL27 |

GPIO4_A6 |

GPIO4_A6_d |

3.3V |

I2C5 clock |

I2C5_SCL_M2 |

72 |

AM27 |

GPIO4_A7 |

GPIO4_A7_d |

3.3V |

I2C5 Data |

I2C5_SDA_M2 |

74 |

AL28 |

GPIO4_A4 |

GPIO4_A4_d |

3.3V |

PCIEx1 link insertion detection |

PCIEx1_0_WAKEn_M1_L |

76 |

AM29 |

GPIO4_A2 |

GPIO4_A2_d |

3.3V |

TYPEC1_SBU2 signal |

TYPEC1_SBU2_DC |

78 |

AL29 |

GPIO4_A3 |

GPIO4_A3_d |

3.3V |

PCIEx1_0_CLKREQn signal |

PCIEx1_0_CLKREQn_M1_L |

80 |

AL30 |

GPIO4_A1 |

GPIO4_A1_d |

3.3V |

TYPEC1_SBU1 signal |

TYPEC1_SBU1_DC |

82 |

AK30 |

GPIO4_A0 |

GPIO4_A0_d |

3.3V |

TYPEC0_SBU1 signal |

TYPEC0_SBU1_DC |

84 |

- |

GND |

- |

- |

Ground |

GND |

86 |

AK6 |

USB20_HOST0_DP |

- |

- |

USB20_HOST0 data+ |

USB20_HOST0_D_P |

88 |

AL6 |

USB20_HOST0_DM |

- |

- |

USB20_HOST0 data- |

USB20_HOST0_D_N |

90 |

- |

GND |

- |

- |

Ground |

GND |

92 |

AL7 |

USB20_HOST1_DP |

- |

- |

USB20_HOST1 data+ |

USB20_HOST1_D_P |

94 |

AM7 |

USB20_HOST1_DM |

- |

- |

USB20_HOST1 data- |

USB20_HOST1_D_N |

96 |

- |

GND |

- |

- |

Ground |

GND |

98 |

AK8 |

TYPEC1_USB20_OTG_ID |

- |

- |

x |

|

100 |

AL8 |

TYPEC1_USB20_VBUSDET |

- |

- |

TYPEC1_USB20_Insertion detection |

TYPEC1_USB20_VBUSDET |

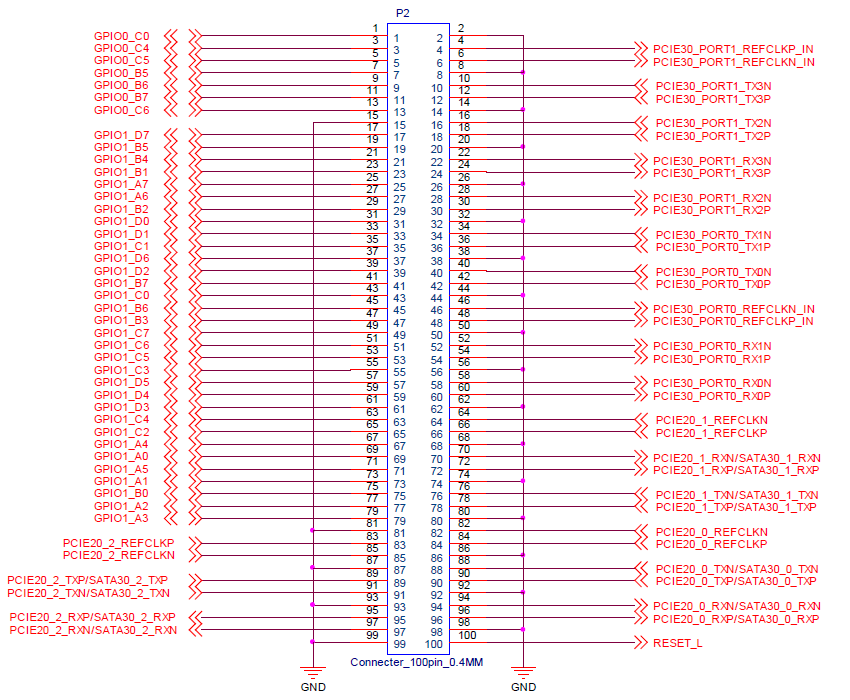

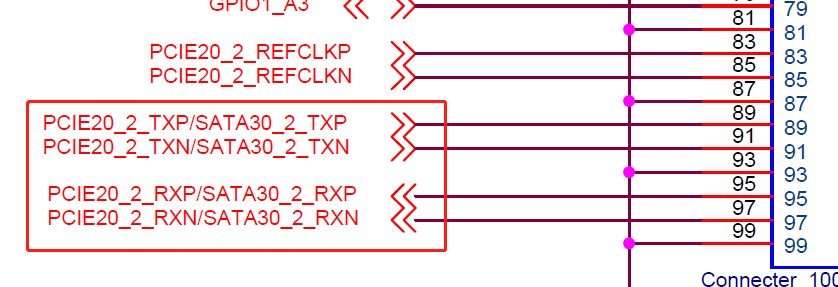

Table 3 Left _ DOWN (P2) Connector Interface (Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

T31 |

GPIO0_C0 |

GPIO0_C0_d |

3.3V |

I2C2 data |

I2C2_SDA_M0 |

3 |

R30 |

GPIO0_C4 |

GPIO0_C4_d |

3.3V |

PWM2 |

PWM2_M0 |

5 |

P30 |

GPIO0_C5 |

GPIO0_C5_u |

3.3V |

PWM4 |

PWM4_M0 |

7 |

P29 |

GPIO0_B5 |

GPIO0_B5_d |

3.3V |

UART2 sending |

UART2_TX_M0_DEBUG |

9 |

R29 |

GPIO0_B6 |

GPIO0_B6_d |

3.3V |

UART2 receiving |

UART2_RX_M0_DEBUG |

11 |

T28 |

GPIO0_B7 |

GPIO0_B7_d |

3.3V |

I2C2 clock |

I2C2_SCL_M0 |

13 |

T29 |

GPIO0_C6 |

GPIO0_C6_u |

3.3V |

PWM5 |

PWM5_M1 |

15 |

- |

GND |

- |

- |

Ground |

GND |

17 |

F25 |

GPIO1_D7 |

GPIO1_D7_u |

1.8V |

HDMI serial data |

HDMI_RX_SDA_M2 |

19 |

E25 |

GPIO1_B5 |

GPIO1_B5_u |

1.8V |

GMAC1 Interrupt |

GMAC1_INT |

21 |

E24 |

GPIO1_B4 |

GPIO1_B4_u |

1.8V |

GMAC1 Reset |

GMAC1_RESET |

23 |

D25 |

GPIO1_B1 |

GPIO1_B1_d |

1.8V |

BT Link activation |

BT_WAKE_HOST(1.8V) |

25 |

C25 |

GPIO1_A7 |

GPIO1_A7_u |

1.8V |

WLAN Link activation |

WLAN WAKE_1.8V_IN |

27 |

C24 |

GPIO1_A6 |

GPIO1_A6_d |

1.8V |

BT Link activation |

BT WAKE_1.8V_IN |

29 |

D26 |

GPIO1_B2 |

GPIO1_B2_d |

1.8V |

Headphone insertion detection |

HP_DET_L |

31 |

F26 |

GPIO1_D0 |

GPIO1_D0_d |

1.8V |

I2C7 clock |

I2C7_SCL_M0 |

33 |

F27 |

GPIO1_D1 |

GPIO1_D1_d |

1.8V |

I2C7 data |

I2C7_SDA_M0 |

35 |

G27 |

GPIO1_C1 |

GPIO1_C1_z |

1.8V |

I2C3 clock |

I2C3_SCL_M0 |

37 |

F24 |

GPIO1_D6 |

GPIO1_D6_u |

1.8V |

HDMI Serial clock |

HDMI_RX_SCL_M2 |

39 |

F28 |

GPIO1_D2 |

GPIO1_D2_d |

1.8V |

UART4 Sending data |

UART4_TX_M0 |

41 |

E27 |

GPIO1_B7 |

GPIO1_B7_u |

1.8V |

HDMI_RXCEC signal |

HDMI_RX_CEC_M2 |

43 |

G29 |

GPIO1_C0 |

GPIO1_C0_z |

1.8V |

I2C3 data |

I2C3_SDA_M0 |

45 |

E26 |

GPIO1_B6 |

GPIO1_B6_d |

1.8V |

HDMI Receiving link detection |

HDMI_RX_HPDOUT_M2 |

47 |

D27 |

GPIO1_B3 |

PIO1_B3_d |

1.8V |

TYPEC1 Interrupt |

TYPEC1_INT |

49 |

E29 |

GPIO1_C7 |

GPIO1_C7_d |

1.8V |

I2S Data output |

I2S0_SDO0 |

51 |

D29 |

GPIO1_C6 |

GPIO1_C6_d |

1.8V |

4G/5G Reset |

4G/5G RESET |

53 |

D30 |

GPIO1_C5 |

GPIO1_C5_d |

1.8V |

I2S Sending frame clock |

I2S0_LRCK_TX |

55 |

E31 |

GPIO1_C3 |

GPIO1_C3_d |

1.8V |

I2S bit clock |

I2S0_SCLK_TX |

57 |

G26 |

GPIO1_D5 |

GPIO1_D5_d |

1.8V |

HDMIIRX insertion detection |

HDMIIRX_DET_L |

59 |

D28 |

GPIO1_D4 |

GPIO1_D4_d |

1.8V |

I2S data input |

I2S0_SDI0 |

61 |

E28 |

GPIO1_D3 |

GPIO1_D3_d |

1.8V |

UART4 receiving data: |

UART4_RX_M0 |

63 |

E30 |

GPIO1_C4 |

GPIO1_C4_d |

1.8V |

4G/5G Reset |

4G/5G_RESET_1V8 |

65 |

F30 |

GPIO1_C2 |

GPIO1_C2__d |

1.8V |

I2S main clock |

I2S0_MCLK |

67 |

B25 |

GPIO1_A4 |

GPIO1_A4_d |

1.8V |

IIC interrupt |

IIC_GPIO_INT |

69 |

A24 |

GPIO1_A0 |

GPIO1_A0_d |

1.8V |

UART6 receiving data: |

UART6_RX_M1 |

71 |

B26 |

GPIO1_A5 |

GPIO1_A5_d |

1.8V |

HDMI Sending link detection |

HDMITX0_HPDIN_M0 |

73 |

A25 |

GPIO1_A1 |

GPIO1_A1_d |

1.8V |

UART6 Sending data |

UART6_TX_M1 |

75 |

C27 |

GPIO1_B0 |

GPIO1_B0_u |

1.8V |

TYPEC0 Interrupt |

TYPEC0_INT |

77 |

A26 |

GPIO1_A2 |

GPIO1_A2_d |

1.8V |

UART6 request sending |

UART6_RTSN_M1 |

79 |

A27 |

GPIO1_A3 |

GPIO1_A3_d |

1.8V |

UART6 clear sending |

UART6_CTSN_M1 |

81 |

- |

GND |

- |

- |

Ground |

GND |

83 |

G31 |

PCIE20_2_REFCLKP |

- |

- |

x |

|

85 |

G30 |

PCIE20_2_REFCLKN |

- |

- |

x |

|

87 |

- |

GND |

- |

- |

Ground |

GND |

89 |

H30 |

PCIE20_2_TXP/SATA30_2_TXP |

- |

- |

USB30_2 sending differential+ |

USB30_2_SSTX_P |

91 |

H29 |

PCIE20_2_TXN/SATA30_2_TXN |

- |

- |

USB30_2 sending differential- |

USB30_2_SSTX_N |

93 |

- |

GND |

- |

- |

Ground |

GND |

95 |

J31 |

PCIE20_2_RXP/SATA30_2_RXP |

- |

USB30_2 receiving differential+ |

USB30_2_SSRX_P |

|

97 |

J30 |

PCIE20_2_RXN/SATA30_2_RXN |

- |

- |

USB30_2 receiving differential- |

USB30_2_SSRX_N |

99 |

- |

GND |

- |

- |

Ground |

GND |

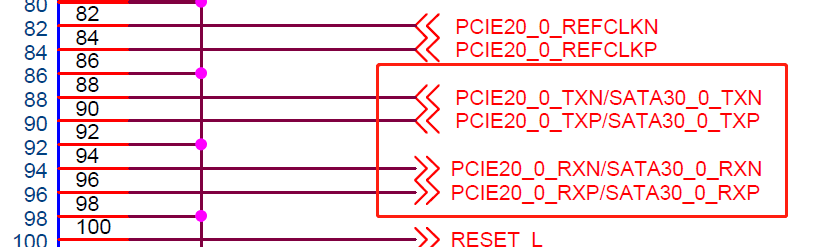

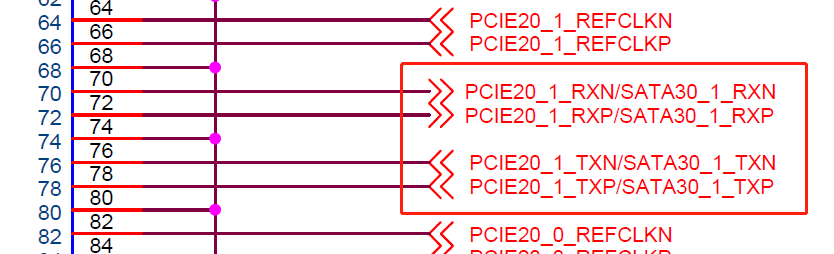

Table 4 Left _ DOWN (P2) Connector Interface (Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

A28 |

PCIE30_PORT1_REFCLKP_IN |

- |

- |

PCIE3.0 clock input+ |

PCIE30_PORT1_REFCLK_IN_P |

6 |

B28 |

PCIE30_PORT1_REFCLKN_IN |

- |

- |

PCIE3.0 clock input- |

PCIE30_PORT1_REFCLK_IN_N |

8 |

- |

GND |

- |

- |

Ground |

GND |

10 |

B29 |

PCIE30_PORT1_TX3N |

- |

- |

PCIE3.0 sending data 3- |

PCIE30_PORT1_TX3_N |

12 |

C29 |

PCIE30_PORT1_TX3P |

- |

- |

PCIE3.0 data sending 3+ |

PCIE30_PORT1_TX3_P |

14 |

- |

GND |

- |

- |

Ground |

GND |

16 |

A30 |

PCIE30_PORT1_TX2N |

- |

- |

PCIE3.0 sending data 2- |

PCIE30_PORT1_TX2_N |

18 |

B30 |

PCIE30_PORT1_TX2P |

- |

- |

PCIE3.0 data sending 2+ |

PCIE30_PORT1_TX2_P |

20 |

- |

GND |

- |

- |

Ground |

GND |

22 |

B31 |

PCIE30_PORT1_RX3N |

- |

- |

PCIE3.0 data receiving 3- |

PCIE30_PORT1_RX3_N |

24 |

C31 |

PCIE30_PORT1_RX3P |

- |

- |

PCIE3.0 data receiving 3+ |

PCIE30_PORT1_RX3_P |

26 |

- |

GND |

- |

- |

Ground |

GND |

28 |

A32 |

PCIE30_PORT1_RX2N |

- |

- |

PCIE3.0 data receiving- |

PCIE30_PORT1_RX2_N |

30 |

B32 |

PCIE30_PORT1_RX2P |

- |

- |

PCIE3.0 data receiving 2+ |

PCIE30_PORT1_RX2_P |

32 |

- |

GND |

- |

- |

Ground |

GND |

34 |

C34 |

PCIE30_PORT0_TX1N |

- |

- |

PCIE3.0 sending data 1- |

PCIE30_PORT0_TX1_N |

36 |

C33 |

PCIE30_PORT0_TX1P |

- |

- |

PCIE3.0 data sending 1+ |

PCIE30_PORT0_TX1_P |

38 |

- |

GND |

- |

- |

Ground |

GND |

40 |

D33 |

PCIE30_PORT0_TX0N |

- |

- |

PCIE3.0 sending data 0- |

PCIE30_PORT0_TX0_N |

42 |

D32 |

PCIE30_PORT0_TX0P |

- |

- |

PCIE3.0 data sending 0+ |

PCIE30_PORT0_TX0_P |

44 |

- |

GND |

- |

- |

Ground |

GND |

46 |

E34 |

PCIE30_PORT0_REFCLKN_IN |

- |

- |

PCIE3.0 clock input- |

PCIE30_PORT0_REFCLK_IN_N |

48 |

E33 |

PCIE30_PORT0_REFCLKP_IN |

- |

- |

PCIE3.0 clock input+ |

PCIE30_PORT0_REFCLK_IN_P |

50 |

- |

GND |

- |

- |

Ground |

GND |

52 |

F33 |

PCIE30_PORT0_RX1N |

- |

- |

PCIE3.0 data receiving 1- |

PCIE30_PORT0_RX1_N |

54 |

F32 |

PCIE30_PORT0_RX1P |

- |

- |

PCIE3.0 data receiving 1+ |

PCIE30_PORT0_RX1_P |

56 |

- |

GND |

- |

- |

Ground |

GND |

58 |

G34 |

PCIE30_PORT0_RX0N |

- |

- |

PCIE3.0 data receiving 0- |

PCIE30_PORT0_RX0_N |

60 |

G33 |

PCIE30_PORT0_RX0P |

- |

- |

PCIE3.0 data receiving 0+ |

PCIE30_PORT0_RX0_P |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

H33 |

PCIE20_1_REFCLKN |

- |

- |

PCIE2.0 clock input- |

PCIE20_1_REFCLK_N |

66 |

H32 |

PCIE20_1_REFCLKP |

- |

- |

PCIE2.0 clock input+ |

PCIE20_1_REFCLK_P |

68 |

- |

GND |

- |

- |

Ground |

GND |

70 |

J34 |

PCIE20_1_RXN/SATA30_1_RXN |

- |

- |

PCIE2.0 data receiving- |

PCIE20_1_RX_N |

72 |

J33 |

PCIE20_1_RXP/SATA30_1_RXP |

- |

- |

PCIE2.0 data receiving+ |

PCIE20_1_RX_P |

74 |

- |

GND |

- |

- |

Ground |

GND |

76 |

K34 |

PCIE20_1_TXN/SATA30_1_TXN |

- |

- |

PCIE2.0 data sending- |

PCIE20_1_TX_N |

78 |

K33 |

PCIE20_1_TXP/SATA30_1_TXP |

- |

- |

PCIE2.0 data sending+ |

PCIE20_1_TX_P |

80 |

- |

GND |

- |

- |

Ground |

GND |

82 |

L33 |

PCIE20_0_REFCLKN |

- |

- |

PCIE2.0 clock input- |

PCIE20_0_REFCLK_N |

84 |

L32 |

PCIE20_0_REFCLKP |

- |

- |

PCIE2.0 clock input+ |

PCIE20_0_REFCLK_P |

86 |

- |

GND |

- |

- |

Ground |

GND |

88 |

M33 |

PCIE20_0_TXN/SATA30_0_TXN |

- |

- |

PCIE2.0 data sending- |

PCIE20_0_TX_N |

90 |

M34 |

PCIE20_0_TXP/SATA30_0_TXP |

- |

- |

PCIE2.0 data sending+ |

PCIE20_0_TX_P |

92 |

- |

GND |

- |

- |

Ground |

GND |

94 |

N34 |

PCIE20_0_RXN/SATA30_0_RXN |

- |

- |

PCIE2.0 data receiving- |

PCIE20_0_RX_N |

96 |

N33 |

PCIE20_0_RXP/SATA30_0_RXP |

- |

- |

PCIE2.0 data receiving+ |

PCIE20_0_RX_P |

98 |

- |

GND |

- |

- |

Ground |

GND |

100 |

RESET_L |

- |

- |

Reset |

RESET_L |

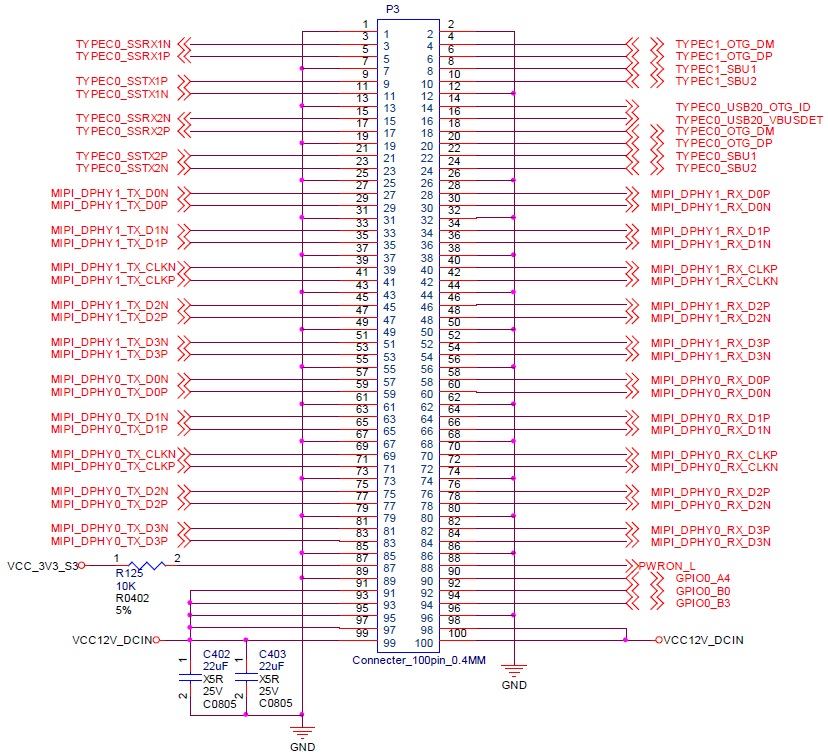

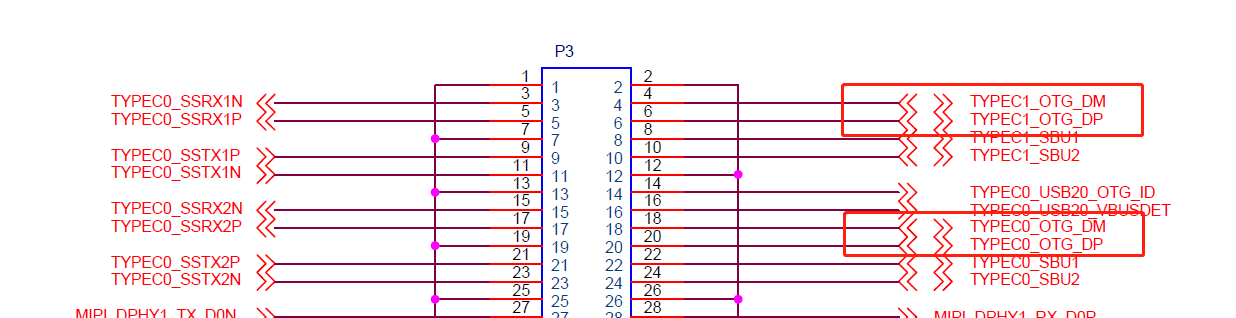

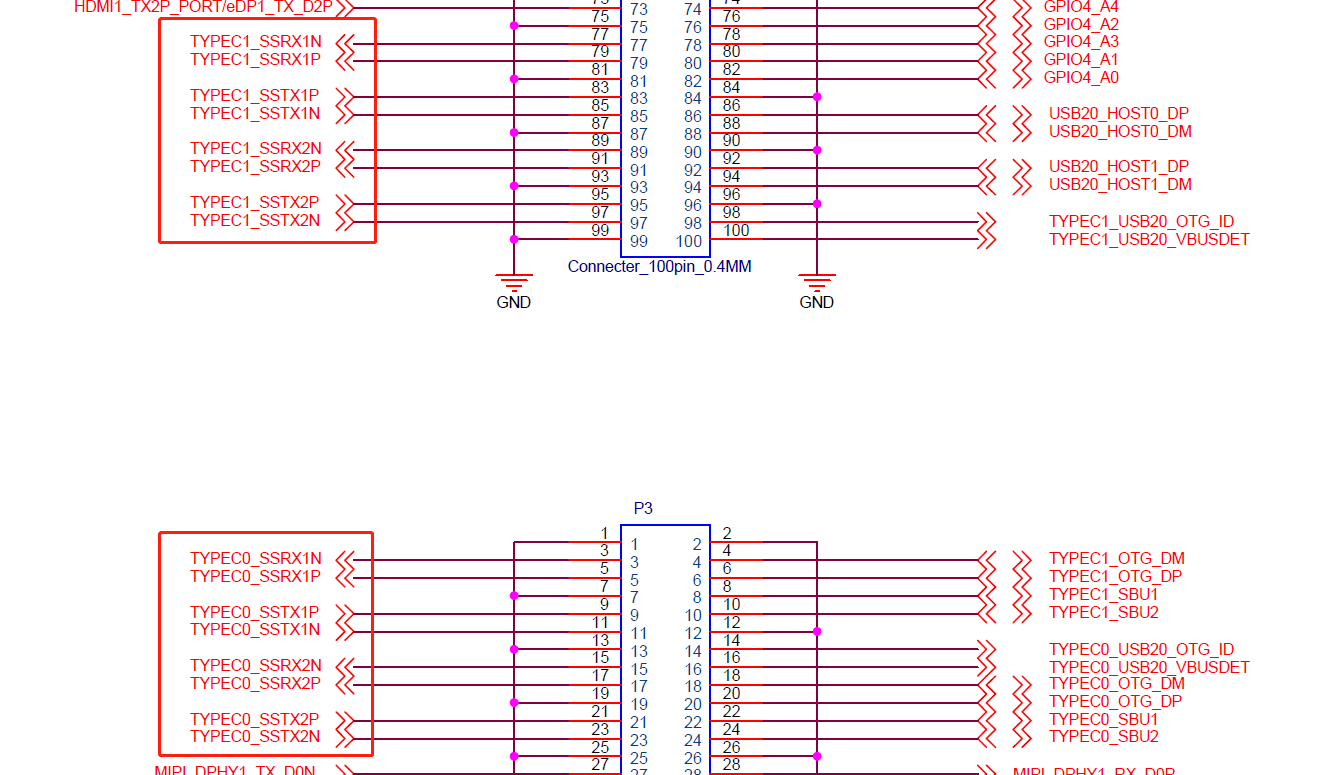

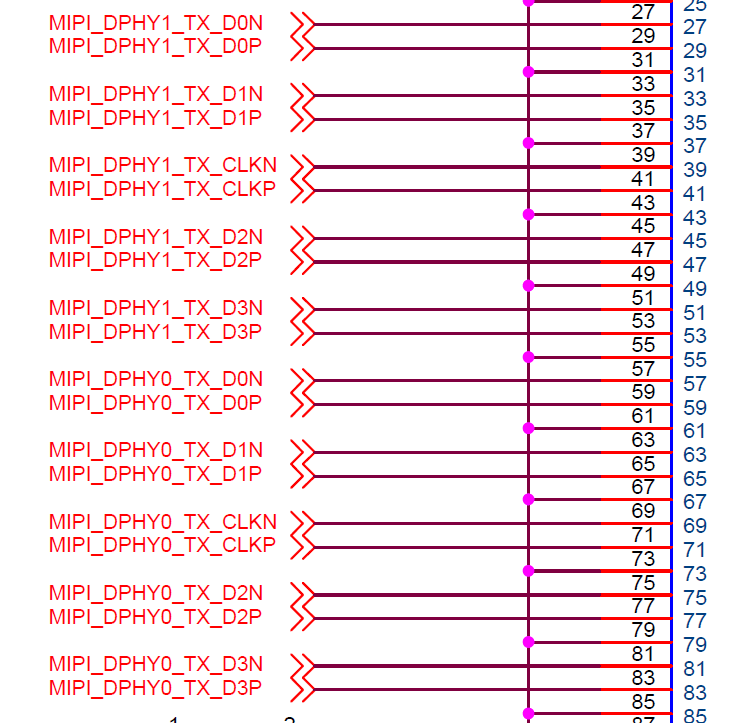

Table 5 Right_UP(P3) Connector Interface(Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

- |

GND |

- |

- |

Ground |

GND |

3 |

AP13 |

TYPEC0_SSRX1N |

- |

- |

TYPEC0 Receiving differential signals1- |

TYPEC0_SSRX1_N |

5 |

AN13 |

TYPEC0_SSRX1P |

- |

- |

TYPEC0 Receiving differential signals 1+ |

TYPEC0_SSRX1_P |

7 |

- |

GND |

- |

- |

Ground |

GND |

9 |

AP14 |

TYPEC0_SSTX1P |

- |

- |

TYPEC0 Sending differential signals 1+ |

TYPEC0_SSTX1_P |

11 |

AN14 |

TYPEC0_SSTX1N |

- |

- |

TYPEC0 Sending differential signals 1- |

TYPEC0_SSTX1_N |

13 |

- |

GND |

- |

- |

Ground |

GND |

15 |

AP15 |

TYPEC0_SSRX2N |

- |

- |

TYPEC0 Receiving differential signals2- |

TYPEC0_SSRX2_N |

17 |

AN15 |

TYPEC0_SSRX2P |

- |

- |

TYPEC0 Receiving differential signals2+ |

TYPEC0_SSRX2_P |

19 |

- |

GND |

- |

- |

Ground |

GND |

21 |

AP16 |

TYPEC0_SSTX2P |

- |

- |

TYPEC0 Sending differential signals2+ |

TYPEC0_SSTX2_P |

23 |

AN16 |

TYPEC0_SSTX2N |

- |

- |

TYPEC0 Sending differential signals2- |

TYPEC0_SSTX2_N |

25 |

- |

GND |

- |

- |

Ground |

GND |

27 |

AP18 |

MIPI_DPHY1_TX_D0N |

- |

- |

MIPI_DPHY 1 data sending 0- |

MIPI_DPHY1_TXD0_N |

29 |

AN18 |

MIPI_DPHY1_TX_D0P |

- |

- |

MIPI_DPHY 1 data sending 0+ |

MIPI_DPHY1_TXD0_P |

31 |

- |

GND |

- |

- |

Ground |

GND |

33 |

AP19 |

MIPI_DPHY1_TX_D1N |

- |

- |

MIPI_DPHY 1 data sending 1- |

MIPI_DPHY1_TXD1_N |

35 |

AN19 |

MIPI_DPHY1_TX_D1P |

- |

- |

MIPI_DPHY 1 data sending 1+ |

MIPI_DPHY1_TXD1_P |

37 |

- |

GND |

- |

- |

Ground |

GND |

39 |

AP20 |

MIPI_DPHY1_TX_CLKN |

- |

- |

MIPI_DPHY 1 clock sending- |

MIPI_DPHY1_TXCLK_N |

41 |

AN20 |

MIPI_DPHY1_TX_CLKP |

- |

- |

MIPI_DPHY 1 clock sending+ |

MIPI_DPHY1_TXCLK_P |

43 |

GND |

- |

- |

Ground |

GND |

|

45 |

AP21 |

MIPI_DPHY1_TX_D2N |

- |

- |

MIPI_DPHY 1 data sending 2- |

MIPI_DPHY1_TXD2_N |

47 |

AN21 |

MIPI_DPHY1_TX_D2P |

- |

- |

MIPI_DPHY 1 data sending 2+ |

MIPI_DPHY1_TXD2_P |

49 |

- |

GND |

- |

- |

Ground |

GND |

51 |

AP22 |

MIPI_DPHY1_TX_D3N |

- |

- |

MIPI_DPHY 1 data sending 3- |

MIPI_DPHY1_TXD3_N |

53 |

AN22 |

MIPI_DPHY1_TX_D3P |

- |

- |

MIPI_DPHY 1 data sending 3+ |

MIPI_DPHY1_TXD3_P |

55 |

- |

GND |

- |

- |

Ground |

GND |

57 |

AP24 |

MIPI_DPHY0_TX_D0N |

- |

- |

MIPI_DPHY 0 data sending 0- |

MIPI_DPHY0_TXD0_N |

59 |

AN24 |

MIPI_DPHY0_TX_D0P |

- |

- |

MIPI_DPHY 0 data sending 0+ |

MIPI_DPHY0_TXD0_P |

61 |

- |

GND |

- |

- |

Ground |

GND |

63 |

AP25 |

MIPI_DPHY0_TX_D1N |

- |

- |

MIPI_DPHY 0 data sending 1- |

MIPI_DPHY0_TXD1_N |

65 |

AN25 |

MIPI_DPHY0_TX_D1P |

- |

- |

MIPI_DPHY 0 data sending 1+ |

MIPI_DPHY0_TXD1_P |

67 |

- |

GND |

- |

- |

Ground |

GND |

69 |

AP26 |

MIPI_DPHY0_TX_CLKN |

- |

- |

MIPI_DPHY 0 clock sending- |

MIPI_DPHY0_TXCLK_N |

71 |

AN26 |

MIPI_DPHY0_TX_CLKP |

- |

- |

MIPI_DPHY 0 clock sending+ |

MIPI_DPHY0_TXCLK_P |

73 |

- |

GND |

- |

- |

Ground |

GND |

75 |

AP27 |

MIPI_DPHY0_TX_D2N |

- |

- |

MIPI_DPHY 0 data sending 2- |

MIPI_DPHY0_TXD2_N |

77 |

AN27 |

MIPI_DPHY0_TX_D2P |

- |

- |

MIPI_DPHY 0 data sending 2+ |

MIPI_DPHY0_TXD2_P |

79 |

- |

GND |

- |

- |

Ground |

GND |

81 |

AP28 |

MIPI_DPHY0_TX_D3N |

- |

- |

MIPI_DPHY 0 data sending 3- |

MIPI_DPHY0_TXD3_N |

83 |

AN28 |

MIPI_DPHY0_TX_D3P |

- |

- |

MIPI_DPHY 0 data sending 3+ |

MIPI_DPHY0_TXD3_P |

85 |

- |

GND |

- |

- |

Ground |

GND |

87 |

CARRIER_BOARD_EN |

- |

- |

CARRIER enable |

CARRIER_BOARD_EN |

|

89 |

- |

GND |

- |

- |

Ground |

GND |

91 |

VCC_DCIN |

- |

- |

5V-12V power input |

VCC_DCIN |

|

93 |

VCC_DCIN |

- |

- |

5V-12V power input |

VCC_DCIN |

|

95 |

VCC_DCIN |

- |

- |

5V-12V power input |

VCC_DCIN |

|

97 |

VCC_DCIN |

- |

- |

5V-12V power input |

VCC_DCIN |

|

99 |

VCC_DCIN |

- |

- |

5V-12V power input |

VCC_DCIN |

Table 6 Right_UP(P3) Connector Interface(Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

AL9 |

TYPEC1_OTG_DM |

- |

- |

TYPEC1 data- |

TYPEC1_OTG_D_N |

6 |

AK9 |

TYPEC1_OTG_DP |

- |

- |

TYPEC1 data+ |

TYPEC1_OTG_D_P |

8 |

AL10 |

TYPEC1_SBU1 |

- |

- |

TYPEC1_SBU1 signal |

TYPEC1_SBU1 |

10 |

AM10 |

TYPEC1_SBU2 |

- |

- |

TYPEC1_SBU2 signal |

TYPEC1_SBU2 |

12 |

- |

GND |

- |

- |

Ground |

GND |

14 |

AL14 |

TYPEC0_USB20_OTG_ID |

- |

- |

X |

|

16 |

AM14 |

TYPEC0_USB20_VBUSDET |

- |

- |

TYPEC0_USB20 insertion detection |

TYPEC0_USB20_VBUSDET |

18 |

AM12 |

TYPEC0_OTG_DM |

- |

- |

TYPEC0 data- |

TYPEC0_OTG_D_N |

20 |

AL12 |

TYPEC0_OTG_DP |

- |

- |

TYPEC0 data+ |

TYPEC0_OTG_D_P |

22 |

AL15 |

TYPEC0_SBU1 |

- |

- |

TYPEC0_SBU1 signal |

TYPEC0_SBU1 |

24 |

AM15 |

TYPEC0_SBU2 |

- |

- |

TYPEC0_SBU2 signal |

TYPEC0_SBU2 |

26 |

- |

GND |

- |

- |

Ground |

GND |

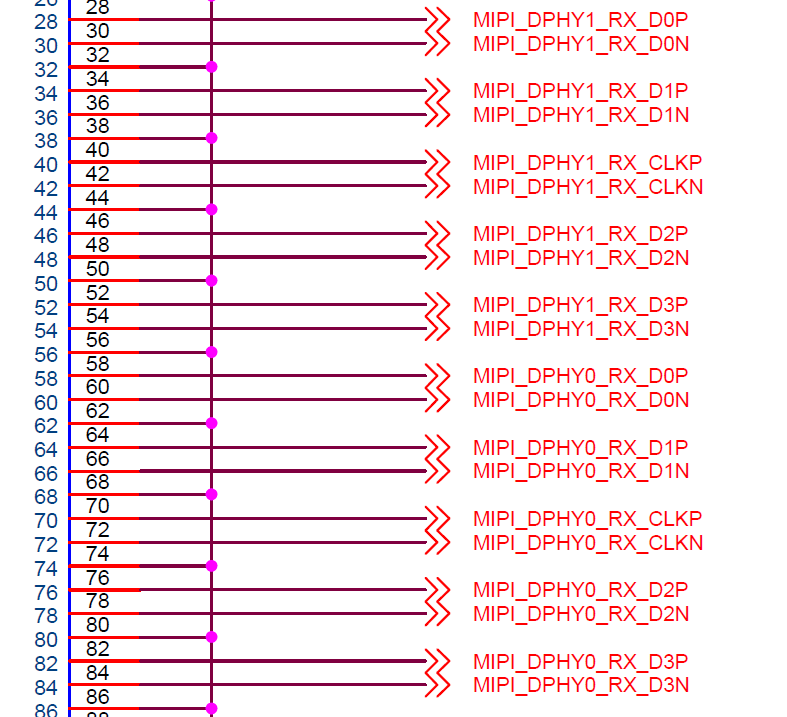

28 |

AK18 |

MIPI_DPHY1_RX_D0P |

- |

- |

MIPI_DPHY 1 data receiving 0+ |

MIPI_DPHY1_RXD0_P |

30 |

AL18 |

MIPI_DPHY1_RX_D0N |

- |

- |

MIPI_DPHY 1 data receiving 0- |

MIPI_DPHY1_RXD0_N |

32 |

- |

GND |

- |

- |

Ground |

GND |

34 |

AK19 |

MIPI_DPHY1_RX_D1P |

- |

- |

MIPI_DPHY 1 data receiving 1+ |

MIPI_DPHY1_RXD1_P |

36 |

AL19 |

MIPI_DPHY1_RX_D1N |

- |

- |

MIPI_DPHY 1 data receiving 1- |

MIPI_DPHY1_RXD1_N |

38 |

- |

GND |

- |

- |

Ground |

GND |

40 |

AK20 |

MIPI_DPHY1_RX_CLKP |

- |

- |

MIPI_DPHY 1 clock receiving+ |

MIPI_DPHY1_RXCLK_P |

42 |

AL20 |

MIPI_DPHY1_RX_CLKN |

- |

- |

MIPI_DPHY 1 clock receiving- |

MIPI_DPHY1_RXCLK_N |

44 |

- |

GND |

- |

- |

Ground |

GND |

46 |

AK21 |

MIPI_DPHY1_RX_D2P |

- |

- |

MIPI_DPHY 1 data receiving 2+ |

MIPI_DPHY1_RXD2_P |

48 |

AL21 |

MIPI_DPHY1_RX_D2N |

- |

- |

MIPI_DPHY 1 data receiving 2- |

MIPI_DPHY1_RXD2_N |

50 |

- |

GND |

- |

- |

Ground |

GND |

52 |

AK22 |

MIPI_DPHY1_RX_D3P |

- |

- |

MIPI_DPHY 1 data receiving 3+ |

MIPI_DPHY1_RXD3_P |

54 |

AL22 |

MIPI_DPHY1_RX_D3N |

- |

- |

MIPI_DPHY 1 data receiving 3- |

MIPI_DPHY1_RXD3_N |

56 |

- |

GND |

- |

- |

Ground |

GND |

58 |

AN29 |

MIPI_DPHY0_RX_D0P |

- |

- |

MIPI_DPHY 0 data receIving 0+ |

MIPI_DPHY0_RXD0_P |

60 |

AP29 |

MIPI_DPHY0_RX_D0N |

- |

- |

MIPI_DPHY 0 data receiving 0- |

MIPI_DPHY0_RXD0_N |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

AN30 |

MIPI_DPHY0_RX_D1P |

- |

- |

MIPI_DPHY 0 data receiving 1+ |

MIPI_DPHY0_RXD1_P |

66 |

AP30 |

MIPI_DPHY0_RX_D1N |

- |

- |

MIPI_DPHY 0 data receiving 1- |

MIPI_DPHY0_RXD1_N |

68 |

GND |

- |

- |

Ground |

GND |

|

70 |

AN32 |

MIPI_DPHY0_RX_CLKP |

- |

- |

MIPI_DPHY 0 clock receiving+ |

MIPI_DPHY0_RXCLK_P |

72 |

AP31 |

MIPI_DPHY0_RX_CLKN |

- |

- |

MIPI_DPHY 0 clock receiving- |

MIPI_DPHY0_RXCLK_N |

74 |

GND |

- |

- |

Ground |

GND |

|

76 |

AN33 |

MIPI_DPHY0_RX_D2P |

- |

- |

MIPI_DPHY 0 data receiving 2+ |

MIPI_DPHY0_RXD2_P |

78 |

AP32 |

MIPI_DPHY0_RX_D2N |

- |

- |

MIPI_DPHY 0 data receiving 2- |

MIPI_DPHY0_RXD2_N |

80 |

- |

GND |

- |

- |

Ground |

GND |

82 |

AN34 |

MIPI_DPHY0_RX_D3P |

- |

- |

MIPI_DPHY 0 data receiving 3+ |

MIPI_DPHY0_RXD3_P |

84 |

AP33 |

MIPI_DPHY0_RX_D3N |

- |

- |

MIPI_DPHY 0 data receiving 3- |

MIPI_DPHY0_RXD3_N |

86 |

- |

GND |

- |

- |

Ground |

GND |

88 |

PWRON_L |

- |

- |

Power on control |

PWRON_L |

|

90 |

P31 |

GPIO0_A4 |

GPIO0_A4_u |

1.8V |

SDMMC card detection signal |

SDMMC_DET_L |

92 |

L30 |

GPIO0_B0 |

GPIO0_B0_z |

1.8V |

GMAC0 Reset |

GMAC0_RESET |

94 |

L29 |

GPIO0_B3 |

GPIO0_B3_z |

1.8V |

GMAC0 Interrupt |

GMAC0_INT |

96 |

- |

GND |

- |

- |

Ground |

GND |

98 |

VCC_DCIN |

- |

- |

5V-13V power input |

VCC_DCIN |

|

100 |

VCC_DCIN |

- |

- |

5V-13V power input |

VCC_DCIN |

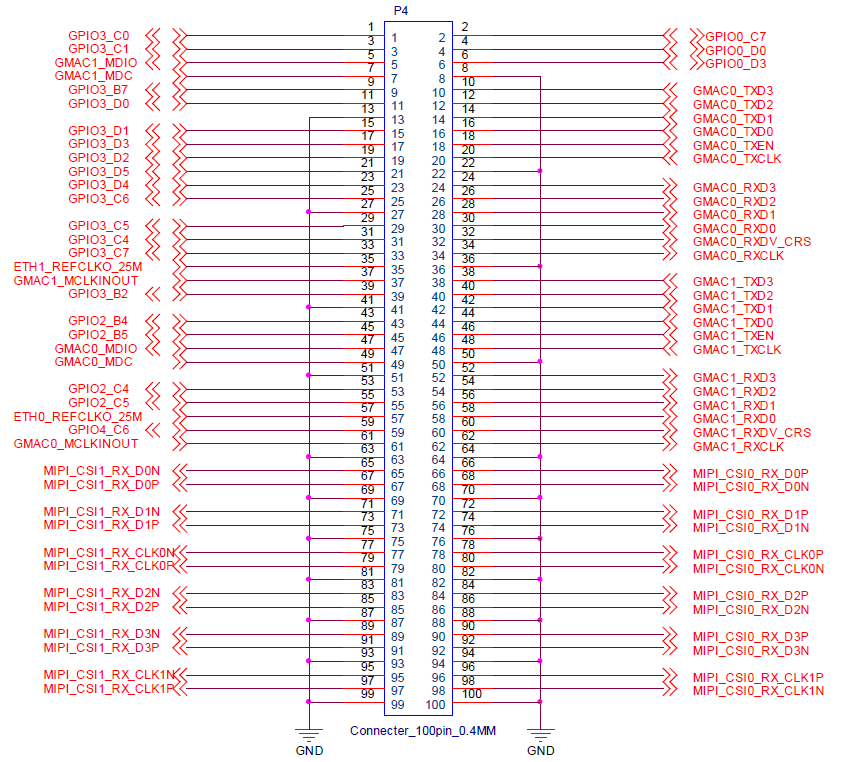

Table7 LEFT_UP(P4) Connector Interface(Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

Y29 |

GPIO3_C0 |

GPIO3_C0_d |

3.3V |

MIPI_DSI1 Interrupt |

MIPI_DSI1_INT |

3 |

Y27 |

GPIO3_C1 |

GPIO3_C1_d |

3.3V |

EDP_LED enable |

EDP_LED_EN |

5 |

Y30 |

GMAC1_MDIO |

GPIO3_C3_d |

3.3V |

GMAC1 Serial Management Data |

GMAC1_MDIO |

7 |

Y31 |

GMAC1_MDC |

GPIO3_C2_d |

3.3V |

GMAC1 Serial Management Clock |

GMAC1_MDC |

9 |

AA28 |

GPIO3_B7 |

GPIO3_B7_d |

3.3V |

MIPI_DSI1 Reset |

MIPI_DSI1_RESET |

11 |

AH24 |

GPIO3_D0 |

GPIO3_D0_u |

3.3V |

PCIE20 link activation signal |

PCIE20X1_2_WAKEN_M0 |

13 |

- |

GND |

- |

- |

Ground |

GND |

15 |

AG23 |

GPIO3_D1 |

GPIO3_D1_d |

3.3V |

PCIE20 Reset |

PCIE20X1_2_PERSTN_M0 |

17 |

AG24 |

GPIO3_D3 |

GPIO3_D3_d |

3.3V |

MIPI_DSI2 interrupt signal |

MIPI_DSI2_INT |

19 |

AG25 |

GPIO3_D2 |

GPIO3_D2_d |

3.3V |

MIPI_DSI2 reset signal |

MIPI_DSI2_RESET |

21 |

AB28 |

GPIO3_D5 |

GPIO3_D5_d |

3.3V |

UART9 sending |

UART9_TX_M2 |

23 |

AA27 |

GPIO3_D4 |

GPIO3_D4_d |

3.3V |

UART9 receiving |

UART9_RX_M2 |

25 |

AG26 |

GPIO3_C6 |

GPIO3_C6_u |

3.3V |

MIPI_DSI2 enable signal |

MIPI_DSI2_EN |

27 |

- |

GND |

- |

- |

Ground |

GND |

29 |

AH25 |

GPIO3_C5 |

GPIO3_C5_u |

3.3V |

CAN2 data sending |

CAN2_TX_M0 |

31 |

AH26 |

GPIO3_C4 |

GPIO3_C4_u |

3.3V |

CAN2 data receiving |

CAN2_RX_M0 |

33 |

AJ24 |

GPIO3_C7 |

GPIO3_C7_u |

3.3V |

PCIE20X1_2_CLKREQN signal |

PCIE20X1_2_CLKREQN_M0 |

35 |

AH27 |

ETH1_REFCLKO_25M |

GPIO3_A6_d |

3.3V |

PHY 25MHz reference clock output |

ETH1_REFCLKO_25M |

37 |

AE29 |

GMAC1_MCLKINOUT |

GPIO3_B6_d |

3.3V |

PHY 125MHz Sync Clock Input |

GMAC1_MCLKINOUT |

39 |

AE28 |

GPIO3_B2 |

GPIO3_B2_d |

3.3V |

MIPI_DSI1 enable signal |

MIPI_DSI1_EN |

41 |

- |

GND |

- |

- |

Ground |

GND |

43 |

AB31 |

GPIO2_B4 |

GPIO2_B4_u |

1.8V |

I2C4 data |

I2C4_SDA_M1 |

45 |

AB30 |

GPIO2_B5 |

GPIO2_B5_u |

1.8V |

I2C4 clock |

I2C4_SCL_M1 |

47 |

AB33 |

GMAC0_MDIO |

GPIO4_C5_d |

1.8V |

GMAC0 Serial Management Data |

GMAC0_MDIO |

49 |

AB34 |

GMAC0_MDC |

GMAC0_MDC |

1.8V |

GMAC0 Serial Management Clock |

GMAC0_MDC |

51 |

- |

GND |

- |

- |

Ground |

GND |

53 |

AC30 |

GPIO2_C4 |

GPIO2_C4_d |

1.8V |

eDP plug detection |

EDP_HPD |

55 |

AE30 |

GPIO2_C5 |

GPIO2_C5_d |

1.8V |

PCIE20X1 insertion detection |

PCIE20X1_PRSNT_L_1V8 |

57 |

AD30 |

ETH0_REFCLKO_25M |

GPIO2_C3_d |

1.8V |

PHY 25MHz reference clock output |

ETH0_REFCLKO_25M |

59 |

AF33 |

GPIO4_C6 |

GPIO4_C6_d |

1.8V |

PCIe30x4 Hot-plug detection |

PCIe30x4_PRSNT_L_1V8 |

61 |

AF34 |

GMAC0_MCLKINOUT |

GPIO4_C3_d |

1.8V |

PHY 125MHz Sync Clock Input |

GMAC0_MCLKINOUT |

63 |

- |

GND |

- |

- |

Ground |

GND |

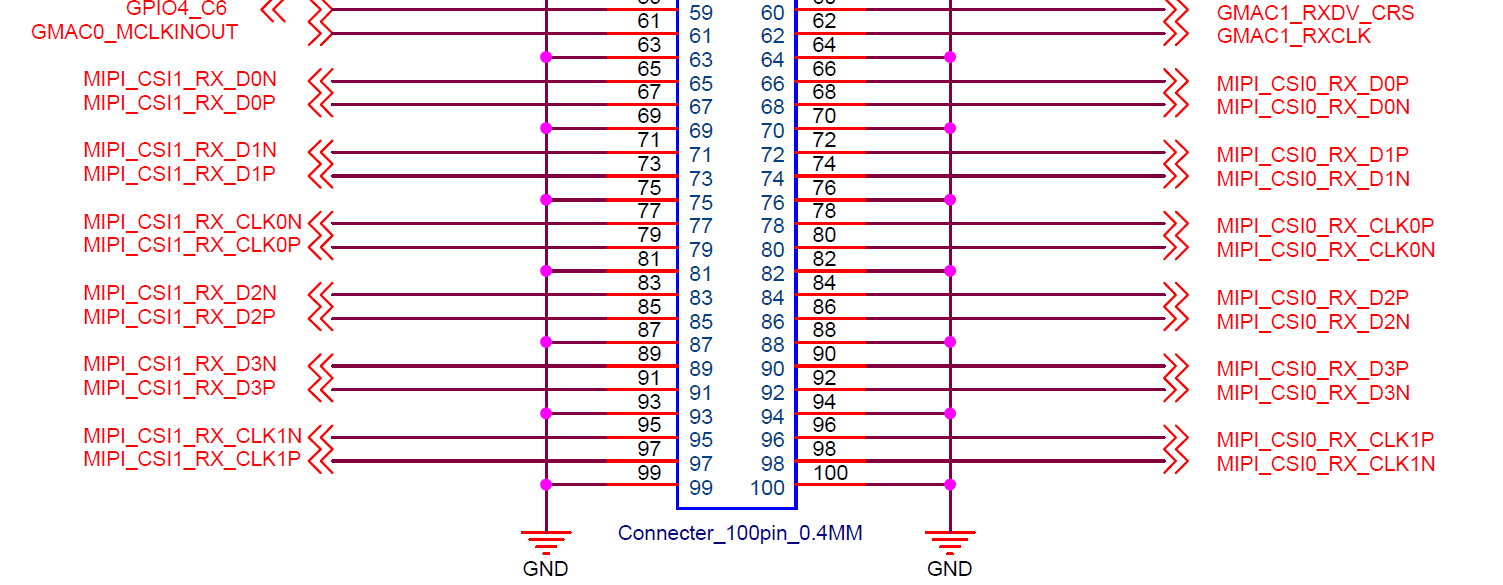

65 |

AG32 |

MIPI_CSI1_RX_D0N |

- |

- |

CSI1 data receiving 0- |

MIPI_CSI1_RXD0_N |

67 |

AG31 |

MIPI_CSI1_RX_D0P |

- |

- |

CSI1 data receiving 0+ |

MIPI_CSI1_RXD0_P |

69 |

- |

GND |

- |

- |

Ground |

GND |

71 |

AH32 |

MIPI_CSI1_RX_D1N |

- |

- |

CSI1 data receiving 1- |

MIPI_CSI1_RXD1_N |

73 |

AH31 |

MIPI_CSI1_RX_D1P |

- |

- |

CSI1 data receiving 1+ |

MIPI_CSI1_RXD1_P |

75 |

- |

GND |

- |

- |

Ground |

GND |

77 |

AJ32 |

MIPI_CSI1_RX_CLK0N |

- |

CSI1 clock 0- |

MIPI_CSI1_RXCLK0_N |

|

79 |

AJ31 |

MIPI_CSI1_RX_CLK0P |

- |

- |

CSI1 clock 0+ |

MIPI_CSI1_RXCLK0_P |

81 |

- |

GND |

- |

- |

Ground |

GND |

83 |

AK32 |

MIPI_CSI1_RX_D2N |

- |

- |

CSI1 data receiving 2- |

MIPI_CSI1_RXD2_N |

85 |

AK31 |

MIPI_CSI1_RX_D2P |

- |

- |

CSI1 data receiving 2+ |

MIPI_CSI1_RXD2_P |

87 |

- |

GND |

- |

- |

Ground |

GND |

89 |

AL32 |

MIPI_CSI1_RX_D3N |

- |

- |

CSI1 data receiving 3- |

MIPI_CSI1_RXD3_N |

91 |

AL31 |

MIPI_CSI1_RX_D3P |

- |

- |

CSI1 data receiving 3+ |

MIPI_CSI1_RXD3_P |

93 |

- |

GND |

- |

- |

Ground |

GND |

95 |

AM32 |

MIPI_CSI1_RX_CLK1N |

- |

- |

CSI1 clock 1- |

MIPI_CSI1_RXCLK1_N |

97 |

AM31 |

MIPI_CSI1_RX_CLK1P |

- |

- |

CSI1 clock 1+ |

MIPI_CSI1_RXCLK1_P |

99 |

- |

GND |

- |

- |

Ground |

GND |

Table8 LEFT_UP(P4) Connector Interface(Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

V31 |

GPIO0_C7 |

GPIO0_C7_d |

3.3V |

PWM6 |

PWM6_M0 |

4 |

W31 |

GPIO0_D0 |

GPIO0_D0_d |

3.3V |

TYPEC0 enable |

TYPEC0_PWREN |

6 |

U33 |

GPIO0_D3 |

GPIO0_D3_u |

3.3V |

TYPEC1 enable |

TYPEC1_PWREN |

8 |

- |

GND |

- |

- |

Ground |

GND |

10 |

AC34 |

GMAC0_TXD3 |

GPIO2_B2_u |

1.8V |

GMAC0 data sending 3 |

GMAC0_TXD3 |

12 |

AC33 |

GMAC0_TXD2 |

GPIO2_B1_u |

1.8V |

GMAC0 data sending 2 |

GMAC0_TXD2 |

14 |

AD34 |

GMAC0_TXD1 |

GPIO2_B7_d |

1.8V |

GMAC0 data sending 1 |

GMAC0_TXD1 |

16 |

AD33 |

GMAC0_TXD0 |

GPIO2_B6_d |

1.8V |

GMAC0 data sending 0 |

GMAC0_TXD0 |

18 |

AE34 |

GMAC0_TXEN |

GPIO2_C0_d |

1.8V |

GMAC0 sending control |

GMAC0_TXEN |

20 |

AE33 |

GMAC0_TXCLK |

GPIO2_B3_d |

1.8V |

GMAC0 clock sending |

GMAC0_TXCLK |

22 |

- |

GND |

- |

- |

Ground |

GND |

24 |

AC31 |

GMAC0_RXD3 |

GPIO2_A7_u |

1.8V |

GMAC0 data receiving 3 |

GMAC0_RXD3 |

26 |

AC32 |

GMAC0_RXD2 |

GPIO2_A6_u |

1.8V |

GMAC0 data receiving 2 |

GMAC0_RXD2 |

28 |

AD31 |

GMAC0_RXD1 |

GPIO2_C2_d |

1.8V |

GMAC0 data receiving 1 |

GMAC0_RXD1 |

30 |

AD32 |

GMAC0_RXD0 |

GPIO2_C1_d |

1.8V |

GMAC0 data receiving 0 |

GMAC0_RXD0 |

32 |

AE31 |

GMAC0_RXDV_CRS |

GPIO4_C2_d |

1.8V |

GMAC0 receiving control |

GMAC0_RXDV_CRS |

34 |

AE32 |

GMAC0_RXCLK |

GPIO2_B0_u |

1.8V |

GMAC0 clock receiving |

GMAC0_RXCLK |

36 |

- |

GND |

- |

- |

Ground |

GND |

38 |

AA30 |

GMAC1_TXD3 |

GPIO3_A1_u |

3.3V |

GMAC1 data sending 3 |

GMAC1_TXD3 |

40 |

AA29 |

GMAC1_TXD2 |

GPIO3_A0_u |

3.3V |

GMAC1 data sending 2 |

GMAC1_TXD2 |

42 |

AC29 |

GMAC1_TXD1 |

GPIO3_B4_u |

3.3V |

GMAC1 data sending 1 |

GMAC1_TXD1 |

44 |

AC28 |

GMAC1_TXD0 |

GPIO3_B3_u |

3.3V |

GMAC1 data sending 0 |

GMAC1_TXD0 |

46 |

AD29 |

GMAC1_TXEN |

GPIO3_B5_u |

3.3V |

GMAC1 sending control |

GMAC1_TXEN |

48 |

AD28 |

GMAC1_TXCLK |

GPIO3_A4_d |

3.3V |

GMAC1 clock sending |

GMAC1_TXCLK |

50 |

- |

GND |

- |

- |

Ground |

GND |

52 |

AE27 |

GMAC1_RXD3 |

GPIO3_A3_u |

3.3V |

GMAC1 data receiving 3 |

GMAC1_RXD3 |

54 |

AD27 |

GMAC1_RXD2 |

GPIO3_A2_u |

3.3V |

GMAC1 data receiving 2 |

GMAC1_RXD2 |

56 |

AG28 |

GMAC1_RXD1 |

GPIO3_A2_u |

3.3V |

GMAC1 data receiving 1 |

GMAC1_RXD1 |

58 |

AG29 |

GMAC1_RXD0 |

GPIO3_A7_u |

3.3V |

GMAC1 data receiving 0 |

GMAC1_RXD0 |

60 |

AH29 |

GMAC1_RXDV_CRS |

GPIO3_B1_d |

3.3V |

GMAC1 receiving control |

GMAC1_RXDV_CRS |

62 |

AH30 |

GMAC1_RXCLK |

GPIO3_A5_d |

3.3V |

GMAC1 clock receiving |

GMAC1_RXCLK |

64 |

- |

GND |

- |

- |

Ground |

GND |

66 |

AG33 |

MIPI_CSI0_RX_D0P |

- |

- |

CSI0 data receiving 0+ |

MIPI_CSI0_RXD0_P |

68 |

AG34 |

MIPI_CSI0_RX_D0N |

- |

- |

CSI0 data receiving 0- |

MIPI_CSI0_RXD0_N |

70 |

- |

GND |

- |

- |

Ground |

GND |

72 |

AH33 |

MIPI_CSI0_RX_D1P |

- |

- |

CSI0 data receiving 1+ |

MIPI_CSI0_RXD1_P |

74 |

AH34 |

MIPI_CSI0_RX_D1N |

- |

- |

CSI0 data receiving 1- |

MIPI_CSI0_RXD1_N |

76 |

- |

GND |

- |

- |

Ground |

GND |

78 |

AJ33 |

MIPI_CSI0_RX_CLK0P |

- |

- |

CSI0 clock 0+ |

MIPI_CSI0_RXCLK0_P |

80 |

AJ34 |

MIPI_CSI0_RX_CLK0N |

- |

- |

CSI0 clock 0- |

MIPI_CSI0_RXCLK0_N |

82 |

- |

GND |

- |

- |

Ground |

GND |

84 |

AK33 |

MIPI_CSI0_RX_D2P |

- |

- |

CSI0 data receiving 2+ |

MIPI_CSI0_RXD2_P |

86 |

AK34 |

MIPI_CSI0_RX_D2N |

- |

- |

CSI0 data receiving 2- |

MIPI_CSI0_RXD2_N |

88 |

- |

GND |

- |

- |

Ground |

GND |

90 |

AL33 |

MIPI_CSI0_RX_D3P |

- |

- |

CSI0 data receiving 3+ |

MIPI_CSI0_RXD3_P |

92 |

AL34 |

MIPI_CSI0_RX_D3N |

- |

- |

CSI0 data receiving 3- |

MIPI_CSI0_RXD3_N |

94 |

- |

GND |

- |

- |

Ground |

GND |

96 |

AM33 |

MIPI_CSI0_RX_CLK1P |

- |

- |

CSI0 clock 1+ |

x |

98 |

AM34 |

MIPI_CSI0_RX_CLK1N |

- |

- |

CSI0 clock 1- |

x |

100 |

- |

GND |

- |

- |

Ground |

GND |

2.6 SoM Hardware Design Description

2.6.1 SoM Circuit Design Guide

The FET3588-C SoM integrates power and storage circuits into a compact module, requiring minimal external circuitry. A minimum system can operate with just power supply and boot configuration, as shown in the figure below:

Please refer to “Appendix IV“ for the minimal system schematic diagram However, in most cases, it is recommended to connect some external devices in addition to the minimal system, such as a debugging serial port, otherwise, the user can not check whether the system is booted. After completing these steps, additional user-specific functions can be added based on the default interface definitions provided by Forlinx for the SoM.

Please refer to section 3.5 in “Chapter 3. OK3588-C Carrier Board Description” for the peripheral circuits.

2.6.2 Design Guide for Vibration Resistance of the SoM

It uses M2 anti-loosening screws to fix the pre-set mounting holes at the four corners of the SoM. The tightening torque is controlled at 0.15 N·m. The specific assembly schematic diagram is as follows:

This design has passed the vibration test specified in the standards GB/T 2423.10 - 2008 / IEC 60068 - 2 - 6:1995, meeting the following levels:

Frequency range: 10 Hz ~ 150 Hz Test axes: X, Y, and Z axes Displacement amplitude: 0.35 mm Acceleration amplitude: 5 g

The performance data listed in this manual is based on tests conducted in a standard laboratory environment and is applicable to general industrial equipment. The performance in actual applications may vary due to factors such as the installation method and combined stress.

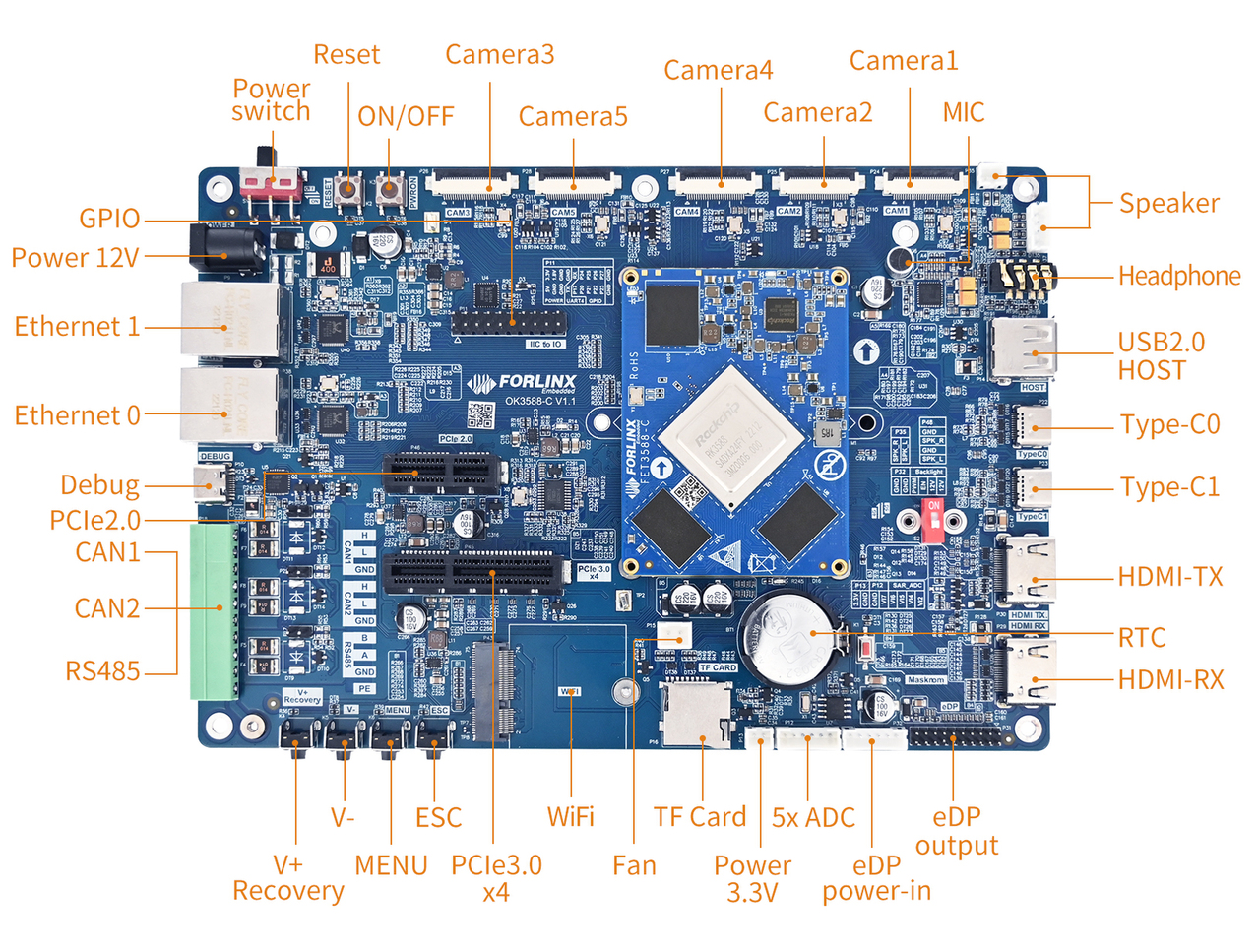

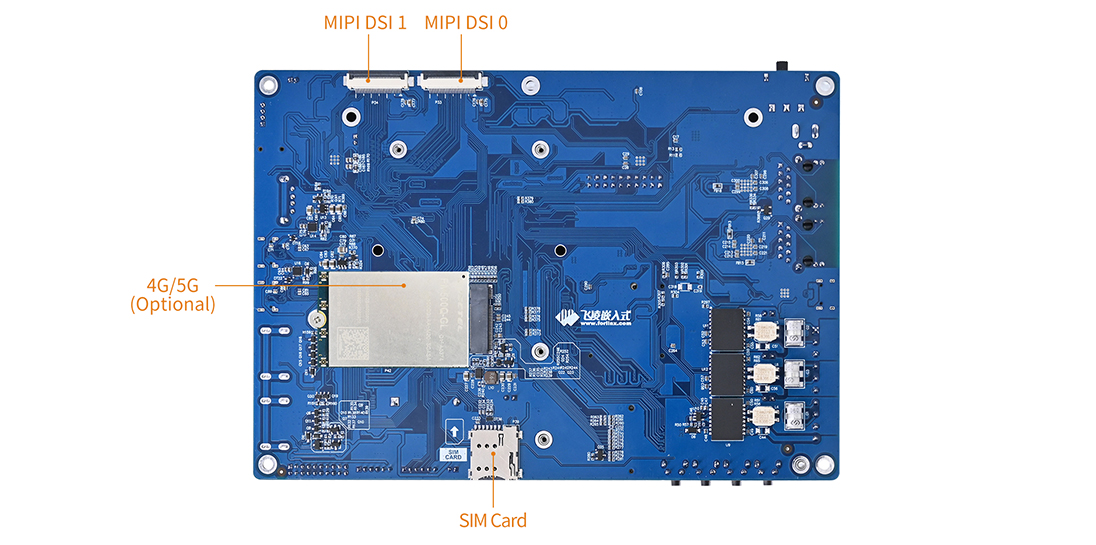

3. OK3588-C Development Platform Description

3.1 OK3588-C Development Board Interface Diagram

Connection method is board-to-board, and main interfaces are shown in the figure below:

Front

Back

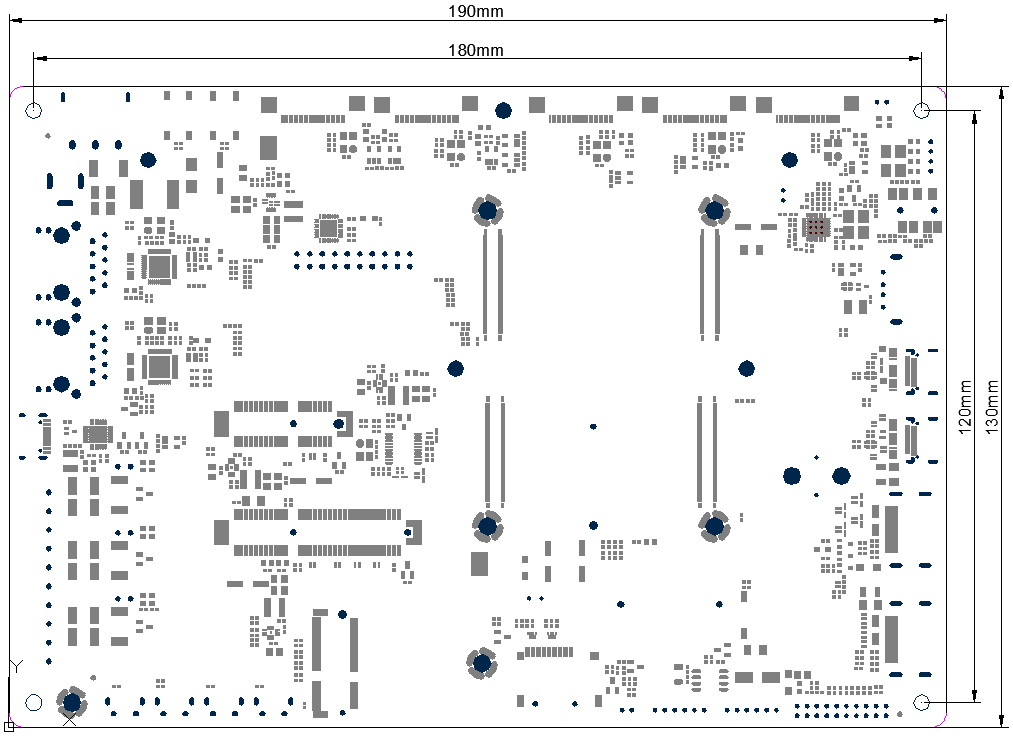

3.2 OK3588-C SoM Dimension Diagram

PCB Size: 190mm × 130mm.

Fixed hole size: spacing: 180mm × 120mm, hole diameter: 3.2mm.

Plate making process: thickness 1.6mm, 4-layer PCB.

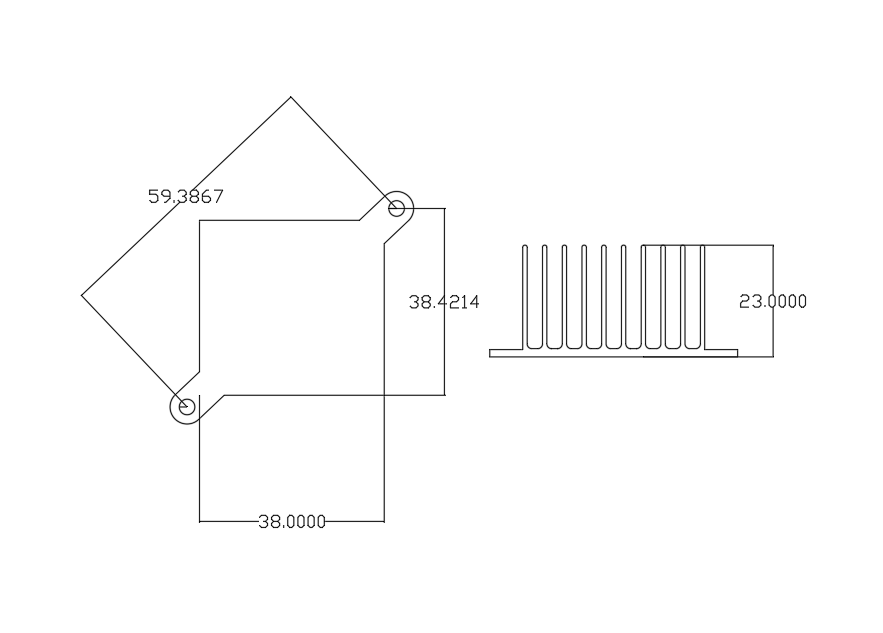

The OK3588-C carrier board reserves an installation hole with a diameter of 3.2 mm for a heat sink. You can choose to install the heat sink according to the on - site environment. Please add a layer of insulating thermal conductive silicone pad on the contact surface between the heat sink and the SoM. 38Mm×38mm×23mm. For more detailed dimensions, please refer to the following figure.

3.3 Carrier Board Naming Rules

A - B - C + D E F : G - H

Field |

Field Description |

Value |

Description |

|---|---|---|---|

A |

Product Line Identification |

OK |

Forlinx Embedded carrier board |

- |

Separator |

- |

The separator “-” is omitted between the product line |

B |

CPU Name |

3588 |

RK3588 |

- |

Segment Identification |

- |

Parameter segment sign |

C |

Connection |

C |

Board to Board Connector |

+ |

Segment Identification |

+ |

The configuration parameter section follows this identifier. |

D |

Type |

M |

Carrier board (Note: carrier board identification M, not filled by default) |

E |

Operating Temperature |

C |

0 to 80℃ Commercial-grade |

F |

PCB Version |

11 |

V1.1 |

: |

Separator |

: |

It’s followed by the manufacture’s internal identification. |

G |

Connector origin |

1 |

Imported connector |

- |

Connector |

- |

Grade Mark Connector |

H |

Grade Identification |

PC |

Prototype Sample |

Blank |

Mass Production |

||

SC |

Special-purpose use: According to the customer’s special requirements for special modifications |

3.4 Carrier Board Resources

Function |

Quantity |

Parameter |

|---|---|---|

MIPI CSI |

5 |

•2 × MIPI DPHY V1.2 4-lane interfaces, each lane supporting up to 2.5 Gbps; routed via 2 x 26-pin FPC connectors, with OV13850 cameras mounted by default; |

MIPI DSI |

2 |

•Each MIPI interface supports 4lane output with a maximum resolution of 4K@60fps; |

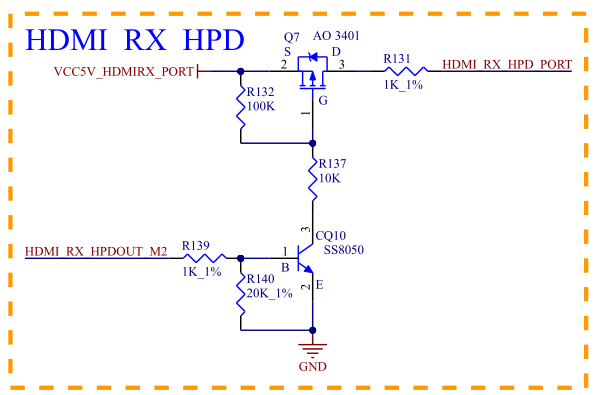

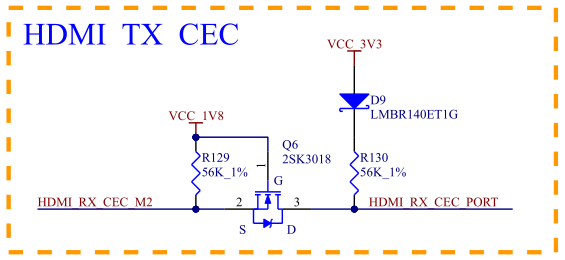

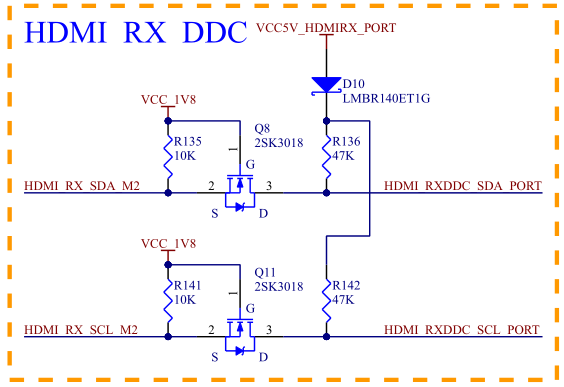

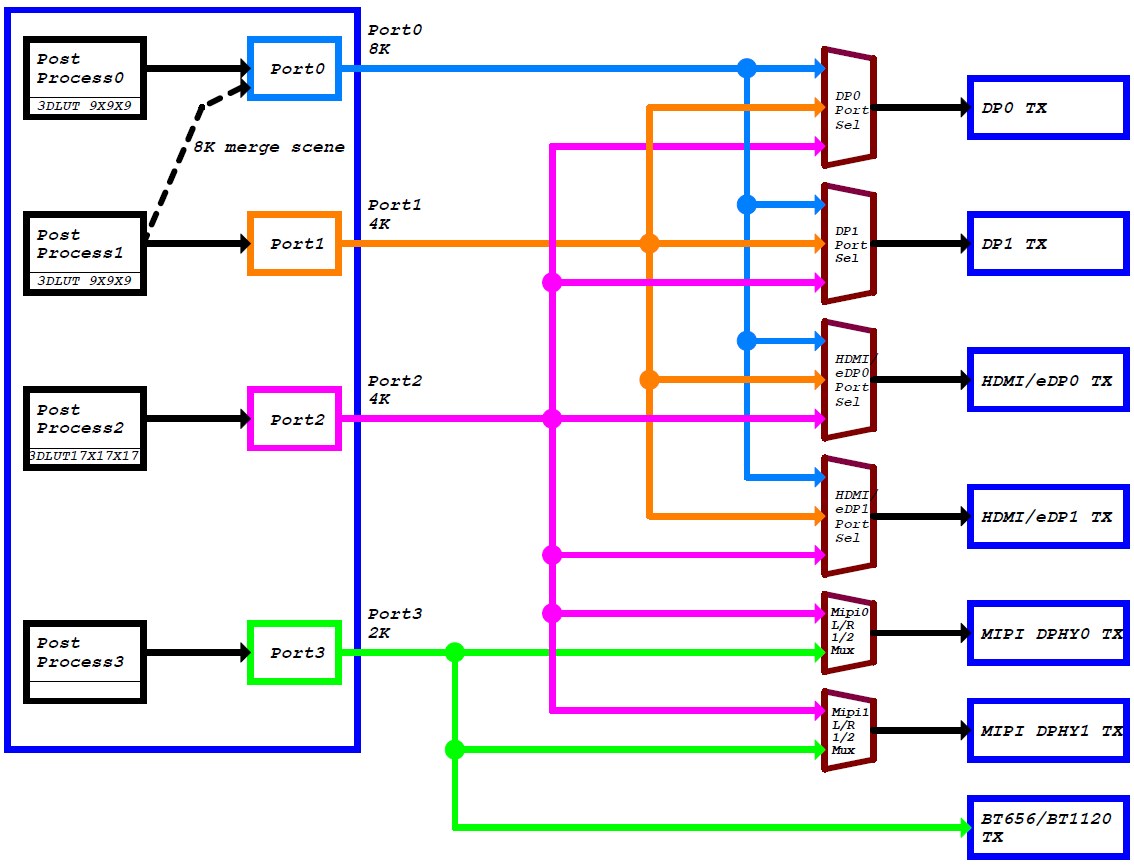

HDMI RX |

1 |

•Led out via standard HDMI socket; |

HDMI TX |

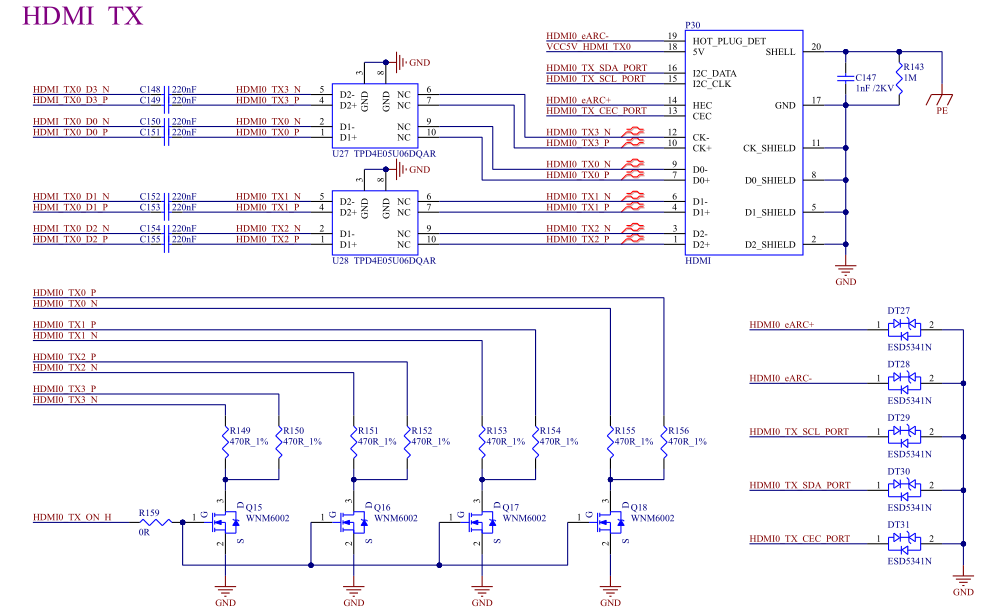

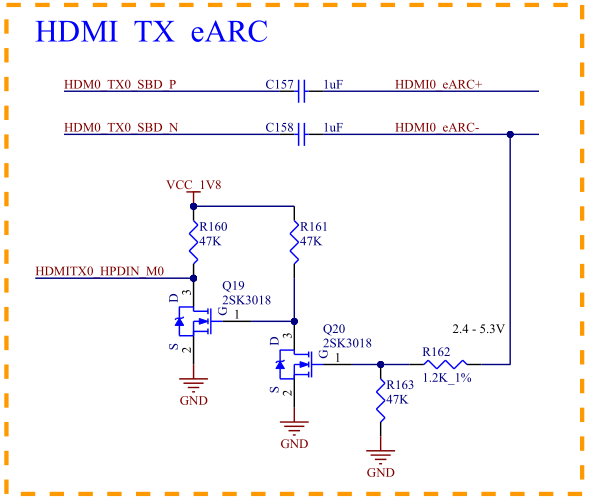

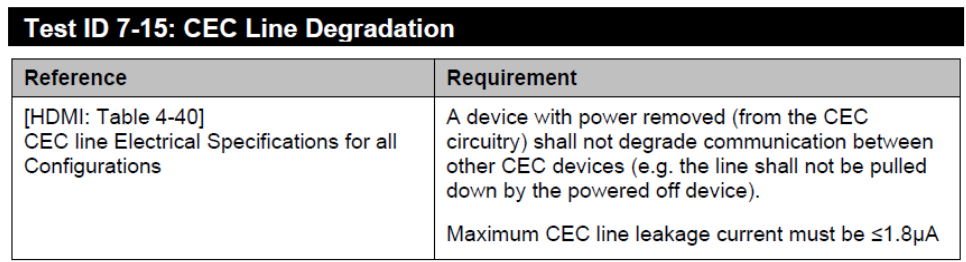

1 |

•Led out via standard HDMI socket; |

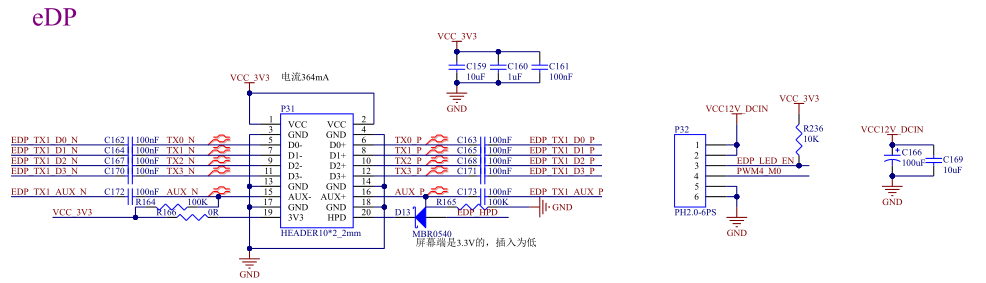

eDP TX |

1 |

•Adapt to 1080p @ 60Hz display; |

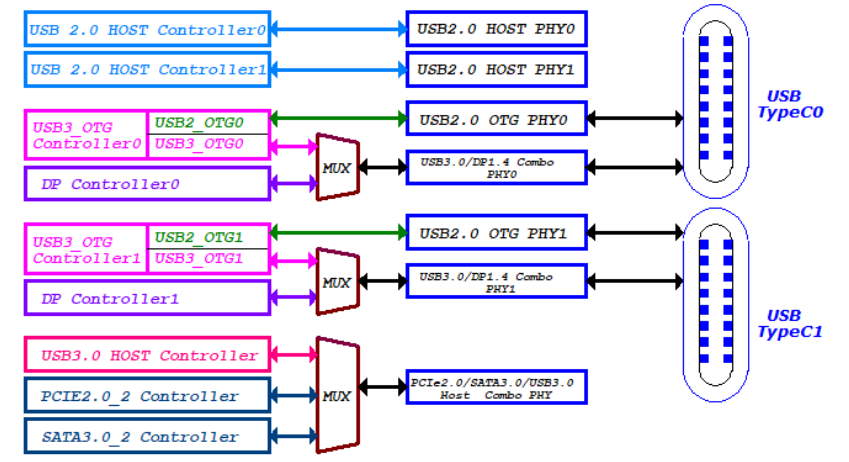

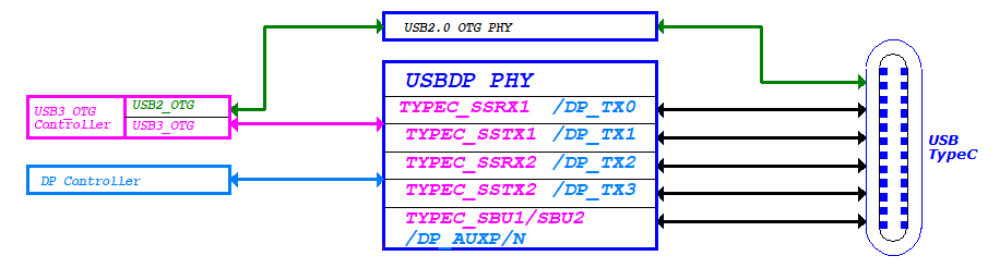

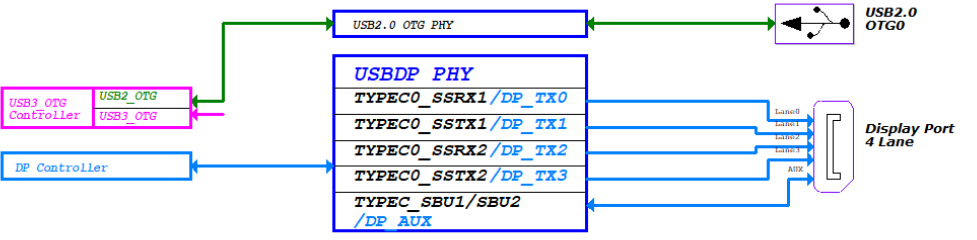

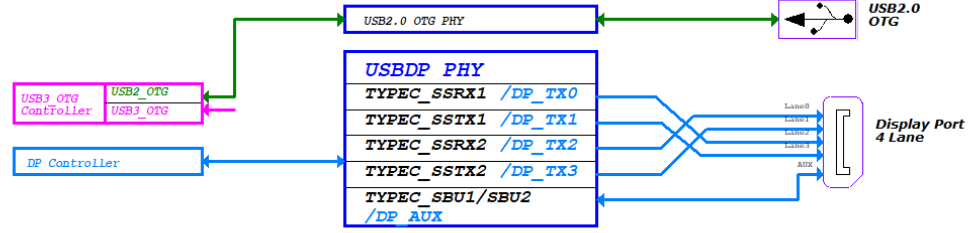

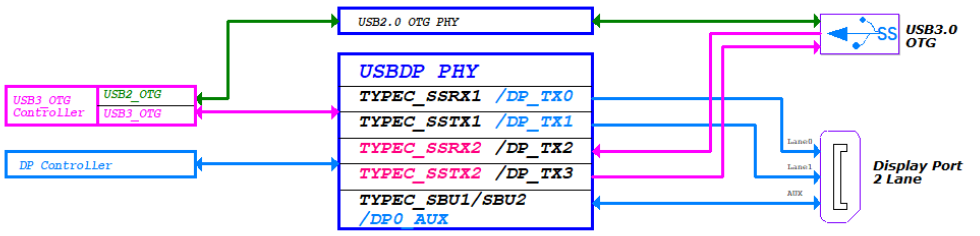

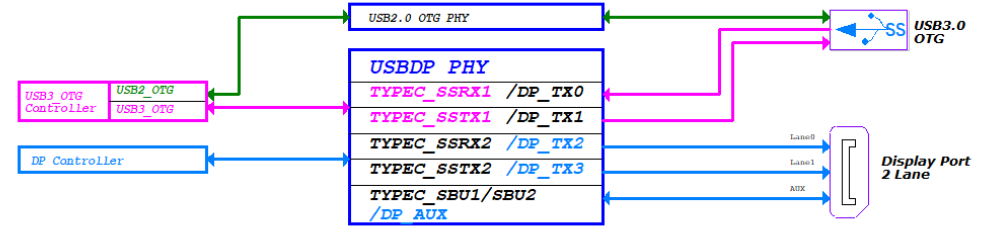

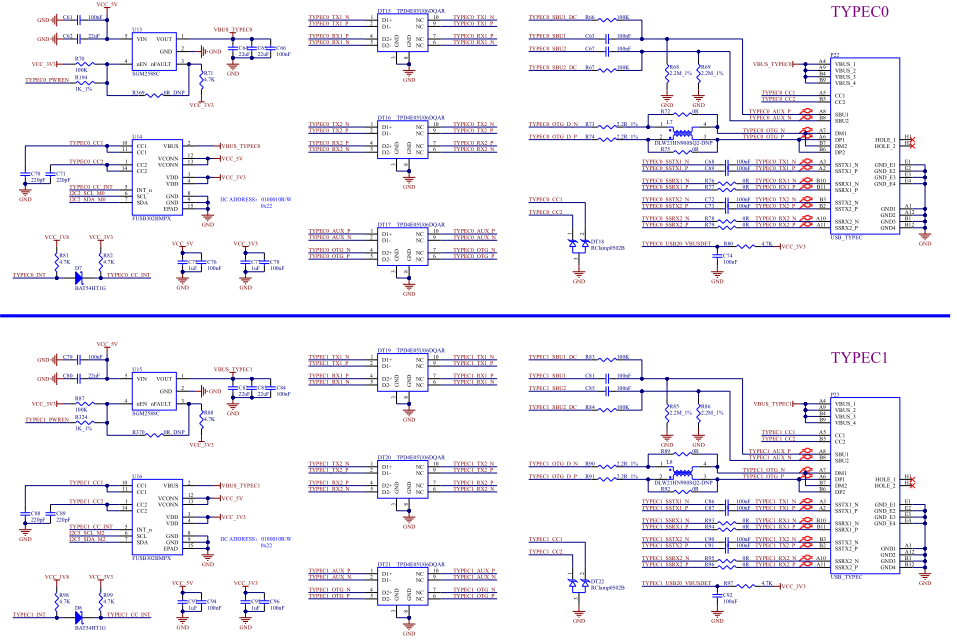

DP TX |

2 |

•2 x DP interfaces are used in combination with USB3.1 Gen1 and led out through Type-C interface; |

USB3.1 Gen1 |

2 |

•Led out via Type-C interface; |

USB2.0 Host |

1 |

•Led out via Type-A USB interface; |

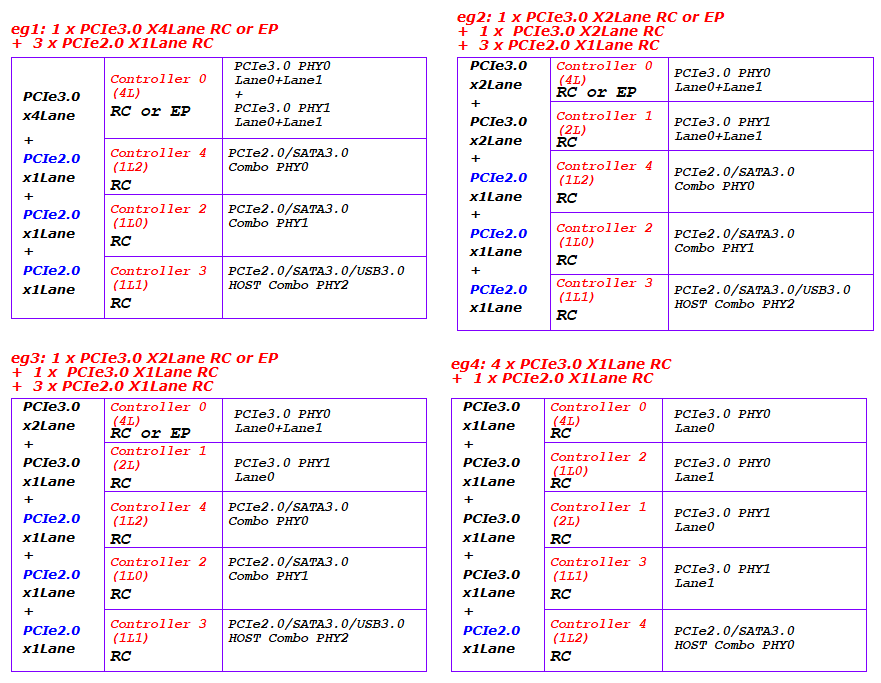

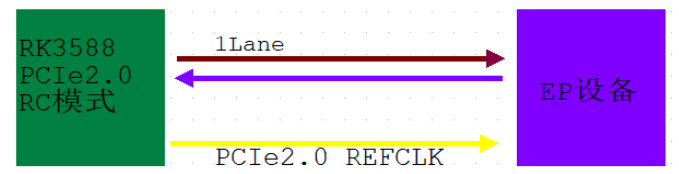

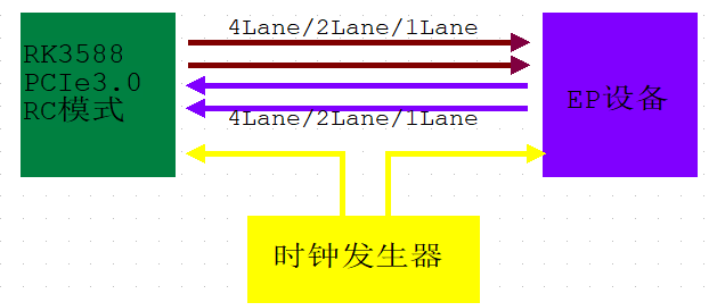

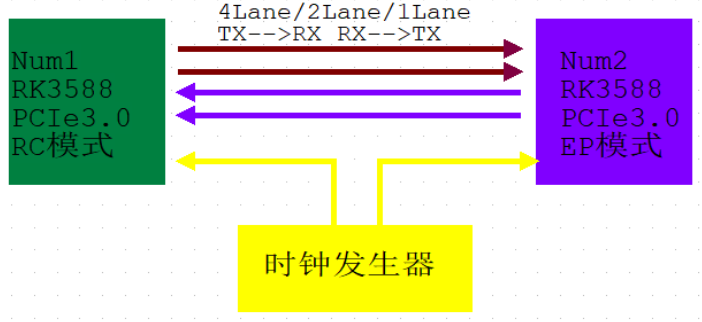

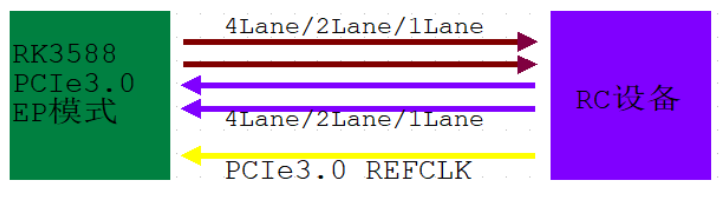

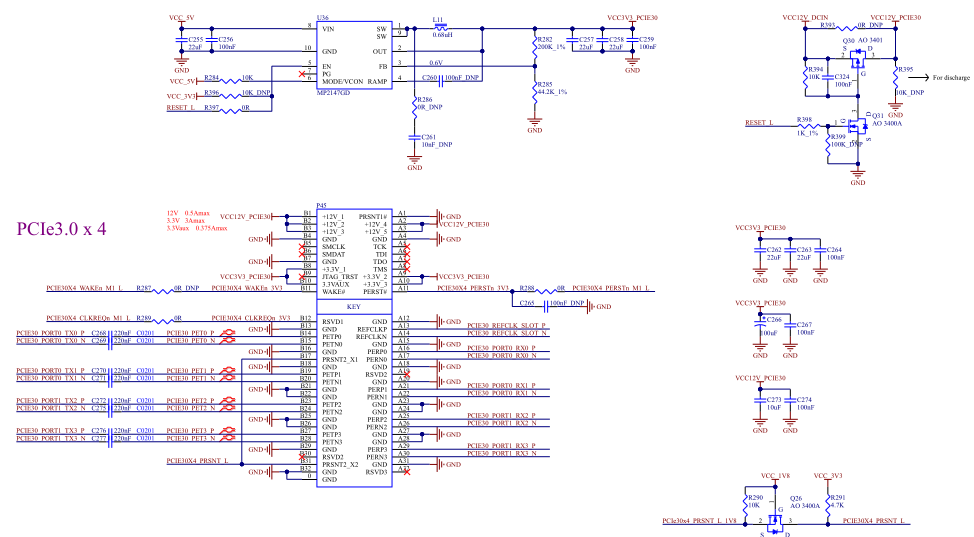

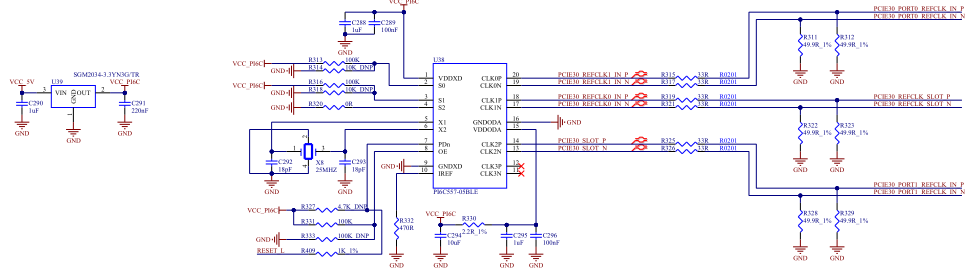

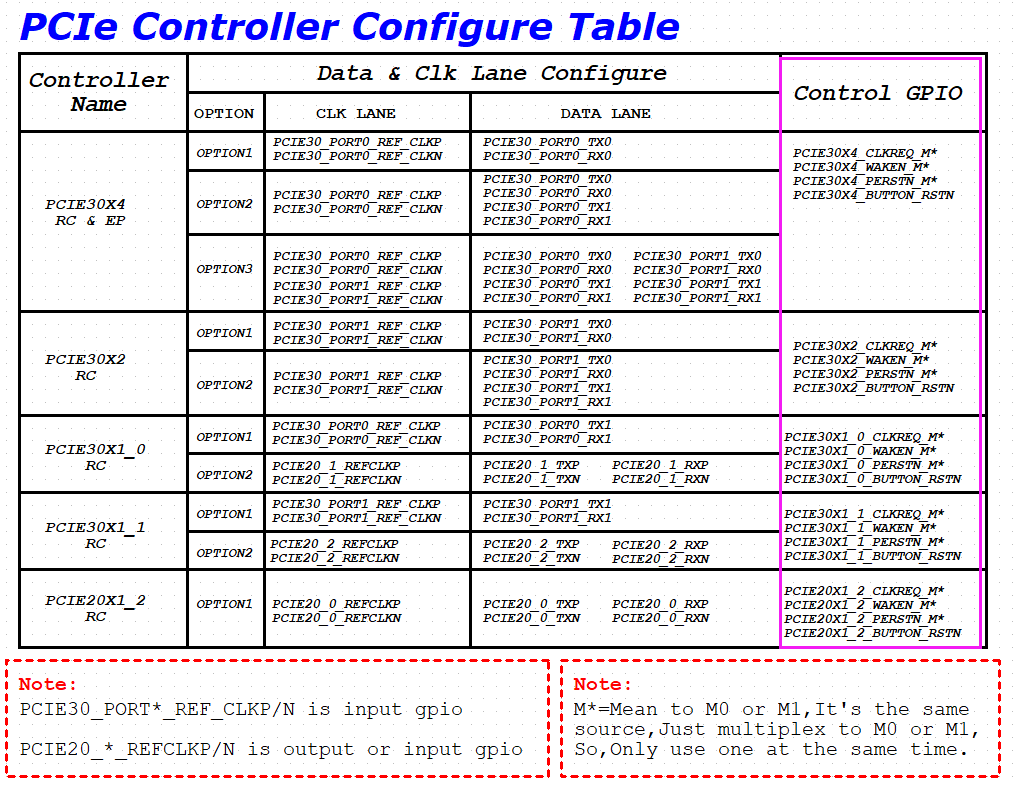

PCIe3.0 |

1 |

•1x 4lanes PCIe signals led out via PCIe X 4 slots; |

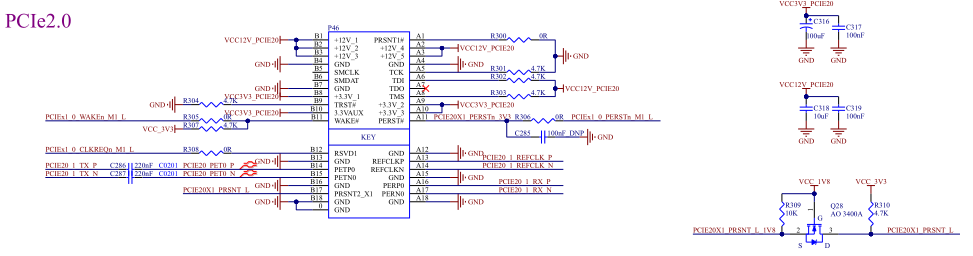

PCIe2.0 |

1 |

•Led out via PCIe X 1 slot; |

Ethernet |

2 |

•Led out via 2 x RJ45 interfaces; |

TF card |

1 |

•TF card is available, rate up to 150MHz,support SDR104 mode; |

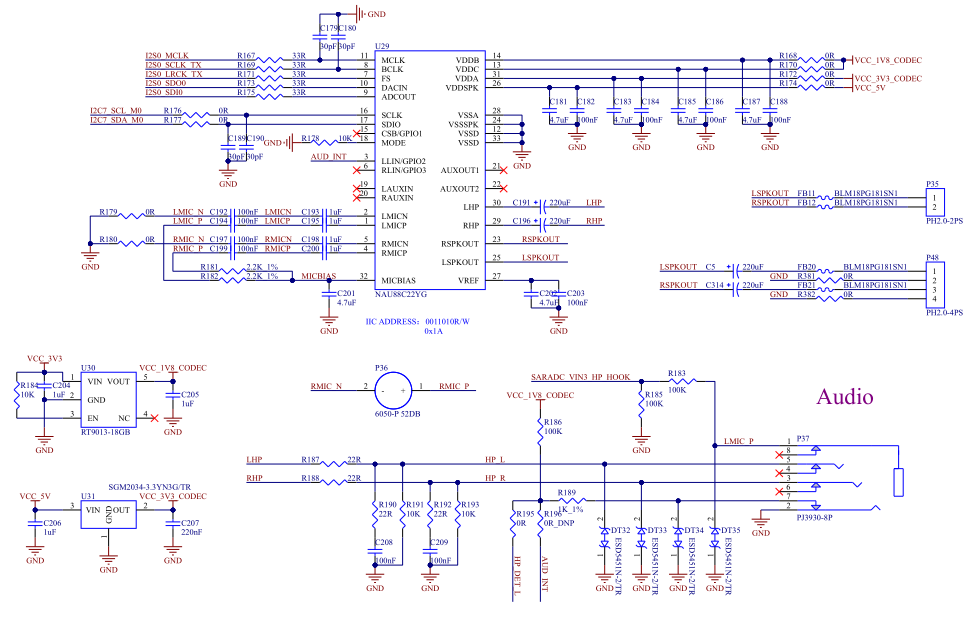

Audio |

1 |

•Codec chip on board, support headphone output, MIC input level Speaker; |

RS485 |

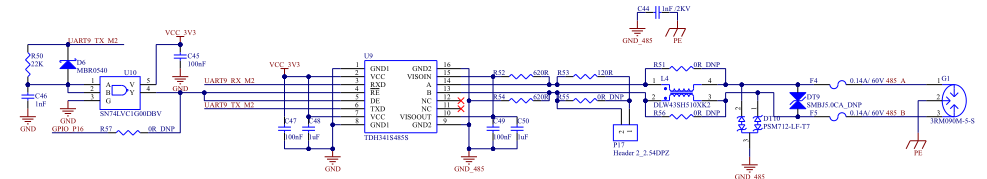

1 |

•1 x RS485 CAN bus led out through RS485 transceiver; |

UART |

1 |

•Led out via 2.54 mm pitch; |

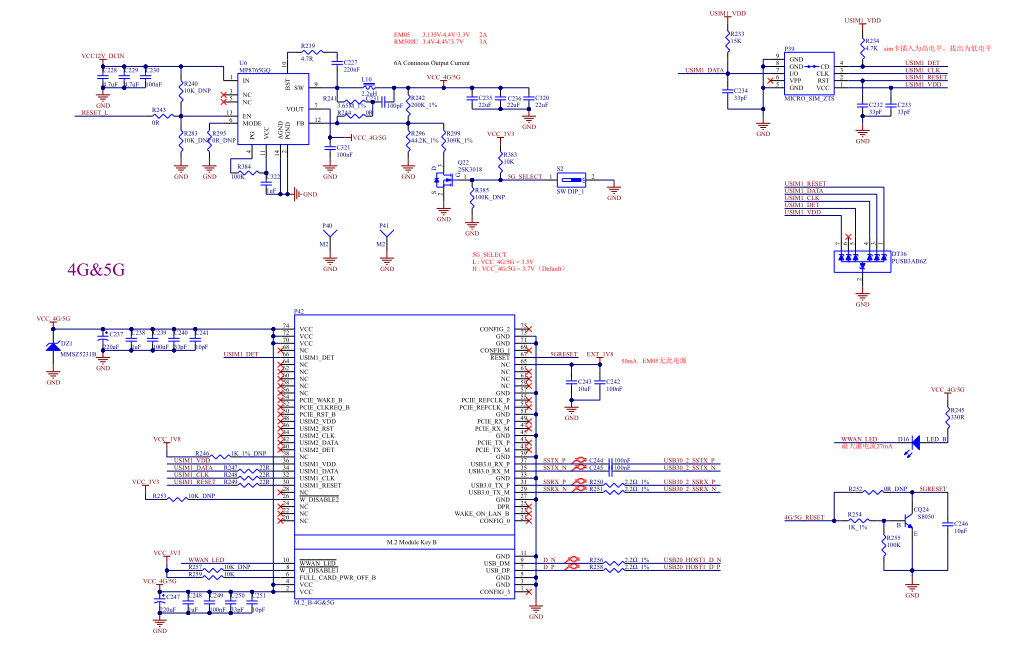

4G/5G |

1 |

•Supports 4G/5G modules packaged in M.2 format; |

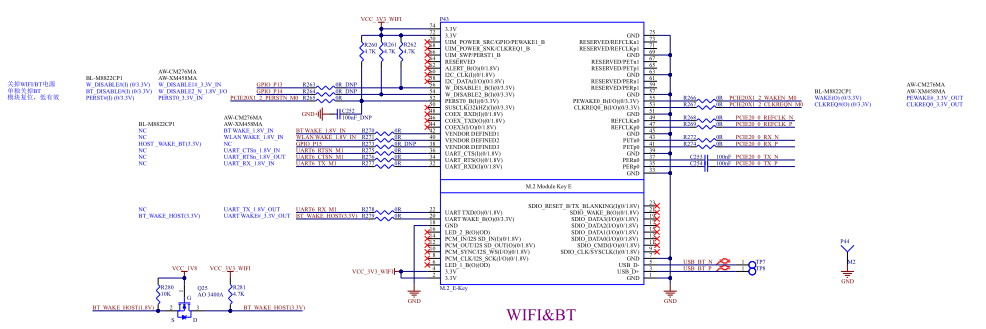

WIFI&BT |

1 |

• Supports M.2-packaged Wi-Fi & BT modules; |

ADC |

5 |

• Led out via PH2.0 socket; |

RTC |

1 |

•Onboard RTC chip and battery socket; |

FAN |

1 |

•Onboard fan connector; |

GPIO |

9 |

•9 x GPIO (3.3 V level) and 5V, 3.3 V, and 1.8 V power led out via a 2.54 mm pitch header pin; |

**Note: **

“TBD” means the function has not been developed in this phase;

The parameters in the table are hardware design or theoretical CPU values.

3.5 OK3588-C Carrier Board Description

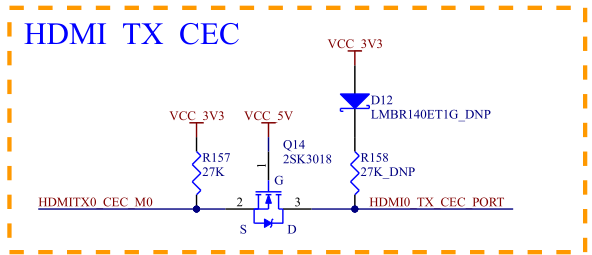

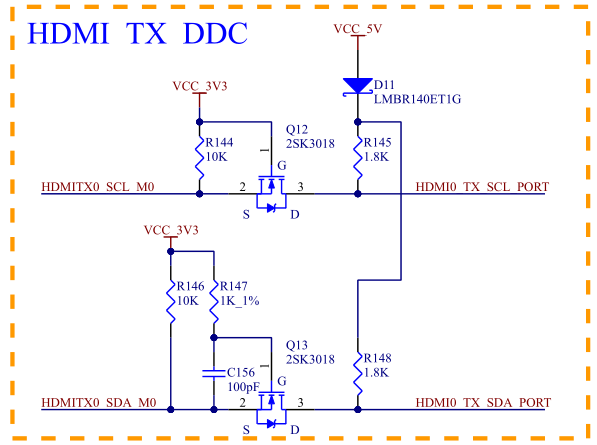

Note: The component UID with “_DNP” mark in the diagram below represents it is not soldered by default.

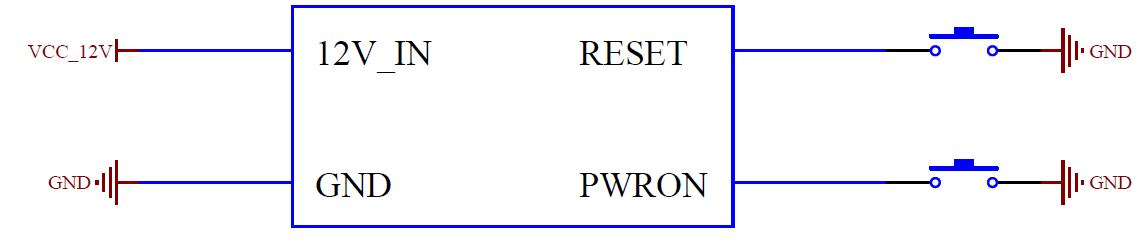

3.5.1 Carrier Board Power

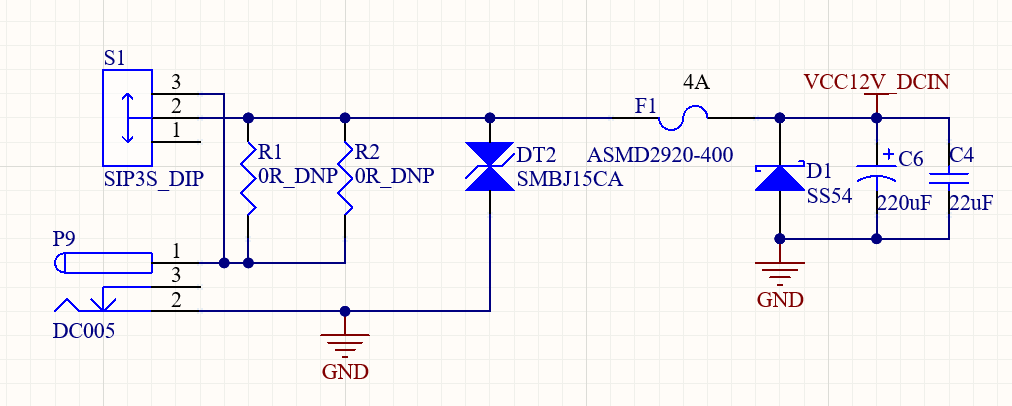

It uses a 12V power adapter for the power supply, and the power connector is a DC005 socket. S1(DIP switch) is the power switch, which moves according to the screen printing indication on the board. The rear of S1 has TVS for electrostatic protection, F1 for over-current protection, and D1 and F1 cooperate for anti-reverse connection protection. VCC12V_ DCIN supplies power to SoM and carrier board at the same time.

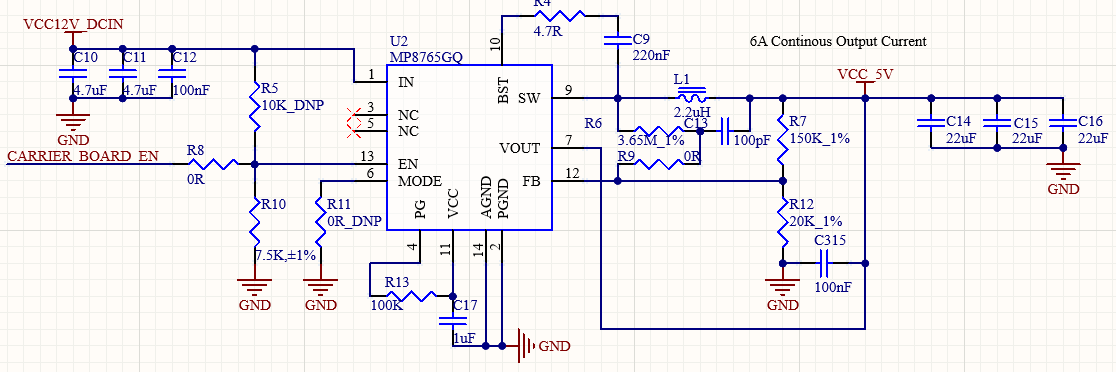

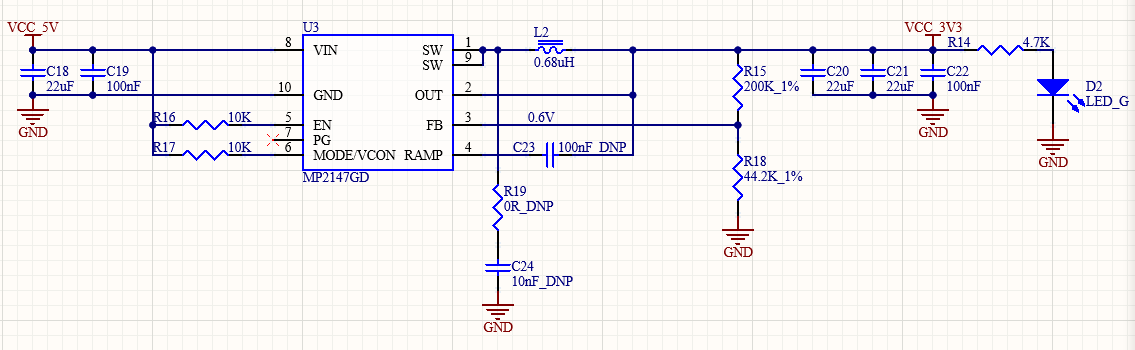

VCC12V_ DCIN is decreased to VCC _ 5V via U2. VCC_ 5V supplies power for some of the peripherals on the carrier board. To meet the power-up timing, the carrier board power-up is controlled by CARRIER_BOARD_EN–a signal of SoM. (the electrical level is 3.3V, and the driving ability is 10K pull-up. If the required driving ability of the enabling pin of the enabling device exceeds this range, a buffer or gate circuit needs to be added for increasing the driving ability to ensure SoM and carrier board power-up normally).

VCC_5V is decreased to VCC_3V3 via U3 VCC_3V3 supplies power for partial carrier board configurations.

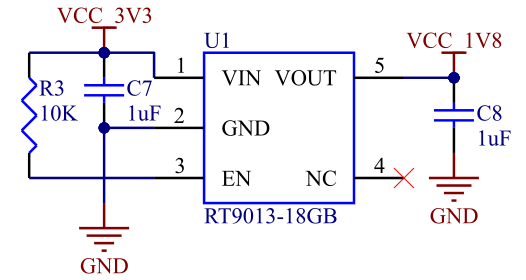

VCC_3V3 is decreased to VCC_1V8 via U1. VCC_1V8 supplies power for partial carrier board configurations.

Note:

When undertaking independent design, it is crucial to ensure proper power sequencing during power-up;

For the device selection and external layout of the buck - boost chip, you need to refer to the corresponding chip manual to ensure a good power supply loop.

3.5.2 Reset and Startup/Shutdown Signal

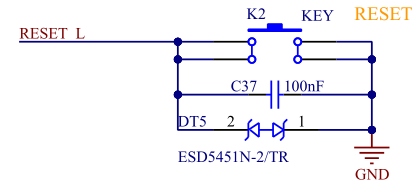

RESET_L is SoM resetting signal input connected to the key for convenient debugging.

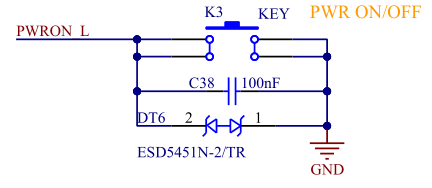

PWRON_L is an On/Off signal input connected to the key for convenient debugging.

3.5.3 Boot Configuration

RK3588 supports multiple boot modes. After resetting the chip reset, the boot code integrated inside the chip can be booted on the following interface devices, and the specific boot sequence can be selected according to actual application requirements:

·Serial Flash(FSPI)

·eMMC

SDMMC Card

If there is no boot code in the above devices, the system code can be downloaded to these devices by the USB2.0 OTG0 interface TYPEC0_OTG_DM / TYPEC0 _OTG_DP signal.

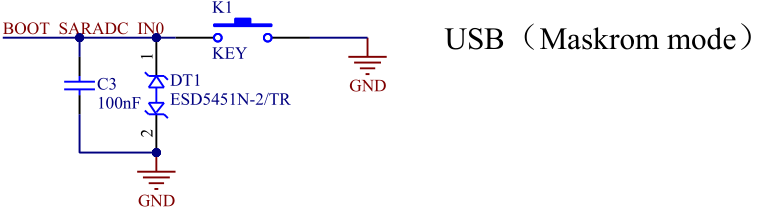

Boot Sequence Selection:

The boot sequence of RK3588 can be set by BOOT_SARADC_IN0 (PIN: P1_28), and it can boot from the peripheral corresponding to the different interfaces. As shown in the table below, the hardware is configured with different up and down resistance values to design the peripheral boot sequence of LEVEL1-LEVEL7 in seven modes that can configurable according to actual application requirements

Table 3.5.2.1 Boot Sequence Configuration

Item |

Rup |

Rdown |

ADC |

VOL |

BOOT MODE |

|---|---|---|---|---|---|

LEVEL1 |

DNP |

1K |

0 |

0V |

USB (Maskrom mode) |

LEVEL2 |

10K |

2K |

682 |

0.3V |

SD Card-USB |

LEVEL3 |

10K |

5.1K |

1365 |

0.6V |

EMMC-USB |

LEVEL4 |

10K |

10K |

2047 |

0.9V |

FSPI M0-USB |

LEVEL5 |

10K |

20K |

2730 |

1.2V |

FSPI M1-USB |

LEVEL6 |

10K |

50K |

3412 |

1.5V |

FSPI M2-USB |

LEVEL7 |

10K |

DNP |

4095 |

1.8V |

FSPI M2-FSPI M1-FSPI M0-EMMC-SD Card-USB |

BOOT_SARADC_IN0 on SoM is 10K pull-up, so the SoM defaults to start from eMMC The pull-down resistor can be added to the carrier board to achieve other boot sequences. According to the above LEVEL1 setting, OK3588-C connects BOOT_ SARADC_ IN0 to GND by the touch key to achieve Maskrom mode.

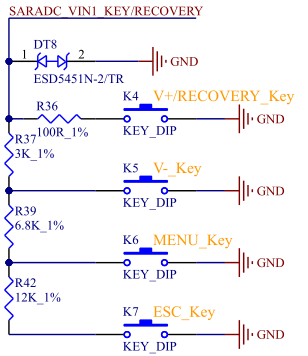

SARADC_ VIN1 is used to enter the recovery state due to a short circuit to the ground, and the SoM pulls it up to a 1.8V power supply using a 10K resistor. On RK3588, the key array adopts a parallel type, which can adjust the input key value by increasing or decreasing the keys and adjusting the proportion of the voltage divider resistor to achieve multi-key input to meet customer product requirements; It is recommended in the design that any two key values must be greater than ± 35, i.e. the center voltage difference must be greater than 123mV. As shown below:

Note: When doing key acquisition, ESD protection is required near the keys. And 0 key value must be connected in series with a 100ohm resistor to strengthen the anti-static surge capacity (If there is only one button, ESD must be close to the button, ESD → 100ohm resistor → 1nF → chip pin).

3.5.4 System Initialization Configuration Signal

There is one important signal in the FET3588 that affects the system boot configuration and needs to be configured and kept in a stable state before power-up:

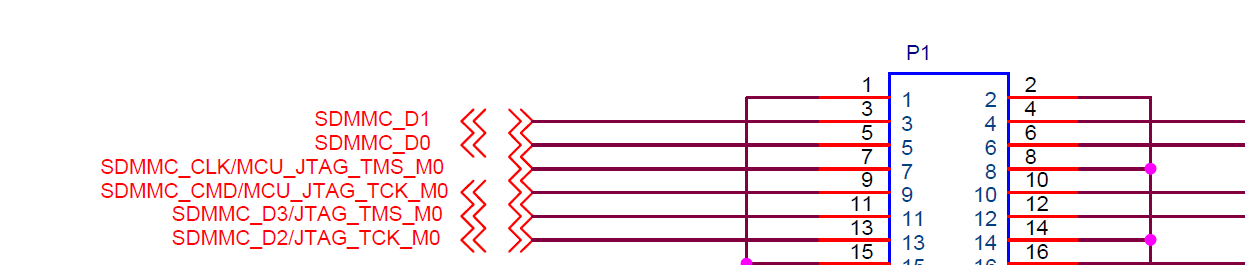

GPIO0_A4 (PIN: P3_90) (default function is SDMMC_DET): determines whether P1_7, P1_9, P1_11, P1_13 are SDMMC or JTAG functions.

The ARM JTAG function of RK3588 is multiplexed with SDMMC function, and IOMUX function is switched via SDMMC_DET pin, so this pin also needs to be configured before power-up, otherwise, no output of the ARM JTAG function will affect the debugging of the boot stage, while no output of SDMMC will affect the SDMMC boot function.

·When this pin detects high level, the corresponding IO switches to the ARM JTAG function; ·When this pin detects low level (Most SD cards inserted will pull down this pin, if not need special treatment), the corresponding IO switches to SDMMC function; ·After the system is up, it can be switched to have registers to control IOMUX, then the pin can be released; ·For easy reference, the configuration status of this pin corresponds to its function shown as follows:

Table 3.5.4.1 FET3588 System Initialization Configuration Signal Description

Signal |

Internal Pull-up&down |

Description |

|---|---|---|

GPIO0_A4 |

Pull-up |

SDMMC/ARM JTAG pin multiplexing selection control signal: |

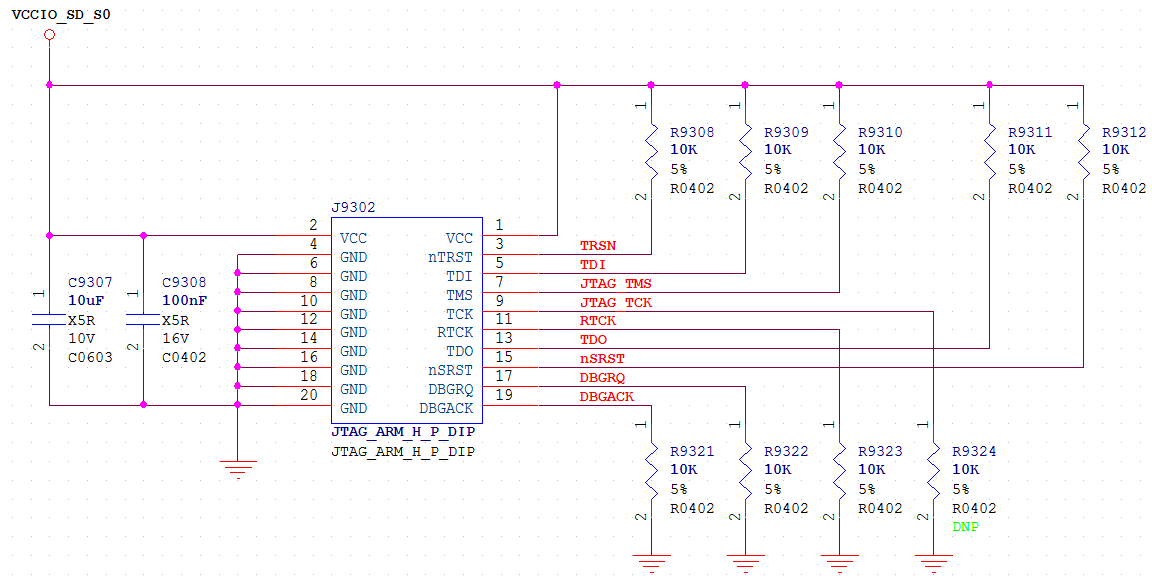

3.5.5 JTAG & UART Debug Circuit

The ARM JTAG interface of the RK3588 chip complies with IEEE1149.1 standard, and the PC can connect to the DSTREAM emulator via SWD mode (two-wire mode) to debug the ARM Core inside the chip.

ARM JTAG interface description is as follows:

Table 3.5.5.1 RK3588 JTAG Debug

Signal |

Description |

|---|---|

JTAG_TCK_M0/M1 |

SWD mode clock input |

JTAG_TMS_M0/M1 |

SWD mode data input and output |

The JTAG connections and standard connector pin definitions are shown as follows:

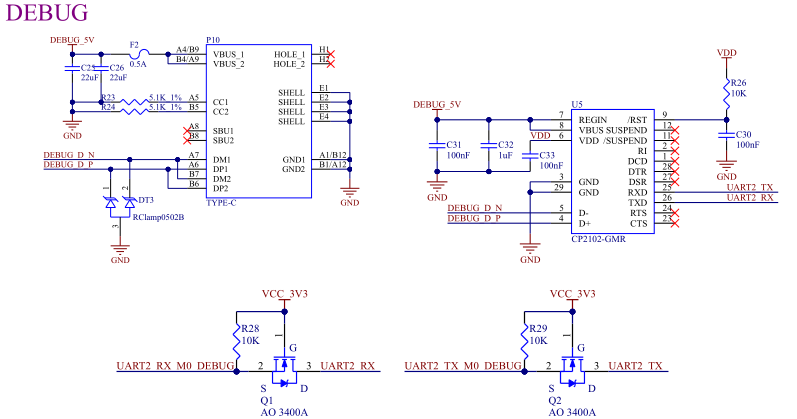

FET3588 UART Debug selects UART2_TX_M0_DEBUG (P2_7)/UART2_RX_M0_DEBUG (P2_9) by default. UART Debug signal needs to be connected with 100ohm resistor in series, if plug-in is used, and TVS tube needs to be added near the plug-in position.

To facilitate user debugging, OK3588 uses a USB to UART chip to convert the UART signal into a USB signal and leads it out through a Type-C socket. You can connect OK3588-C P10 to PC with USB Type-A to UAB Type-C cable and install a CP2102 driver.

The schematic is as follows:

Note:

For the convenience of later debugging, please lead out the debugging serial port when designing the carrier board;

It is recommended to keep Q1 and Q2, which can effectively prevent the U5 current from flowing back to the CPU through UART2_TX/RX when the core board is not powered-up, affecting the startup and even causing damage.

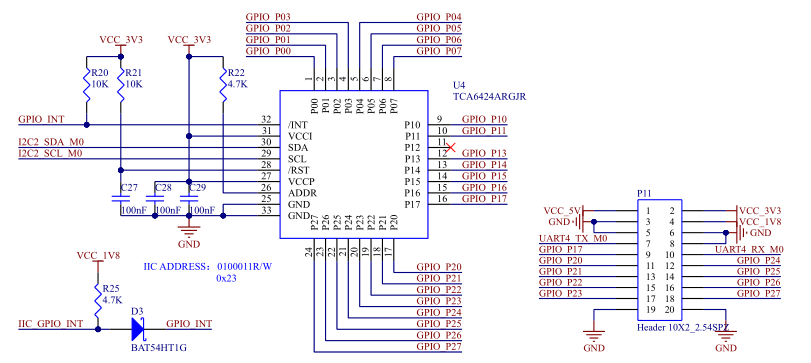

3.5.6 IIC Extending IO

To introduce more diverse interfaces, the enable and reset signals of the carrier board are completed by the IIC to IO chip U4. At the same time, the U4 spare part of IO is led out by P11 to facilitate the expansion. The principle is as follows:

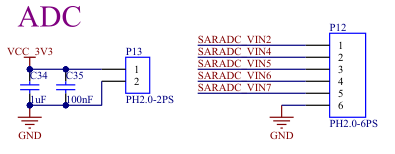

3.5.7 SARADC

The OK3588 introduces SARADC_VIN2/VIN4/VIN5/VIN6/VIN7 through P12, while P13 can provide 3.3V power output for peripherals.

As shown in the figure below:

Note: When using the SARADC_VINx, 1nF capacitor must be added near the pin to eliminate jitter.

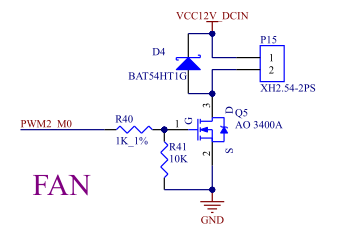

3.5.8 FAN Interface

The OK3588-C has a fan power interface, which can adjust the power supply current through PWM to achieve fan speed adjustment.

As shown in the figure below:

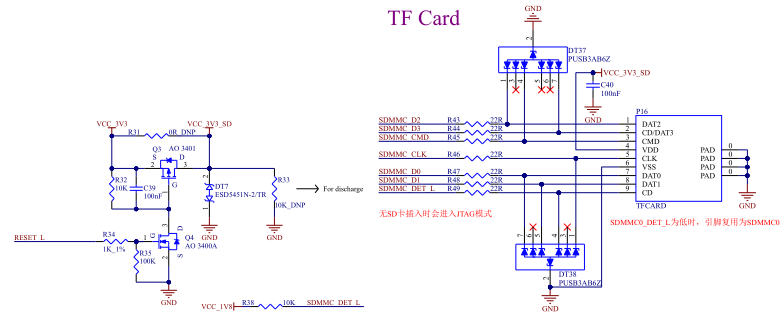

3.5.9 TF Card

The carrier board P16 is a TF Card interface, which can support system boot and flash.

Note:

The power supply for the TF card must be controlled; refer to the carrier board circuit for implementation;

Impedance requirements: Single-ended 50ohm.

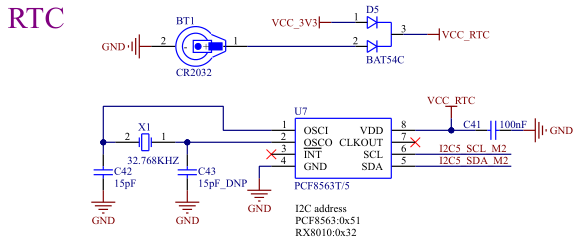

3.5.10 RTC Circuit

The OK3588 provides an on-board external RTC function for more accurate timing and lower power consumption. As shown in the figure below:

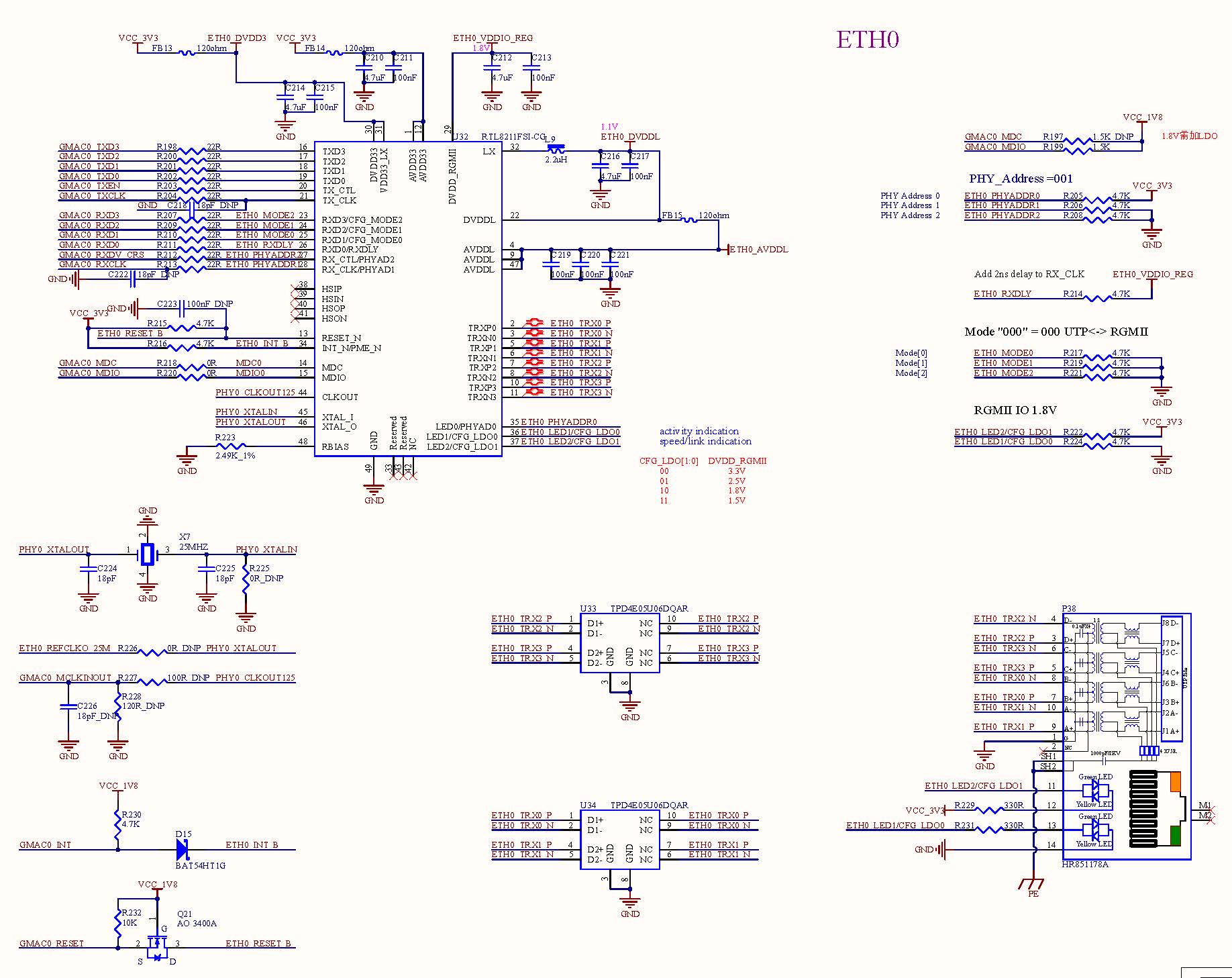

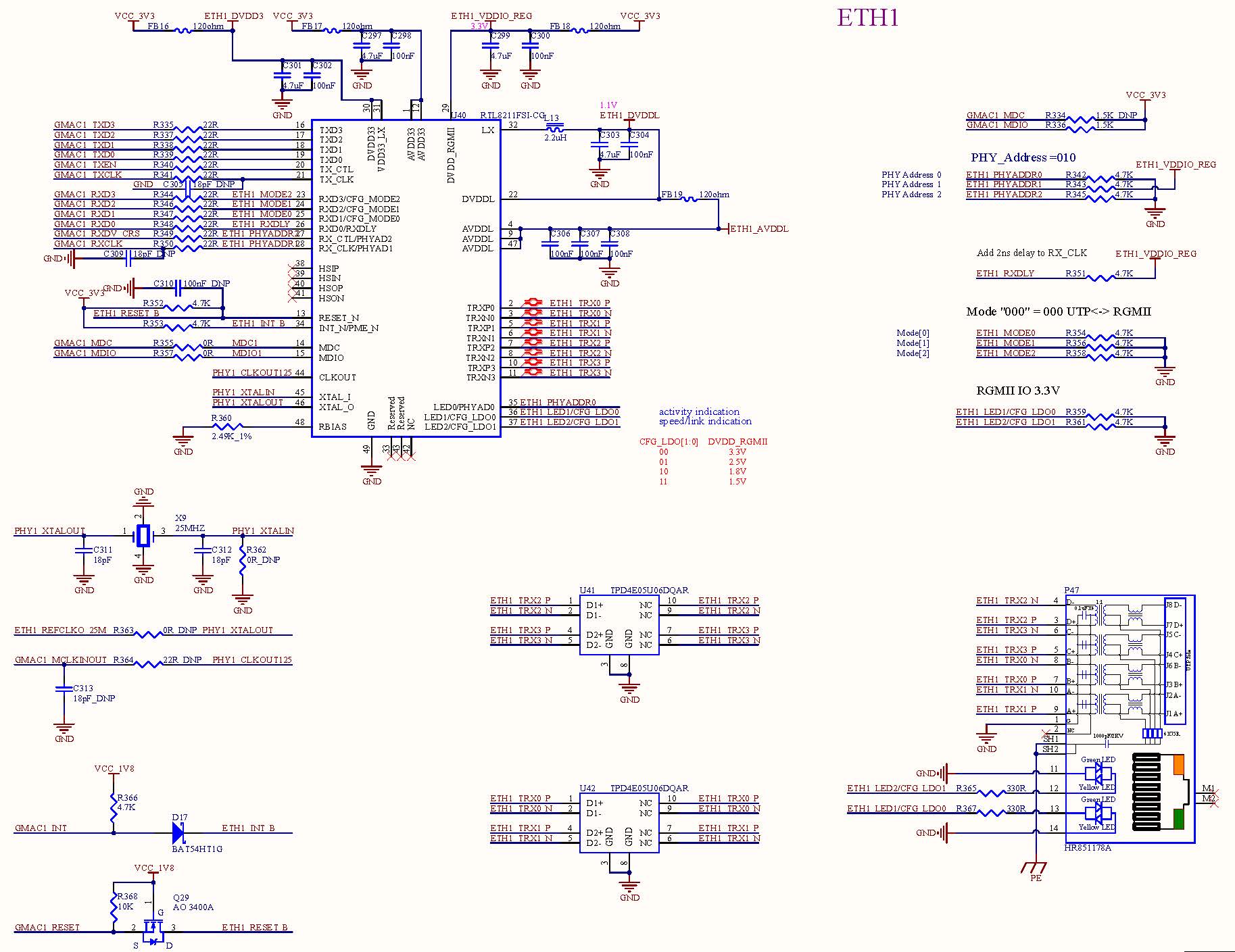

3.5.11 Ethernet Circuit

The carrier board supports dual 1000/100/10M Ethernet interfaces, which are led out via RJ45.

**Note: **

The following table shows the RK3588 RGMII/RMII interface design:

Table 3.5.11.1 RK3588 RGMII/RMII Interface

Signal |

IO Type |

RGMII Interface |

Signal Description |

RMII Interface |

Signal Description |

|---|---|---|---|---|---|

GMACx_TXD[3:0] |

Output |

RGMIIxTXD[3:0] |

Data sending |

RMIIx_TXD[1:0] |

Data sending |

GMACx_TXCLK |

Output |

RGMIIx_TXCLK |

Reference clock for data sending |

– |

– |

GMACx_TXEN |

Output |

RGMIIx_TXEN |

Data sending enable (rising edge) and data transmission error (falling edge) |

RMIIx_TXEN |

Data sending enable ( |

GMACx_RXD[3:0] |

Input |

RGMIIx_RXD[3:0] |

Data receiving |

RMIIx_RXD[1:0] |

Data receiving |

GMACx_RXCLK |

Input |

RGMIIx_RXCLK |

Data receiving reference clock |

– |

– |

GMACx_RXDV |

Input |

RGMIIx_RXDV |

Effective data receiving (rising edge) and receiving error (falling edge) |

RMIIx_RXDV_ |

Data receiving validity and carrier sense |

GMACx_MCLKINOUT |

Input/Output |

RGMIIx_MCLKIN_ |

PHY sends 125MHz to MAC, optional |

RMII_MCLKIN_50M or RMII_MCLKOUT_50M |

RMII data sending and data receiving reference clock |

ETHx_REFCLKO_ |

Output |

ETHx_REFCLKO_ |

RK3588 provides 25MHz clock to replace PHY crystal |

ETHx_REFCLKO_ |

RK3588 provides 25MHz clock to replace PHY crystal |

GMACx_MDC |

Output |

RGMIIx_MDC |

Manage the data clock |

RMIIx_MDC |

Manage the data clock |

GMACx_MDIO |

Input/Output |

RGMIIx_MDIO |

Manage data output/input |

RMIIx_MDIO |