User’s Hardware Manual_V1.8

Document classification: □ Top secret □ Secret □ Internal information ■ Open

Copyright

The copyright of this manual belongs to Baoding Folinx Embedded Technology Co., Ltd. Without the written permission of our company, no organizations or individuals have the right to copy, distribute, or reproduce any part of this manual in any form, and violators will be held legally responsible.

Forlinx adheres to copyrights of all graphics and texts used in all publications in original or license-free forms.

The drivers and utilities used for the components are subject to the copyrights of the respective manufacturers. The license conditions of the respective manufacturer are to be adhered to. Related license expenses for the operating system and applications should be calculated/declared separately by the related party or its representatives.

Revision History

Date |

User Manual Version |

SoM Version |

Carrier Board Version |

Revision History |

|---|---|---|---|---|

05/07/2022 |

V1.0 |

V1.1 |

V1.1 |

Initial Version |

12/01/2023 |

V1.1 |

V1.2 |

V1.2 |

Modifying the SoM model in the ordering information |

05/05/2023 |

V1.2 |

V1.2 |

V1.2 |

Improving the WIFI schematic diagram |

29/05/2023 |

V1.3 |

V1.2 |

V1.2 |

Updating BOOT configuration description |

13/06/2023 |

V1.4 |

V1.2 |

V1.2 |

Completing CPU description and minimum system schematic |

20/01/2024 |

V1.5 |

V1.2 |

V1.2 |

1. Completing the description of reset signal; |

18/03/2023 |

V1.6 |

V1.2 |

V1.2 |

Correcting the errors in the manual. |

27/08/2024 |

V1.7 |

V1.2 |

V1.2 |

1. Updating the dimension and glitch tolerance information of the SoM; |

28/01/2026 |

V1.8 |

V1.2 |

V2.2 |

The carrier board is upgraded to V2.2, and the circuit function description of the serial port and audio part is updated. |

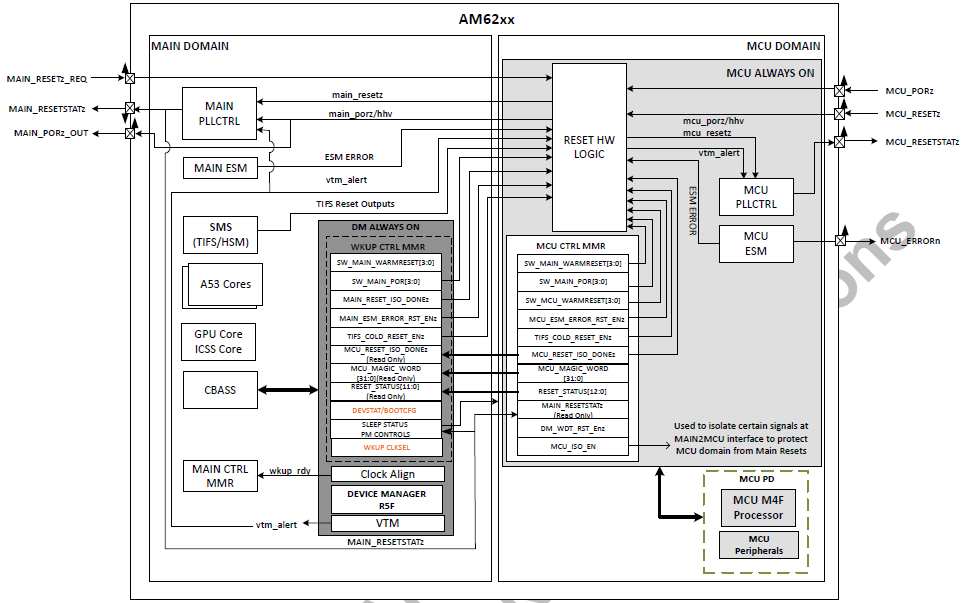

1. Introduction to AM62X

The AM62x is an extension of the Sitara™ industrial/automotive-grade heterogeneous Arm® processor family, featuring embedded 3D graphics acceleration, dual display interfaces, and a wide range of peripheral and networking options. The AM62x is built for a wide range of industrial and automotive applications. It includes up to four Arm® Cortex®-A53 cores with a 64-bit architecture, a single-core Arm® Cortex®-R5F device manager subsystem, an IMG AXE1 - 16 3D graphics module, a dual-core PRU module, and a Cortex®-M4F MCU module. The Cortex - A53x provides the powerful computing elements required for Linux applications. Linux and real - time (RT) Linux are provided through TI’s Processor SDK Linux, which is updated annually to the latest long - term support (LTS) Linux kernel, bootloader, and Yocto file system.

The AM62x has a powerful IMG AXE1 - 16 3D graphics core, suitable for HMI applications and QT acceleration, with dual display output options at a resolution of up to 2K and 60fps. Functional safety features can be enabled through the integrated Cortex - M4F and its dedicated peripherals, all of which can be isolated from the rest of the SoC. There are two external Gigabit Ethernet ports that support TSN. The additional PRU module can provide real - time I/O capabilities for customers’ own use cases. In addition, the AM62x also includes a wide range of peripheral sets to achieve system - level connectivity, such as USB, MMC/SD, camera interface, OSPI, CAN - FD, and GPMC for parallel host interfaces with external ASIC/FPGA. The AM62x supports secure boot for IP protection through a built - in HSM (Hardware Security Module) and also adopts advanced power management support for portable and power - sensitive applications.

Target Applications:

• Human - Machine Interface (HMI)

• Retail Automation

• Driver Monitoring System (DMS/OMS)/Interior Monitoring (ICM)

• Telematics Control Unit (TCU)

• 3D Point Cloud

• Vehicle-to-Infrastructure/Vehicle-to-Vehicle (V2X / V2V)

• 3D Reconfigurable Automotive Instrument Panel

• Device User Interface and Connectivity

• Medical Equipment …..

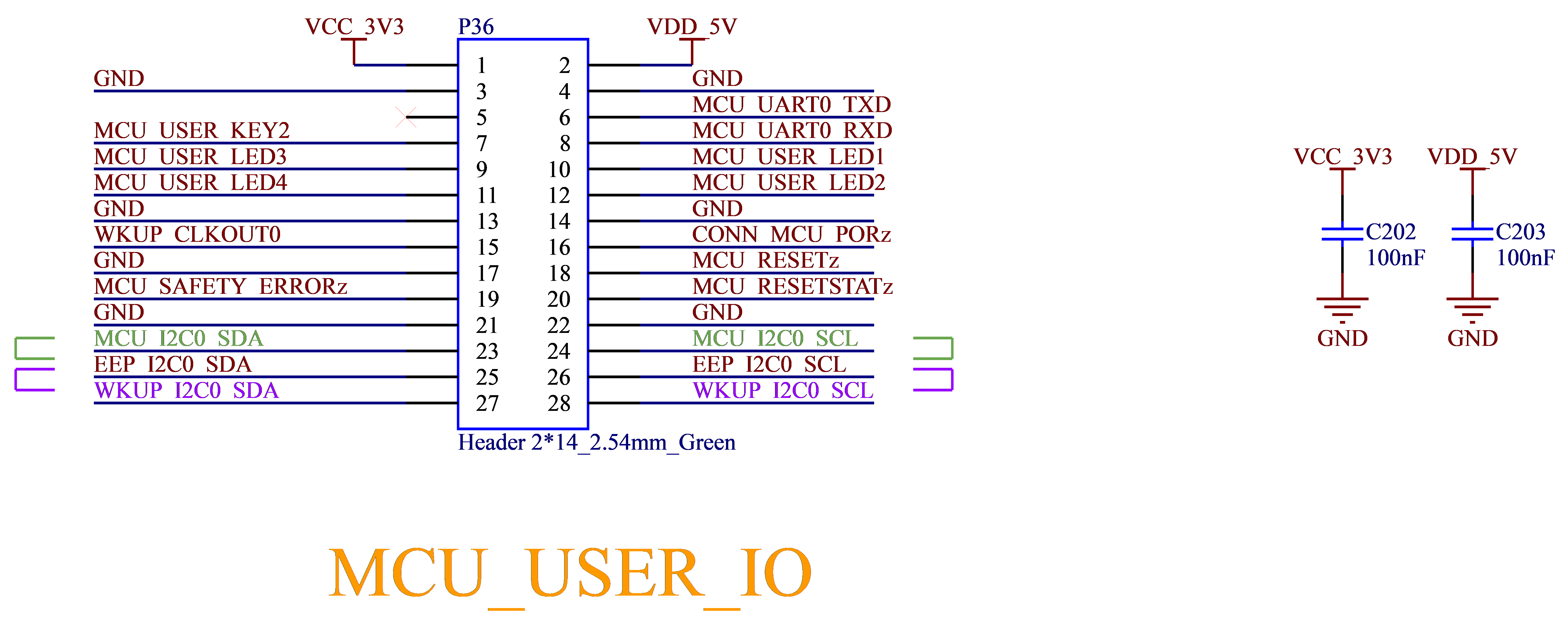

AM62x Block Diagram

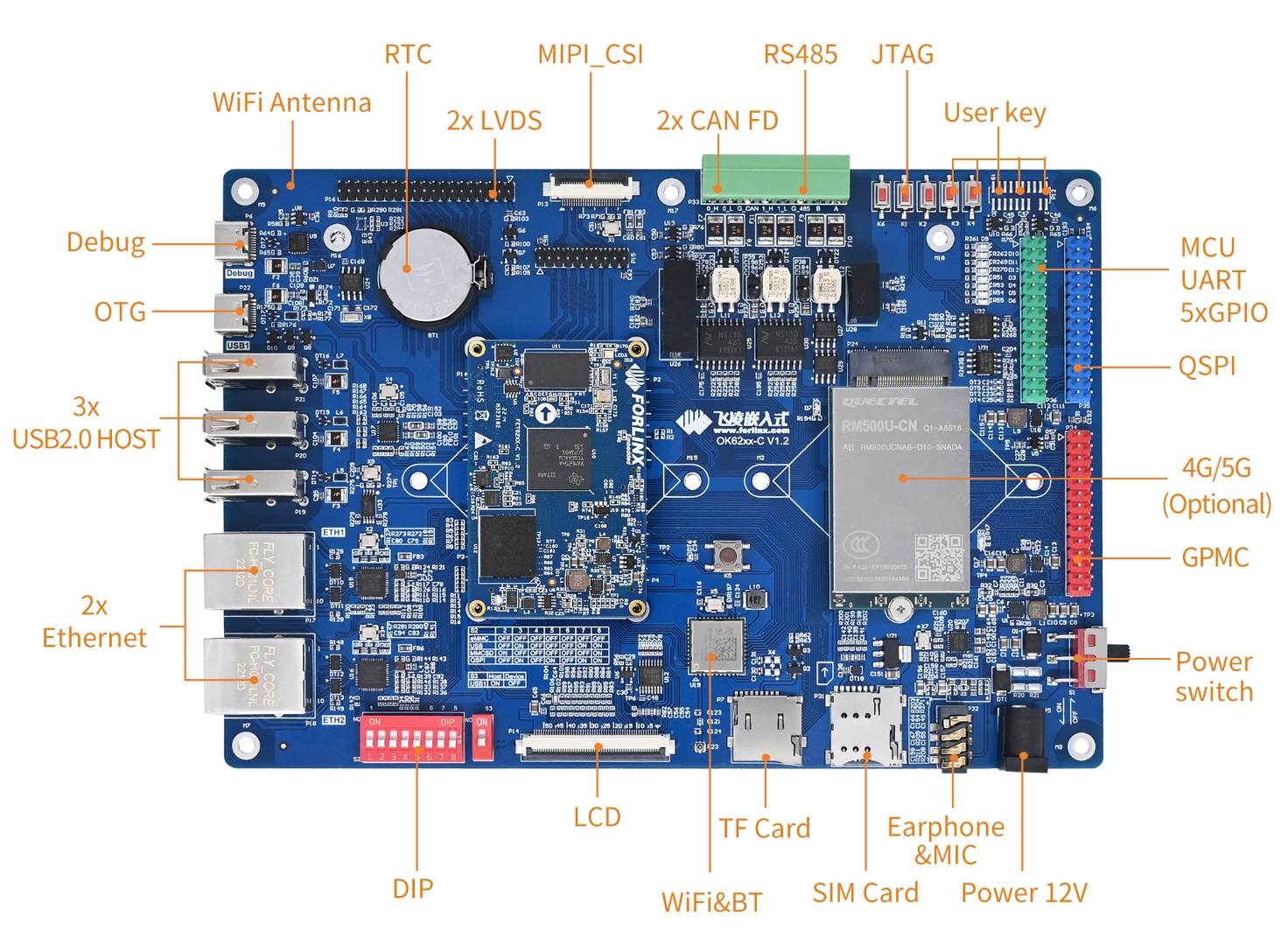

2. FET62xx-C SoM Description

2.1 FET62xx-C SoM

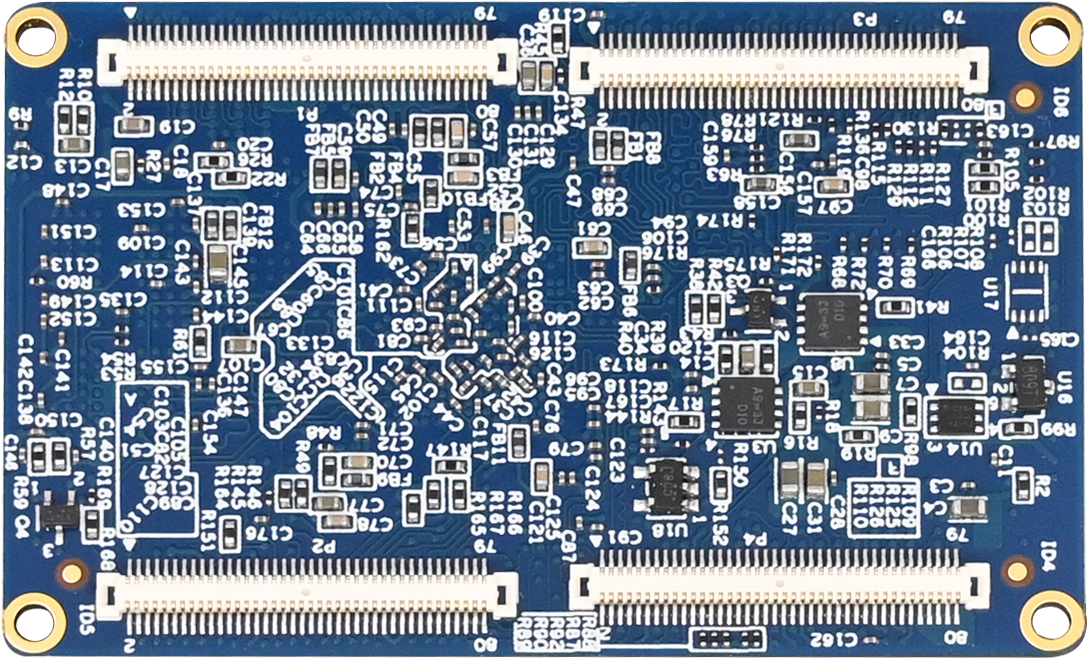

FET62xx-C SoM Appearance:

Front

Back

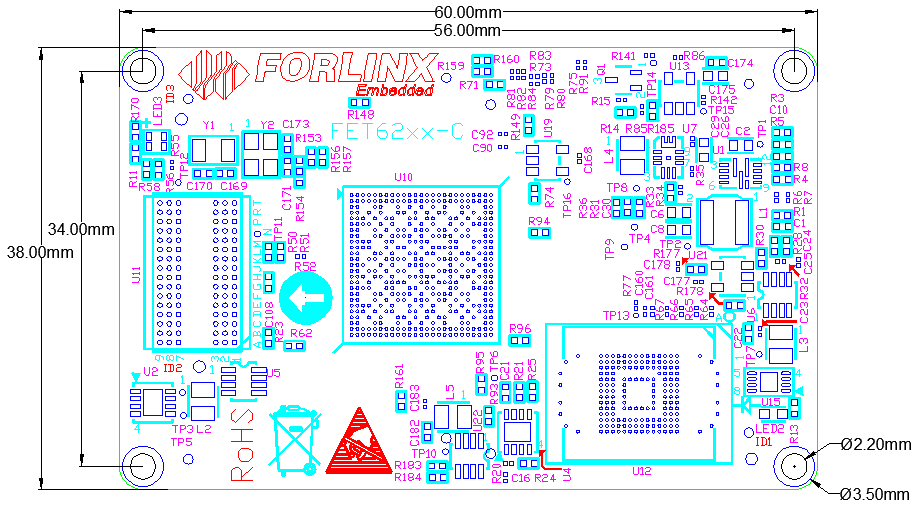

2.2 FET62xx-C SoM Dimension Diagram

Top

Bottom

Structure size: 60mm × 38mm, size tolerance ± 0.13mm, single side of burr tolerance ± 0.2mm.

Plate making process: 1.6mm thickness, 10-layer immersion gold PCB.

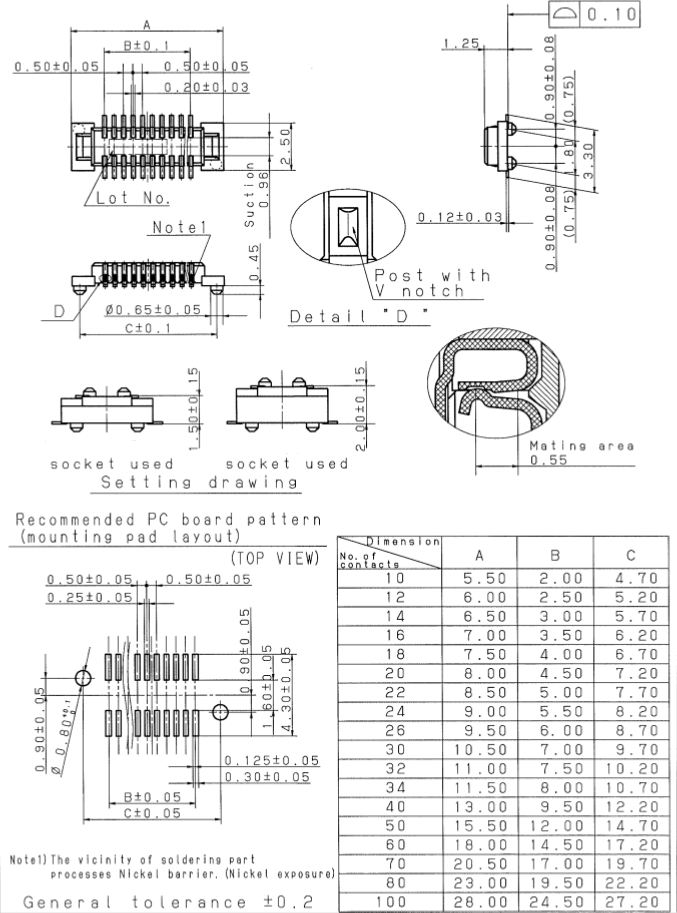

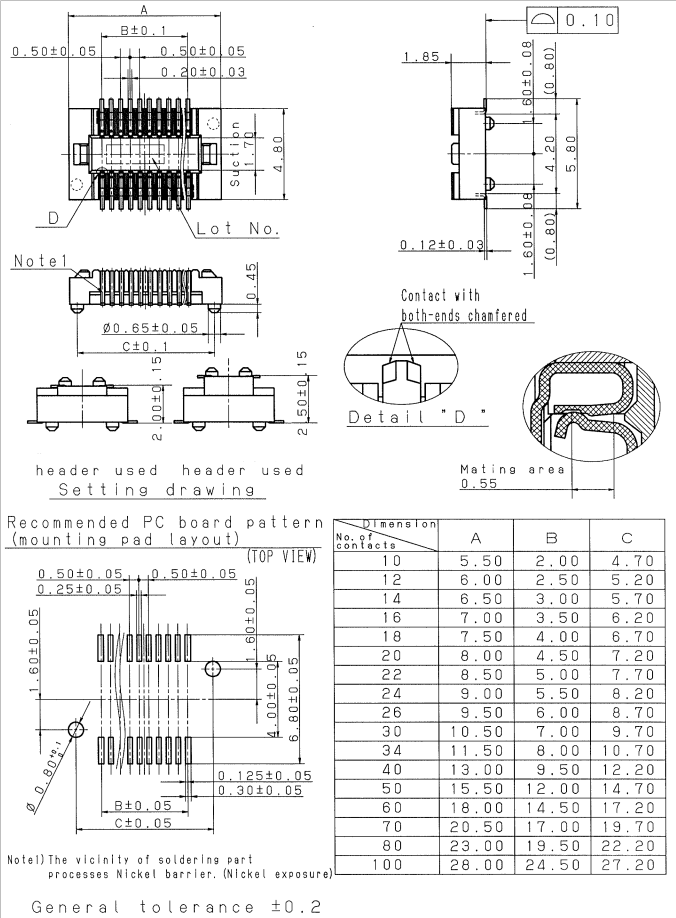

Connector: Four 0.5mm pitch, 80pin board-to-board connectors. Refer to Appendix for the connector dimension diagram.

Four mounting holes (2.2mm) are reserved at the four corners of the SoM to facilitate the installation of fixing screws and to improve the reliability of the product connection so that the product can be used in vibration environments.

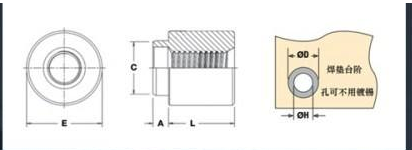

Please refer to the development board design and use SMT nuts of M2 with a length (L) of 2 mm on the carrier board. Please refer to the following figure for the specifications of the SMT nuts.

2.3 SoM Configuration Resources

2.3.1 SoM Naming Rules

A-B-C+DEFGHIJ:KL-M

Field |

Field Description |

Value |

Description |

|---|---|---|---|

A |

Product Line Identification |

FET |

Forlinx Embedded SoM |

- |

Segment Identification |

- |

When the first digit of the CPU value is a letter, connect the product line identifier to the CPU with “-”; when the first digit of the CPU value is a number, omit “-“. |

B |

CPU Name |

62xx |

AM6254, AM6231, AM6232 |

- |

Segment Identification |

- |

Parameter segment sign |

C |

Connection |

C |

Board to Board Connector |

+ |

Segment Identification |

+ |

The configuration parameter section follows this identifier. |

D |

CPU Clock |

14 |

1.4 GHz (AM6231 clock 1.0GHZ) |

E |

RAM capacity |

1G/2G |

1G/2G |

F |

Single ROM Type |

SE |

eMMC |

G |

ROM capacity |

8G |

8GB |

H |

Operating Temperature |

I |

-40 to 85℃ industrial level |

I |

Configuration No. |

A~Z |

If the D~H field values are the same for each product, then this field has the same value. It is in ascending order according to the configuration release time. |

J |

PCB Version |

12 |

V1.2 |

: |

Separator |

: |

It’s followed by the manufacture’s internal identification. |

K |

Chip Type |

A~Z |

This is the internal identification of the manufacturer and has no impact on the use. |

L |

Connector origin |

1 |

Imported connector |

2.3.2 Order Information

No. |

Specification Model |

CPU Clock |

RAM |

ROM |

Temperature Level |

|---|---|---|---|---|---|

A |

FET6254-C+141GSE8GIA12 |

1.4 GHZ |

1G |

8G |

Industrial-grade |

B |

FET6254-C+142GSE8GIB12 |

1.4 GHZ |

2G |

8G |

Industrial-grade |

A |

FET6232-C+142GSE8GIA12 |

1.4 GHZ |

2G |

8G |

Industrial-grade |

B |

FET6232-C+141GSE8GIB12 |

1.4 GHZ |

1G |

8G |

Industrial-grade |

A |

FET6231-C+101GSE8GIA12 |

1.0 GHZ |

1G |

8G |

Industrial-grade |

This table shows examples of the SoM specifications and models, but it does not cover all possible specifications. The latest specifications and models can be found in the latest product hardware manual. If the specifications you need are not listed in the table, or if you have any questions about the specifications, please visit www.forlinx.net or contact your Forlinx sales representative.

2.4 Performance Parameters

2.4.1 System Main Frequency

Name |

Specification |

Description |

|||

|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

||

System clock Arm ® Cortex ® -53 |

— |

— |

1400 |

MHz |

— |

System clock y Arm® Cortex®-M4F |

— |

— |

400 |

MHz |

|

RTC clock |

— |

32.768 |

— |

KHz |

— |

AM6231 system clock is up to 1000MHZ

2.4.2 Power Parameter

Parameter |

Pin Number |

Specification |

Description |

|||

|---|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

|||

Main Power Supply Voltage |

ACIN |

4.5 |

5 |

5.5 |

V |

2.4.3 Operating Environment

Parameter |

Specification |

Description |

||||

|---|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

|||

Operating Temperature |

Operating Environment |

-40 |

25 |

85 |

℃ |

Industrial-grade |

Storage Environment |

-40 |

25 |

85 |

℃ |

||

Humidity |

Operating Environment |

10 |

— |

90 |

%RH |

No condensation |

Storage Environment |

5 |

— |

95 |

%RH |

2.4.4 SoM Interface Speed

Parameter |

Specification |

Description |

|||

|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

||

Serial Port Communication Speed |

— |

115200 |

3.6M |

bps |

— |

SPI Clock Frequncey |

— |

— |

50 |

MHz |

— |

I2C Communication Speed |

— |

100 |

400 |

Kbps |

— |

USB interface speed |

— |

— |

480 |

Mbps |

— |

CAN-FD Communication speed |

— |

— |

5 |

Mbps |

— |

2.5 SoM Interface Speed

Function |

Quantity |

Parameter |

|---|---|---|

LVDS12 |

2 |

2 x 4-lane LVDS display serial interfaces supporting up to 1.19 Gbps per lane; |

RGB Parallel |

1 |

1 x 24bit RGB parallel display interface, up to WUXGA (1920 X 1200 @ 60fps, |

MIPI CSI |

1 |

One 4-lane MIPI camera serial interface MIPI-DPHY 1.2; |

Ethernet |

2 |

Supports RMII(10/100)or RGMII (10/100/1000); |

USB |

2 |

USB 2.0 (up to 480 Mbps); |

UART*3 |

≤9 |

Compatible with 16C750; |

SPI*4 |

≤5 |

Serial clock with programmable frequency, polarity, and phase per channel; |

I2C*5 |

≤6 |

Supports standard-mode (up to 100Kbps) and fast-mode (up to 400Kbps); |

Audio |

≤3 |

Send and receive clocks up to 50MHz; |

ePWM |

≤3 |

Each set of PWM supports two PWM outputs (EPWMxA and EPWMxB) for |

eQEP |

≤3 |

Enhanced Quadrature Encoder Pulse Input; |

eCAP |

≤3 |

The enhanced capture module can be used for: |

CAN-FD*6 |

≤3 |

Complies with CAN2.0a, B or ISO 11898 -1 protocols; |

SD |

≤2 |

Supports 2 x 4-bit SD/SDIO interfaces up to UHS-I; |

GPMC |

1 |

Clock speeds up to 133MHz; |

OSPI/QSPI |

1 |

Supports 166MHz DDR/200MHz SDR mode |

JTAG |

1 |

Supports JTAG interface |

Note: The interface number listed in the table is the hardware design or CPU theoretical maximum quantity, and most of the function pins are multiplexed. Please refer to the PinMux table for easy configuration.

A single LVDS interface can support WUXGA (1920x1200@60p, 162MHz pixel clock). It requires that the receiving display or link bridging device can accept the video output of the device through a single LVDS link. Normally, single - link interfaces are only used for display resolutions smaller than 1366 x 768. In the dual - link mode, the second interface does not increase the available bandwidth but reduces the required pixel clock by half;

It can support 1 x 2048x1080 + 1 x 1280x720;

7 x out of the 9 x UART are resources in the main domain, and the other 2 x are resources in the MCU domain. The names of the MCU - domain UARTs are: WKUP_UART0 and MCU_UART0;

3 x out of the 5 x SPI are resources in the main domain, and the other 2 x are resources in the MCU domain;

2 x out of the 6 x I2C are resources in the main domain, and the other 2 x are resources in the MCU domain;

1 x out of the 3 x CAN FD is a resource in the main domain, and the other 2 x are resources in the MCU domain;

The AM6231 SoM has a single - core A53 and no 3D Graphics Engine;

The AM6232 SoM has a dual - core A53 and no 3D Graphics Engine.

2.6 FET62xx SoM Pins Definition

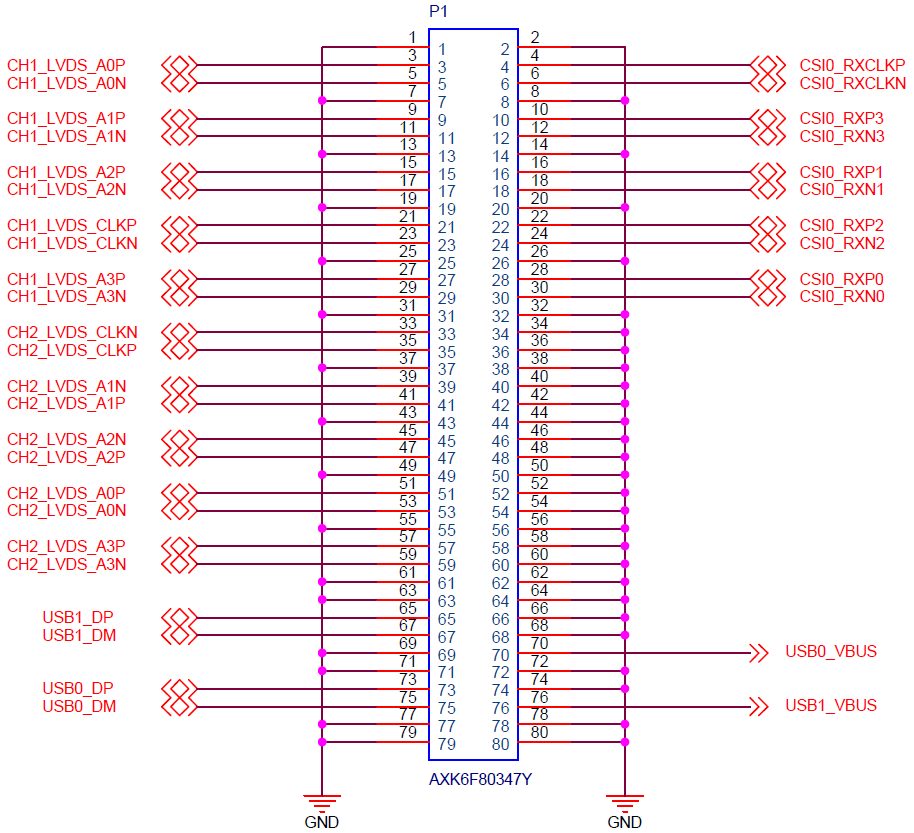

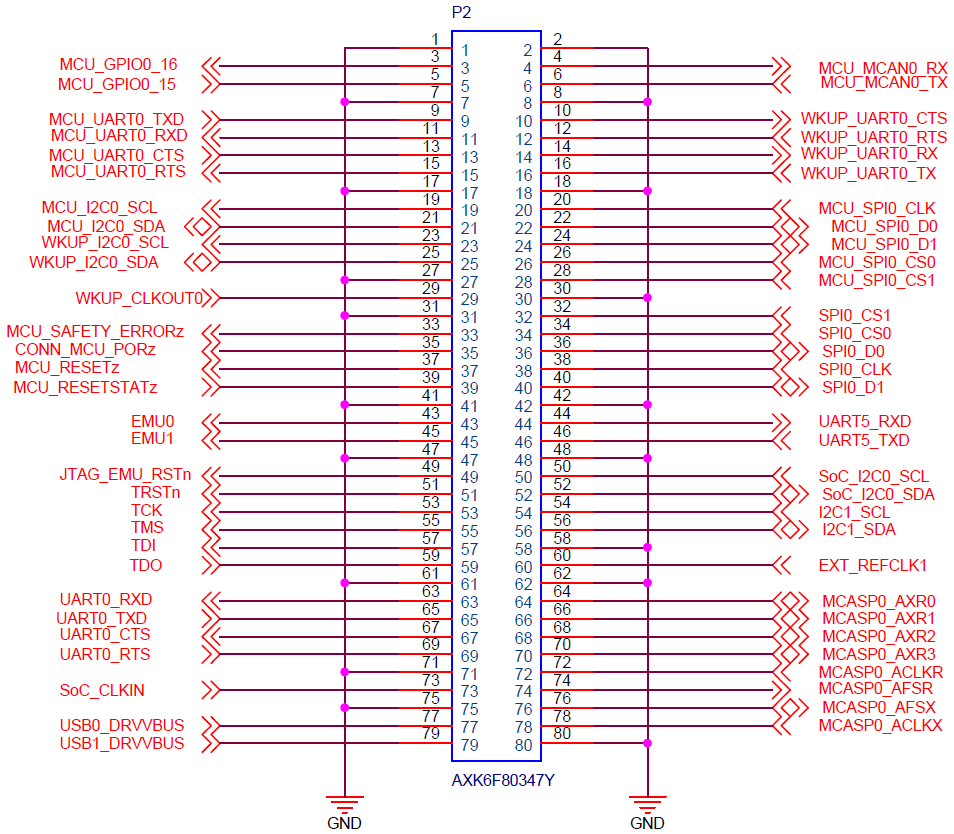

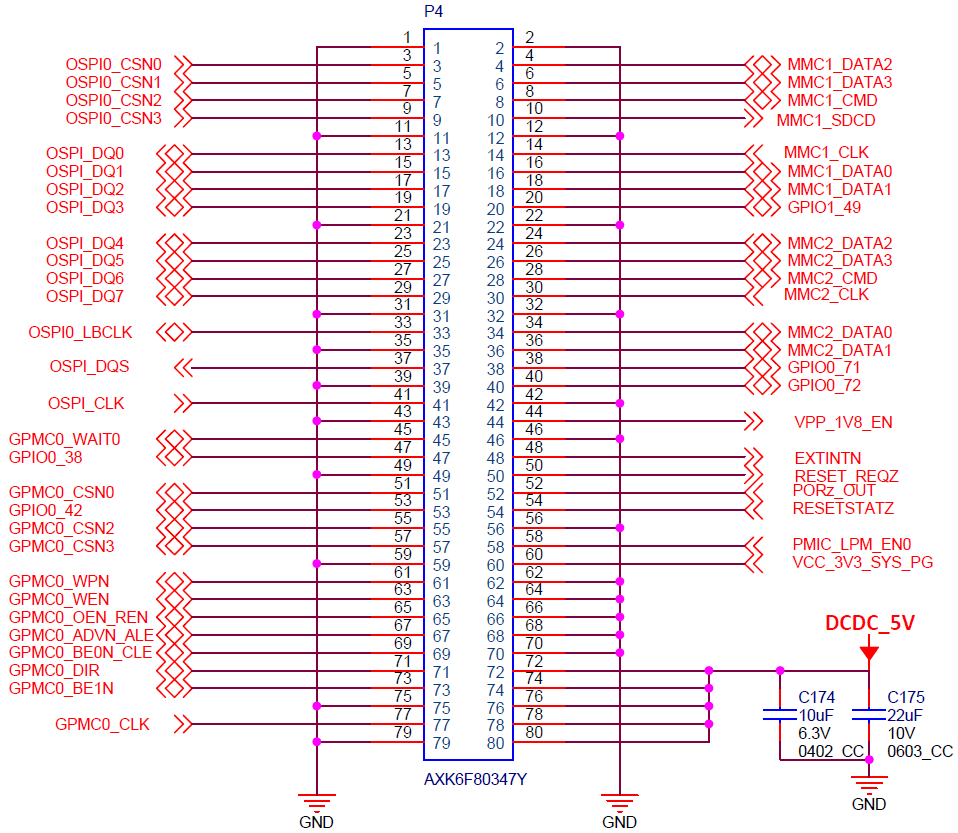

2.6.1 FET62xx SoM Pins Schematic

FET62xx-C SoM Pins Schematic are as follows:

2.6.2 FET62xx SoM Pin Functions Description

Note1:

Num ——SoM connector pin no.:

Ball —— CPU pin ball no.

GPIO ——CPU pin general I/O port serial number

Vol ——Pin signal level

Note2:

Signal Name——SoM connector network name, the top right corner subscripts’ meaning are as follows:

Superscript No. |

Superscript Description |

|---|---|

[1] |

Pins can be configured for interrupt use. |

[2] |

The default pin level is 1.8 V. |

[3] |

Pins are CPU boot-related pins, which are not recommended for IO. |

[4] |

Special-purpose pins and can not be used as IO. |

Pin Description—— SoM Pin Signal Descriptions

Default function-All pin functions of the SoM are specified according to the “default function” in the table below. Please do not modify it, otherwise it may be delivered from the factory.

Drive conflict. If you have any questions, please contact our sales or technical support.

Note3: The pins marked as “Do not use on carrier board” in the “Default Function” column are those already utilized by the core board and should not be used in the design of the baseboard.

Table 1 LEFT_UP(P1) Connector Interface(Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

- |

GND |

- |

- |

Ground |

GND |

3 |

- |

CH1_LVDS_A0P |

- |

- |

CH1_LVDS data A0+ |

CH1_LVDS_A0P |

5 |

- |

CH1_LVDS_A0N |

- |

- |

CH1_LVDS data A0- |

CH1_LVDS_A0N |

7 |

- |

GND |

- |

- |

Ground |

GND |

9 |

- |

CH1_LVDS_A1P |

- |

- |

CH1_LVDS data A1+ |

CH1_LVDS_A1P |

11 |

- |

CH1_LVDS_A1N |

- |

- |

CH1_LVDS data A1- |

CH1_LVDS_A1N |

13 |

- |

GND |

- |

- |

Ground |

GND |

15 |

- |

CH1_LVDS_A2P |

- |

- |

CH1_LVDS data A2+ |

CH1_LVDS_A2P |

17 |

- |

CH1_LVDS_A2N |

- |

- |

CH1_LVDS data A2- |

CH1_LVDS_A2N |

19 |

- |

GND |

- |

- |

Ground |

GND |

21 |

- |

CH1_LVDS_CLKP |

- |

- |

CH1_LVDS clock+ |

CH1_LVDS_CLKP |

23 |

- |

CH1_LVDS_CLKN |

- |

- |

CH1_LVDS clock- |

CH1_LVDS_CLKN |

25 |

- |

GND |

- |

- |

Ground |

GND |

27 |

- |

CH1_LVDS_A3P |

- |

- |

CH1_LVDS data A3+ |

CH1_LVDS_A3P |

29 |

- |

CH1_LVDS_A3N |

- |

- |

CH1_LVDS data A3- |

CH1_LVDS_A3N |

31 |

- |

GND |

- |

- |

Ground |

GND |

33 |

- |

CH2_LVDS_CLKN |

- |

- |

CH2_LVDS clock- |

CH2_LVDS_CLKN |

35 |

- |

CH2_LVDS_CLKP |

- |

- |

CH2_LVDS clock+ |

CH2_LVDS_CLKP |

37 |

- |

GND |

- |

- |

Ground |

GND |

39 |

- |

CH2_LVDS_A1N |

- |

- |

CH2_LVDS data A1- |

CH2_LVDS_A1N |

41 |

- |

CH2_LVDS_A1P |

- |

- |

CH2_LVDS data A1+ |

CH2_LVDS_A1P |

43 |

- |

GND |

- |

- |

Ground |

GND |

45 |

- |

CH2_LVDS_A2N |

- |

- |

CH2_LVDS data A2- |

CH2_LVDS_A2N |

47 |

- |

CH2_LVDS_A2P |

- |

- |

CH2_LVDS data A2+ |

CH2_LVDS_A2P |

49 |

- |

GND |

- |

- |

Ground |

GND |

51 |

- |

CH2_LVDS_A0P |

- |

- |

CH2_LVDS data A0+ |

CH2_LVDS_A0P |

53 |

- |

CH2_LVDS_A0N |

- |

- |

CH2_LCDS data A0- |

CH2_LVDS_A0N |

55 |

- |

GND |

- |

- |

Ground |

GND |

57 |

- |

CH2_LVDS_A3P |

- |

- |

CH2_LVDS data A3+ |

CH2_LVDS_A3P |

59 |

- |

CH2_LVDS_A3N |

- |

- |

CH2_LVDS data A3- |

CH2_LVDS_A3N |

61 |

- |

GND |

- |

- |

Ground |

GND |

63 |

- |

GND |

- |

- |

Ground |

GND |

65 |

- |

USB1_DP |

- |

- |

USB1 data+ |

USB1_DP |

67 |

- |

USB1_DM |

- |

- |

USB1 data- |

USB1_DM |

69 |

- |

GND |

- |

- |

Ground |

GND |

71 |

- |

GND |

- |

- |

Ground |

GND |

73 |

- |

USB0_DP |

- |

- |

USB0 data+ |

USB0_DP |

75 |

- |

USB0_DM |

- |

- |

USB0 data- |

USB0_DM |

77 |

- |

GND |

- |

- |

Ground |

GND |

79 |

- |

GND |

- |

- |

Ground |

GND |

Table 2 LEFT_UP(P1) Connector Interface(Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

- |

CSI0_RXCLKP |

- |

- |

MIPI_CSI0 Receiving clock+ |

CSI0_RXCLKP |

6 |

- |

CSI0_RXCLKN |

- |

- |

MIPI_CSI0 Receiving clock- |

CSI0_RXCLKN |

8 |

- |

GND |

- |

- |

Ground |

GND |

10 |

- |

CSI0_RXP3 |

- |

- |

MIPI_CSI0 Receiving data 3+ |

CSI0_RXP3 |

12 |

- |

CSI0_RXN3 |

- |

- |

MIPI_CSI0 Receiving data 3- |

CSI0_RXN3 |

14 |

- |

GND |

- |

- |

Ground |

GND |

16 |

- |

CSI0_RXP1 |

- |

- |

MIPI_CSI0 Receiving data1+ |

CSI0_RXP1 |

18 |

- |

CSI0_RXN1 |

- |

- |

MIPI_CSI0 Receiving data1- |

CSI0_RXN1 |

20 |

- |

GND |

- |

- |

Ground |

GND |

22 |

- |

CSI0_RXP2 |

- |

- |

MIPI_CSI0 Receiving data 2+ |

CSI0_RXP2 |

24 |

- |

CSI0_RXN2 |

- |

- |

MIPI_CSI0 Receiving data 2- |

CSI0_RXN2 |

26 |

- |

GND |

- |

- |

Ground |

GND |

28 |

- |

CSI0_RXP0 |

- |

- |

MIPI_CSI0 Receiving data 0+ |

CSI0_RXP0 |

30 |

- |

CSI0_RXN0 |

- |

- |

MIPI_CSI0 Receiving data 0- |

CSI0_RXN0 |

32 |

- |

GND |

- |

- |

Ground |

GND |

34 |

- |

GND |

- |

- |

Ground |

GND |

36 |

- |

GND |

- |

- |

Ground |

GND |

38 |

- |

GND |

- |

- |

Ground |

GND |

40 |

- |

GND |

- |

- |

Ground |

GND |

42 |

- |

GND |

- |

- |

Ground |

GND |

44 |

- |

GND |

- |

- |

Ground |

GND |

46 |

- |

GND |

- |

- |

Ground |

GND |

48 |

- |

GND |

- |

- |

Ground |

GND |

50 |

- |

GND |

- |

- |

Ground |

GND |

52 |

- |

GND |

- |

- |

Ground |

GND |

54 |

- |

GND |

- |

- |

Ground |

GND |

56 |

- |

GND |

- |

- |

Ground |

GND |

58 |

- |

GND |

- |

- |

Ground |

GND |

60 |

- |

GND |

- |

- |

Ground |

GND |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

- |

GND |

- |

- |

Ground |

GND |

66 |

- |

GND |

- |

- |

Ground |

GND |

68 |

- |

GND |

- |

- |

Ground |

GND |

70 |

- |

USB0_VBUS |

- |

1.8V |

USB0_VBUS detection input |

USB0_VBUS |

72 |

- |

GND |

- |

- |

Ground |

GND |

74 |

- |

GND |

- |

- |

Ground |

GND |

76 |

- |

USB1_VBUS |

- |

1.8V |

USB1_VBUS detection input |

USB1_VBUS |

78 |

- |

GND |

- |

- |

Ground |

GND |

80 |

- |

GND |

- |

- |

Ground |

GND |

Table 3 RIGHT_UP(P2) Connector Interface(Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

- |

GND |

- |

- |

Ground |

GND |

3 |

D4 |

MCU_GPIO0_16 |

MCU_GPIO0_16 |

3.3V |

MCU domain GPIO0_16 |

MCU_GPIO0_16 |

5 |

E5 |

MCU_GPIO0_15 |

MCU_GPIO0_16 |

3.3V |

MCU domain GPIO0_15 |

MCU_GPIO0_15 |

7 |

- |

GND |

- |

- |

Ground |

GND |

9 |

A5 |

MCU_UART0_TXD |

MCU_GPIO0_6 |

3.3V |

MCU domain UART0 send |

MCU_UART0_TXD |

11 |

B5 |

MCU_UART0_RXD |

MCU_GPIO0_5 |

3.3V |

MCU domain UART0 receive |

MCU_UART0_RXD |

13 |

A6 |

MCU_UART0_CTS |

MCU_GPIO0_7 |

3.3V |

MCU domain UART0 clear to send (active low) |

MCU_GPIO0_7 |

15 |

B6 |

MCU_UART0_RTS |

MCU_GPIO0_8 |

3.3V |

MCU domain UART0 request to send (active low) |

MCU_GPIO0_8 |

17 |

- |

GND |

- |

- |

Ground |

GND |

19 |

A8 |

MCU_I2C0_SCL |

MCU_GPIO0_17 |

3.3V |

MCU domain I2C0 clock |

MCU_I2C0_SCL |

21 |

D10 |

MCU_I2C0_SDA |

MCU_GPIO0_18 |

3.3V |

MCU domain I2C0 data |

MCU_I2C0_SDA |

23 |

B9 |

WKUP_I2C0_SCL |

MCU_GPIO0_19 |

3.3V |

WKUP domain I2C0 clock |

WKUP_I2C0_SCL |

25 |

A9 |

WKUP_I2C0_SDA |

MCU_GPIO0_20 |

3.3V |

WKUP domain I2C0 data |

WKUP_I2C0_SDA |

27 |

- |

GND |

- |

- |

Ground |

GND |

29 |

A12 |

WKUP_CLKOUT0 |

MCU_GPIO0_23 |

3.3V |

WKUP domain CLKOUT0 output |

WKUP_CLKOUT0 |

31 |

- |

GND |

- |

- |

Ground |

GND |

33 |

- |

MCU_SAFETY_ERRORZ |

- |

1.8V |

MCU domain ESM error signal output |

MCU_SAFETY_ERRORZ |

35 |

- |

CONN_MCU_PORZ |

- |

3.3V |

MCU domain cold reset input |

CONN_MCU_PORZ |

37 |

- |

MCU_RESETZ |

- |

3.3V |

MCU domain warm reset input |

MCU_RESETZ |

39 |

- |

MCU_RESETSTATZ |

- |

3.3V |

MCU domain hot reset status output |

MCU_RESETSTATZ |

41 |

- |

GND |

- |

- |

Ground |

GND |

43 |

- |

EMU0 |

- |

3.3V |

Simulation control 0 |

EMU0 |

45 |

- |

EMU1 |

- |

3.3V |

Simulation control 1 |

EMU1 |

47 |

- |

GND |

- |

- |

Ground |

GND |

49 |

- |

JTAG_EMU_RSTN |

- |

3.3V |

JTAG_EMU cold reset |

JTAG_EMU_RSTN |

51 |

B10 |

TRSTN |

- |

3.3V |

JTAG reset |

TRSTN |

53 |

A10 |

TCK |

- |

3.3V |

JTAG test clock input |

TCK |

55 |

B11 |

TMS |

- |

3.3V |

JTAG test mode selection input |

TMS |

57 |

A11 |

TDI |

- |

3.3V |

JTAG test data input |

TDI |

59 |

D12 |

TDO |

- |

3.3V |

JTAG test data output |

TDO |

61 |

- |

GND |

- |

- |

Ground |

GND |

63 |

D14 |

UART0_RXD |

GPIO1_20 |

3.3V |

Main domain UART0 receive |

UART0_RXD |

65 |

E14 |

UART0_TXD |

GPIO1_21 |

3.3V |

Main domain UART0 send |

UART0_TXD |

67 |

A15 |

UART0_CTS |

GPIO1_22 |

3.3V |

Main domain UART0 clear sending(active low) |

GPIO1_22 |

69 |

B15 |

UART0_RTS |

GPIO1_23 |

3.3V |

Main domain UART0 request to send (active low) |

AUDIO_EXT_REFCLK1 |

71 |

- |

GND |

- |

- |

Ground |

GND |

73 |

- |

SOC_CLKIN |

- |

1.8V |

SoM clock input (floating by default) |

SOC_CLKIN |

75 |

- |

GND |

- |

- |

Ground |

GND |

77 |

- |

USB0_DRVVBUS |

- |

3.3V |

USB0 VBUS control output |

USB0_DRVVBUS |

79 |

- |

USB1_DRVVBUS |

- |

3.3V |

USB1 VBUS control output |

USB1_DRVVBUS |

Table 4 RIGHT_UP(P2) Connector Interface(Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

B3 |

MCU_MCAN0_RX |

MCU_GPIO0_14 |

3.3V |

MCU domain CAN0 receive |

MCU_MCAN0_RX |

6 |

D6 |

MCU_MCAN0_TX |

MCU_GPIO0_13 |

3.3V |

MCU domain CAN0 send |

MCU_MCAN0_TX |

8 |

- |

GND |

- |

- |

Ground |

GND |

10 |

C6 |

WKUP_UART0_CTS |

MCU_GPIO0_11 |

3.3V |

WKUP domain UART0 clear sending |

MCU_GPIO0_11 |

12 |

A4 |

WKUP_UART0_RTS |

MCU_GPIO0_12 |

3.3V |

WKUP domain UART0 request to send |

MCU_GPIO0_12 |

14 |

B4 |

WKUP_UART0_RX |

MCU_GPIO0_9 |

3.3V |

WKUP domain UART0 receive |

WKUP_UART0_RX |

16 |

C5 |

WKUP_UART0_TX |

MCU_GPIO0_10 |

3.3V |

WKUP domain UART0 send |

WKUP_UART0_TX |

18 |

- |

GND |

- |

- |

Ground |

GND |

20 |

A7 |

MCU_SPI0_CLK |

MCU_GPIO0_2 |

3.3V |

MCU domain SPI0 clock |

MCU_SPI0_CLK |

22 |

D9 |

MCU_SPI0_D0 |

MCU_GPIO0_3 |

3.3V |

MCU domain SPI0 data 0 |

MCU_SPI0_D0 |

24 |

C9 |

MCU_SPI0_D1 |

MCU_GPIO0_4 |

3.3V |

MCU domain SPI0 data 1 |

MCU_SPI0_D1 |

26 |

E8 |

MCU_SPI0_CS0 |

MCU_GPIO0_0 |

3.3V |

MCU domain SPI0 chip selection 0 |

MCU_SPI0_CS0 |

28 |

B8 |

MCU_SPI0_CS1 |

MCU_GPIO0_1 |

3.3V |

MCU domain SPI0 chip selection 1 |

MCU_SPI0_CS1 |

30 |

- |

GND |

- |

- |

Ground |

GND |

32 |

C13 |

SPI0_CS1 |

GPIO1_16 |

3.3V |

Main domain SPI0 chip selection 1 |

GPIO1_16 |

34 |

A13 |

SPI0_CS0 |

GPIO1_15 |

3.3V |

Main domain SPI0 chip selection 0 |

GPIO1_15 |

36 |

B13 |

SPI0_D0 |

GPIO1_18 |

3.3V |

Main domain SPI0 data 0 |

GPIO1_18 |

38 |

A14 |

SPI0_CLK |

GPIO1_17 |

3.3V |

Main domain SPI0 clock |

GPIO1_17 |

40 |

B14 |

SPI0_D1 |

GPIO1_19 |

3.3V |

Main domain SPI0 data 1 |

GPIO1_19 |

42 |

- |

GND |

- |

- |

Ground |

GND |

44 |

C15 |

UART5_RXD |

GPIO1_24 |

3.3V |

Main domain UART5 receive |

UART5_RXD |

46 |

E15 |

UART5_TXD |

GPIO1_25 |

3.3V |

Main domain UART5 send |

UART5_TXD |

48 |

- |

GND |

- |

- |

Ground |

GND |

50 |

B16 |

SOC_I2C0_SCL |

GPIO1_26 |

3.3V |

Main domain I2C0 clock |

SOC_I2C0_SCL |

52 |

A16 |

SOC_I2C0_SDA |

GPIO1_27 |

3.3V |

Main domain I2C0 data |

SOC_I2C0_SDA |

54 |

B17 |

I2C1_SCL |

GPIO1_28 |

3.3V |

Main domain I2C1 clock |

I2C1_SCL |

56 |

A17 |

I2C1_SDA |

GPIO1_29 |

3.3V |

Main domain I2C1 data |

I2C1_SDA |

58 |

- |

GND |

- |

- |

Ground |

GND |

60 |

- |

EXT_REFCLK1 |

- |

3.3V |

External clock input to the Main domain |

EXT_REFCLK1 |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

E18 |

MCASP0_AXR0 |

GPIO1_10 |

3.3V |

MCASP0 serial data 0 |

LCD_PWM |

66 |

B18 |

MCASP0_AXR1 |

GPIO1_9 |

3.3V |

MCASP0 serial data 1 |

LVDS_PWM |

68 |

A19 |

MCASP0_AXR2 |

GPIO1_8 |

3.3V |

MCASP0 serial data 2 |

MCASP0_AXR2 |

70 |

B19 |

MCASP0_AXR3 |

GPIO1_7 |

3.3V |

MCASP0 serial data 3 |

MCASP0_AXR3 |

72 |

A20 |

MCASP0_ACLKR |

GPIO1_14 |

3.3V |

MCASP0 receive bit reference clock |

MCASP0_ACLKR |

74 |

E19 |

MCASP0_AFSR |

GPIO1_13 |

3.3V |

MCASP0 receives the frame sync |

MCASP0_AFSR |

76 |

D20 |

MCASP0_AFSX |

GPIO1_12 |

3.3V |

MCASP0 send bit reference clock |

MCASP0_AFSX |

78 |

B20 |

MCASP0_ACLKX |

GPIO1_11 |

3.3V |

MCASP0 sends frame sync |

MCASP0_ACLKX |

80 |

- |

GND |

- |

- |

Ground |

GND |

Table 5 LEFT _ DOWN (P3) Connector Interface (Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

- |

GND |

- |

- |

Ground |

GND |

3 |

AC25 |

VOUT0_VSYNC |

GPIO0_63 |

3.3V |

Vertical synchronization of video output |

VOUT0_VSYNC |

5 |

AB24 |

VOUT0_HSYNC |

GPIO0_61 |

3.3V |

Horizontal synchronization of video output |

VOUT0_HSYNC |

7 |

Y20 |

VOUT0_DE |

GPIO0_62 |

3.3V |

Enable video output data |

VOUT0_DE |

9 |

- |

GND |

- |

- |

Ground |

GND |

11 |

AD24 |

CPSW_RGMII2_MDC |

GPIO0_86 |

3.3V |

MDIO clock |

CPSW_RGMII2_MDC |

13 |

AB22 |

CPSW_RGMII2_MDIO |

GPIO0_85 |

3.3V |

MDIO data |

CPSW_RGMII2_MDIO |

15 |

- |

GND |

- |

- |

Ground |

GND |

17 |

AD17 |

CPSW_RGMII1_RXC |

GPIO0_80 |

3.3V |

RGMII1 Receiving clock- |

CPSW_RGMII1_RXC |

19 |

AE17 |

CPSW_RGMII1_RX_CTL |

GPIO0_79 |

3.3V |

RGMII1 receiving control |

CPSW_RGMII1_RX_CTL |

21 |

- |

GND |

- |

- |

Ground |

GND |

23 |

AB17 |

CPSW_RGMII1_RD0 |

GPIO0_81 |

3.3V |

RGMII1 receive data 0 |

CPSW_RGMII1_RD0 |

25 |

AC17 |

CPSW_RGMII1_RD1 |

GPIO0_82 |

3.3V |

RGMII1 receive data 1 |

CPSW_RGMII1_RD1 |

27 |

AB16 |

CPSW_RGMII1_RD2 |

GPIO0_83 |

3.3V |

RGMII1 receive data 2 |

CPSW_RGMII1_RD2 |

29 |

AA15 |

CPSW_RGMII1_RD3 |

GPIO0_84 |

3.3V |

RGMII1 receive data 3 |

CPSW_RGMII1_RD3 |

31 |

- |

GND |

- |

- |

Ground |

GND |

33 |

AE19 |

CPSW_RGMII1_TXC |

GPIO0_74 |

3.3V |

RGMII1 clock sending |

CPSW_RGMII1_TXC |

35 |

AD19 |

CPSW_RGMII1_TX_CTL |

GPIO0_73 |

3.3V |

RGMII1 sending control |

CPSW_RGMII1_TX_CTL |

37 |

- |

GND |

- |

- |

Ground |

GND |

39 |

AE20 |

CPSW_RGMII1_TD0 |

GPIO0_75 |

3.3V |

RGMII1 sends data 0 |

CPSW_RGMII1_TD0 |

41 |

AD20 |

CPSW_RGMII1_TD1 |

GPIO0_76 |

3.3V |

RGMII1 sends data 1 |

CPSW_RGMII1_TD1 |

43 |

AE18 |

CPSW_RGMII1_TD2 |

GPIO0_77 |

3.3V |

RGMII1 sends data 2 |

CPSW_RGMII1_TD2 |

45 |

AD18 |

CPSW_RGMII1_TD3 |

GPIO0_78 |

3.3V |

RGMII1_send data 3 |

CPSW_RGMII1_TD3 |

47 |

- |

GND |

- |

- |

Ground |

GND |

49 |

AD23 |

CPSW_RGMII2_RXC |

GPIO1_2 |

3.3V |

RGMII2 Receiving clock- |

CPSW_RGMII2_RXC |

51 |

AD22 |

CPSW_RGMII2_RX_CTL |

GPIO1_1 |

3.3V |

RGMII2 receiving control |

CPSW_RGMII2_RX_CTL |

53 |

- |

GND |

- |

- |

Ground |

GND |

55 |

AE23 |

CPSW_RGMII2_RD0 |

GPIO1_3 |

3.3V |

RGMII2 receive data 0 |

CPSW_RGMII2_RD0 |

57 |

AB20 |

CPSW_RGMII2_RD1 |

GPIO1_4 |

3.3V |

RGMII2 receive data 1 |

CPSW_RGMII2_RD1 |

59 |

AC21 |

CPSW_RGMII2_RD2 |

GPIO1_5 |

3.3V |

RGMII2 receive data 2 |

CPSW_RGMII2_RD2 |

61 |

AE22 |

CPSW_RGMII2_RD3 |

GPIO1_6 |

3.3V |

RGMII2 receive data 3 |

CPSW_RGMII2_RD3 |

63 |

- |

GND |

- |

- |

Ground |

GND |

65 |

AE21 |

CPSW_RGMII2_TXC |

GPIO0_88 |

3.3V |

RGMII2 clock sending |

CPSW_RGMII2_TXC |

67 |

AA19 |

CPSW_RGMII2_TX_CTL |

GPIO0_87 |

3.3V |

RGMII2 sending control |

CPSW_RGMII2_TX_CTL |

69 |

- |

GND |

- |

- |

Ground |

GND |

71 |

Y18 |

CPSW_RGMII2_TD0 |

GPIO0_89 |

3.3V |

RGMII2 sends data 0 |

CPSW_RGMII2_TD0 |

73 |

AA18 |

CPSW_RGMII2_TD1 |

GPIO0_90 |

3.3V |

RGMII2 sends data 1 |

CPSW_RGMII2_TD1 |

75 |

AD21 |

CPSW_RGMII2_TD2 |

GPIO0_91 |

3.3V |

RGMII2 sends data 2 |

CPSW_RGMII2_TD2 |

77 |

AC20 |

CPSW_RGMII2_TD3 |

GPIO1_0 |

3.3V |

RGMII2 sends data 3 |

CPSW_RGMII2_TD3 |

79 |

- |

GND |

- |

- |

Ground |

GND |

Table 6 LEFT _ DOWN (P3) Connector Interface (Even) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

AC24 |

VOUT0_PCLK |

GPIO0_64 |

3.3V |

Video output pixel clock |

VOUT0_PCLK |

6 |

- |

GND |

- |

- |

Ground |

GND |

8 |

- |

GND |

- |

- |

Ground |

GND |

10 |

U22 |

VOUT0_DATA0 |

GPIO0_45 |

3.3V |

Video output data 0 |

VOUT0_DATA0 |

12 |

V24 |

VOUT0_DATA1 |

GPIO0_46 |

3.3V |

Video output data 1 |

VOUT0_DATA1 |

14 |

W25 |

VOUT0_DATA2 |

GPIO0_47 |

3.3V |

Video output data 2 |

VOUT0_DATA2 |

16 |

W24 |

VOUT0_DATA3 |

GPIO0_48 |

3.3V |

Video output data 3 |

VOUT0_DATA3 |

18 |

Y25 |

VOUT0_DATA4 |

GPIO0_49 |

3.3V |

Video output data 4 |

VOUT0_DATA4 |

20 |

Y24 |

VOUT0_DATA5 |

GPIO0_50 |

3.3V |

Video output data 5 |

VOUT0_DATA5 |

22 |

Y23 |

VOUT0_DATA6 |

GPIO0_51 |

3.3V |

Video output data 6 |

VOUT0_DATA6 |

24 |

AA25 |

VOUT0_DATA7 |

GPIO0_52 |

3.3V |

Video output data 7 |

VOUT0_DATA7 |

26 |

- |

GND |

- |

- |

Ground |

GND |

28 |

V21 |

VOUT0_DATA8 |

GPIO0_53 |

3.3V |

Video output data 8 |

VOUT0_DATA8 |

30 |

W21 |

VOUT0_DATA9 |

GPIO0_54 |

3.3V |

Video output data 9 |

VOUT0_DATA9 |

32 |

V20 |

VOUT0_DATA10 |

GPIO0_55 |

3.3V |

Video output data 10 |

VOUT0_DATA10 |

34 |

AA23 |

VOUT0_DATA11 |

GPIO0_56 |

3.3V |

Video output data 11 |

VOUT0_DATA11 |

36 |

AB25 |

VOUT0_DATA12 |

GPIO0_57 |

3.3V |

Video output data 12 |

VOUT0_DATA12 |

38 |

AA24 |

VOUT0_DATA13 |

GPIO0_58 |

3.3V |

Video output data 13 |

VOUT0_DATA13 |

40 |

Y22 |

VOUT0_DATA14 |

GPIO0_59 |

3.3V |

Video output data 14 |

VOUT0_DATA14 |

42 |

AA21 |

VOUT0_DATA15 |

GPIO0_60 |

3.3V |

Video output data 15 |

VOUT0_DATA15 |

44 |

- |

GND |

- |

- |

Ground |

GND |

46 |

U24 |

GPMC0_AD15 |

GPIO0_30 |

3.3V |

GPMC data 15/address 16 |

GPMC0_AD15 |

48 |

U25 |

GPMC0_AD14 |

GPIO0_29 |

3.3V |

GPMC data 14/address 15 |

GPMC0_AD14 |

50 |

T24 |

GPMC0_AD13 |

GPIO0_28 |

3.3V |

GPMC data 13/address 14 |

GPMC0_AD13 |

52 |

T22 |

GPMC0_AD12 |

GPIO0_27 |

3.3V |

GPMC data 12/address 13 |

GPMC0_AD12 |

54 |

R21 |

GPMC0_AD11 |

GPIO0_26 |

3.3V |

GPMC data 11/address 12 |

GPMC0_AD11 |

56 |

T25 |

GPMC0_AD10 |

GPIO0_25 |

3.3V |

GPMC data 10/address 11 |

GPMC0_AD10 |

58 |

R25 |

GPMC0_AD9 |

GPIO0_24 |

3.3V |

GPMC data 9/address 10 |

GPMC0_AD9 |

60 |

R24 |

GPMC0_AD8 |

GPIO0_23 |

3.3V |

GPMC data 8/address 9 |

GPMC0_AD8 |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

R23 |

GPMC0_AD7 |

GPIO0_22 |

3.3V |

GPMC data 7/address 8 |

GPMC0_AD7 |

66 |

P21 |

GPMC0_AD6 |

GPIO0_21 |

3.3V |

GPMC data 6/address 7 |

GPMC0_AD6 |

68 |

P22 |

GPMC0_AD5 |

GPIO0_20 |

3.3V |

GPMC data 5/address 6 |

GPMC0_AD5 |

70 |

P24 |

GPMC0_AD4 |

GPIO0_19 |

3.3V |

GPMC data 4/address 5 |

GPMC0_AD4 |

72 |

N25 |

GPMC0_AD3 |

GPIO0_18 |

3.3V |

GPMC data 3/address 4 |

GPMC0_AD3 |

74 |

N24 |

GPMC0_AD2 |

GPIO0_17 |

3.3V |

GPMC data 2/address 3 |

GPMC0_AD2 |

76 |

N23 |

GPMC0_AD1 |

GPIO0_16 |

3.3V |

GPMC data 1/address 2 |

GPMC0_AD1 |

78 |

M25 |

GPMC0_AD0 |

GPIO0_15 |

3.3V |

GPMC data 0/address 1 |

GPMC0_AD0 |

80 |

- |

GND |

- |

- |

Ground |

GND |

Table 7. RIGHT_ DOWN (P4) Connector Interface (Odd) Pin Definition

NUM |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

1 |

- |

GND |

- |

- |

Ground |

GND |

3 |

F23 |

OSPI0_CSN0 |

GPIO0_11 |

1.8V |

OSPI chip select 0 |

OSPI0_CSN0 |

5 |

G21 |

OSPI0_CSN1 |

GPIO0_12 |

1.8V |

OSPI chip select 1 |

GPIO0_12 |

7 |

H21 |

OSPI0_CSN2 |

GPIO0_13 |

1.8V |

OSPI chip select 2 |

OSPI0_CSN2 |

9 |

E24 |

OSPI0_CSN3 |

GPIO0_14 |

1.8V |

OSPI chip select 3 |

OSPI0_CSN3 |

11 |

- |

GND |

- |

- |

Ground |

GND |

13 |

E25 |

OSPI_DQ0 |

GPIO0_3 |

1.8V |

OSPI Data 0 |

OSPI_DQ0 |

15 |

G24 |

OSPI_DQ1 |

GPIO0_4 |

1.8V |

OSPI Data 1 |

OSPI_DQ1 |

17 |

F25 |

OSPI_DQ2 |

GPIO0_5 |

1.8V |

OSPI Data 2 |

OSPI_DQ2 |

19 |

F24 |

OSPI_DQ3 |

GPIO0_6 |

1.8V |

OSPI Data 3 |

OSPI_DQ3 |

21 |

- |

GND |

- |

- |

Ground |

GND |

23 |

J23 |

OSPI_DQ4 |

GPIO0_7 |

1.8V |

OSPI Data 4 |

GPIO0_7 |

25 |

J25 |

OSPI_DQ5 |

GPIO0_8 |

1.8V |

OSPI Data 5 |

GPIO0_8 |

27 |

H25 |

OSPI_DQ6 |

GPIO0_9 |

1.8V |

OSPI Data 6 |

GPIO0_9 |

29 |

J22 |

OSPI_DQ7 |

GPIO0_10 |

1.8V |

OSPI Data 7 |

GPIO0_10 |

31 |

- |

GND |

- |

- |

Ground |

GND |

33 |

G25 |

OSPI0_LBCLK |

GPIO0_1 |

1.8V |

OSPI loop clock input/output |

OSPI0_LBCLK |

35 |

- |

GND |

- |

- |

Ground |

GND |

37 |

J24 |

OSPI_DQS |

GPIO0_2 |

1.8V |

OSPI data strobe or loopback clock input |

OSPI_DQS |

39 |

- |

GND |

- |

- |

Ground |

GND |

41 |

H24 |

OSPI_CLK |

GPIO0_0 |

1.8V |

OSPI clock output- |

OSPI_CLK |

43 |

- |

GND |

- |

- |

Ground |

GND |

45 |

U23 |

GPMC0_WAIT0 |

GPIO0_37 |

3.3V |

GPMC external wait for indication input |

GPMC0_WAIT0 |

47 |

V25 |

GPIO0_38 |

GPIO0_38 |

3.3V |

Main domain GPIO0_38 |

GPIO0_38 |

49 |

- |

GND |

- |

- |

Ground |

GND |

51 |

M21 |

GPMC0_CSN0 |

GPIO0_41 |

3.3V |

GPMC chip select 0 |

GPMC0_CSN0 |

53 |

L21 |

GPIO0_42 |

GPIO0_42 |

3.3V |

Main domain GPIO0_42 |

GPIO0_42 |

55 |

K22 |

GPMC0_CSN2 |

GPIO0_43 |

3.3V |

GPMC chip select 2 |

GPMC0_CSN2 |

57 |

K24 |

GPMC0_CSN3 |

GPIO0_44 |

3.3V |

GPMC chip select 3 |

GPMC0_CSN3 |

59 |

- |

GND |

- |

- |

Ground |

GND |

61 |

K25 |

GPMC0_WPN |

GPIO0_39 |

3.3V |

GPMC Flash write protect |

GPIO0_39 |

63 |

L25 |

GPMC0_WEN |

GPIO0_34 |

3.3V |

GPMC write enable |

GPMC0_WEN |

65 |

L24 |

GPMC0_OEN_REN |

GPIO0_33 |

3.3V |

GPMC output enable or read enable |

GPMC0_OEN_REN |

67 |

L23 |

GPMC0_ADVN_ALE |

GPIO0_32 |

3.3V |

GPMC address active (active low) or address latch enable |

GPMC0_ADVN_ALE |

69 |

M24 |

GPMC0_BE0N_CLE |

GPIO0_35 |

3.3V |

GPMC low byte enable or command latch enable |

GPIO0_35 |

71 |

M22 |

GPMC0_DIR |

GPIO0_35 |

3.3V |

GPMC data bus signal direction control |

GPIO0_40 |

73 |

N20 |

GPMC0_BE1N |

GPIO0_36 |

3.3V |

GPMC high byte enable |

GPIO0_36 |

75 |

- |

GND |

- |

- |

Ground |

GND |

77 |

P25 |

GPMC0_CLK |

GPIO0_31 |

3.3V |

GPMC clock output- |

GPIO0_31 |

79 |

- |

GND |

- |

- |

Ground |

GND |

Table 8. RIGHT_ DOWN (P4) Connector Interface (Even) Pin Definition

NUM** |

BALL |

Signal Name |

GPIO |

VOL |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

2 |

- |

GND |

- |

- |

Ground |

GND |

4 |

C21 |

MMC1_DATA2 |

GPIO1_43 |

1.8V/3.3V |

MMC1 data bit 2- |

MMC1_DATA2 |

6 |

D22 |

MMC1_DATA3 |

GPIO1_42 |

1.8V/3.3V |

MMC1 data bit 3- |

MMC1_DATA3 |

8 |

A21 |

MMC1_CMD |

GPIO1_47 |

1.8V/3.3V |

MMC1 command |

MMC1_CMD |

10 |

D17 |

MMC1_SDCD |

GPIO1_48 |

3.3V |

MMC1 card detection |

MMC1_SDCD |

12 |

- |

GND |

- |

- |

Ground |

GND |

14 |

B22 |

MMC1_CLK |

GPIO1_46 |

1.8V/3.3V |

MMC1 clock |

MMC1_CLK |

16 |

A22 |

MMC1_DATA0 |

GPIO1_45 |

1.8V/3.3V |

MMC1 data bit 0- |

MMC1_DATA0 |

18 |

B21 |

MMC1_DATA1 |

GPIO1_44 |

1.8V/3.3V |

MMC1 data bit 1- |

MMC1_DATA1 |

20 |

C17 |

GPIO1_49 |

GPIO1_49 |

3.3V |

Main domain GPIO1_49 |

GPIO1_49 |

22 |

- |

GND |

- |

- |

Ground |

GND |

24 |

E23 |

MMC2_DATA2 |

GPIO0_66 |

1.8V |

MMC2 data bit 2- |

MMC2_DATA2 |

26 |

D24 |

MMC2_DATA3 |

GPIO0_65 |

1.8V |

MMC2 data bit 3- |

MMC2_DATA3 |

28 |

C24 |

MMC2_CMD |

GPIO0_70 |

1.8V |

MMC2 command |

MMC2_CMD |

30 |

D25 |

MMC2_CLK |

GPIO0_69 |

1.8V |

MMC2 clock |

MMC2_CLK |

32 |

- |

GND |

- |

- |

Ground |

GND |

34 |

B24 |

MMC2_DATA0 |

GPIO0_68 |

1.8V |

MMC2 data bit 0- |

MMC2_DATA0 |

36 |

C25 |

MMC2_DATA1 |

GPIO0_67 |

1.8V |

MMC2 data bit 1- |

MMC2_DATA1 |

38 |

A23 |

GPIO0_71 |

GPIO0_71 |

1.8V |

Main domain GPIO0_71 |

GPIO0_71 |

40 |

B23 |

GPIO0_72 |

GPIO0_72 |

1.8V |

Main domain GPIO0_72 |

GPIO0_72 |

42 |

- |

GND |

- |

- |

Ground |

GND |

44 |

- |

VPP_1V8_EN |

- |

3.3V |

SoM VPP_1V8 enable input |

VPP_1V8_EN |

46 |

- |

GND |

- |

- |

Ground |

GND |

48 |

- |

EXTINTN |

- |

3.3V |

External interrupt input |

EXTINTN |

50 |

- |

RESET_REQZ |

- |

3.3V |

Main domain external hot reset request input |

RESET_REQZ |

52 |

- |

PORZ_OUT |

- |

3.3V |

Main domain POR status output |

PORZ_OUT |

54 |

- |

RESETSTATZ |

- |

3.3V |

Main domain hot reset state output |

RESETSTATZ |

56 |

- |

GND |

- |

- |

Ground |

GND |

58 |

- |

PMIC_LPM_EN0 |

- |

3.3V |

Dual function PMIC control output, |

PMIC_LPM_EN0 |

60 |

- |

VCC_3V3_SYS_PG |

- |

3.3V |

SoM VCC3V3 Power Good output, |

VCC_3V3_SYS_PG |

62 |

- |

GND |

- |

- |

Ground |

GND |

64 |

- |

GND |

- |

- |

Ground |

GND |

66 |

- |

GND |

- |

- |

Ground |

GND |

68 |

- |

GND |

- |

- |

Ground |

GND |

70 |

- |

GND |

- |

- |

Ground |

GND |

72 |

- |

DCDC_5V |

- |

5V |

SoM 5V power input |

DCDC_5V |

74 |

- |

DCDC_5V |

- |

5V |

SoM 5V power input |

DCDC_5V |

76 |

- |

DCDC_5V |

- |

5V |

SoM 5V power input |

DCDC_5V |

78 |

- |

DCDC_5V |

- |

5V |

SoM 5V power input |

DCDC_5V |

80 |

- |

DCDC_5V |

- |

5V |

SoM 5V power input |

DCDC_5V |

2.7 FET62xx SoM Pin Description (Divided by Function)

Note:

All the pin functions of the SoM are specified according to the “Default Functions” in the following table, please do not modify them, otherwise, they may conflict with the factory driver. Please contact us with any questions in time;

When you have requirements for multiple function expansions, please refer to the “FET62xx-C Pin Multiplexing Comparison Table” in the reference materials. However, if you need more detailed information, please consult relevant documentation, the chip data sheet, and the reference manual;

The pins marked as “Do not use on carrier board” in the “Default Function” column are those already utilized by the SoM and should not be used in the design of the carrier board;

“Signal Name” column defaults to SoM pin name, and the red mark is carrier board pin definition name.

2.7.1 Power Pin

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

Power |

DCDC_5V |

Power Input |

External power supply pin, 5V |

P4_72 |

DCDC_5V |

Power Input |

External power supply pin, 5V |

||

DCDC_5V |

Power Input |

External power supply pin, 5V |

||

DCDC_5V |

Power Input |

External power supply pin, 5V |

||

DCDC_5V |

Power Input |

External power supply pin, 5V |

||

GND |

— |

Power ground |

P1_1 |

|

GND |

— |

Power ground |

P1_2 |

|

GND |

— |

Power ground |

P1_7 |

|

GND |

— |

Power ground |

P1_8 |

|

GND |

— |

Power ground |

P1_13 |

|

GND |

— |

Power ground |

P1_14 |

|

GND |

— |

Power ground |

P1_19 |

|

GND |

— |

Power ground |

P1_20 |

|

GND |

— |

Power ground |

P1_25 |

|

GND |

— |

Power ground |

P1_26 |

|

GND |

— |

Power ground |

P1_31 |

|

GND |

— |

Power ground |

P1_32 |

|

GND |

— |

Power ground |

P1_34 |

|

GND |

— |

Power ground |

P1_36 |

|

GND |

— |

Power ground |

P1_37 |

|

GND |

— |

Power ground |

P1_38 |

|

GND |

— |

Power ground |

P1_40 |

|

GND |

— |

Power ground |

P1_42 |

|

GND |

— |

Power ground |

P1_43 |

|

GND |

— |

Power ground |

P1_44 |

|

GND |

— |

Power ground |

P1_46 |

|

GND |

— |

Power ground |

P1_48 |

|

GND |

— |

Power ground |

P1_49 |

|

GND |

— |

Power ground |

P1_50 |

|

GND |

— |

Power ground |

P1_52 |

|

GND |

— |

Power ground |

P1_54 |

|

GND |

— |

Power ground |

P1_55 |

|

GND |

— |

Power ground |

P1_56 |

|

GND |

— |

Power ground |

P1_58 |

|

GND |

— |

Power ground |

P1_60 |

|

GND |

— |

Power ground |

P1_61 |

|

GND |

— |

Power ground |

P1_62 |

|

GND |

— |

Power ground |

P1_63 |

|

GND |

— |

Power ground |

P1_64 |

|

GND |

— |

Power ground |

P1_66 |

|

GND |

— |

Power ground |

P1_68 |

|

GND |

— |

Power ground |

P1_69 |

|

GND |

— |

Power ground |

P1_71 |

|

GND |

— |

Power ground |

P1_72 |

|

GND |

— |

Power ground |

P1_74 |

|

GND |

— |

Power ground |

P1_77 |

|

GND |

— |

Power ground |

P1_78 |

|

GND |

— |

Power ground |

P1_79 |

|

GND |

— |

Power ground |

P1_80 |

|

GND |

— |

Power ground |

P2_1 |

|

GND |

— |

Power ground |

P2_2 |

|

GND |

— |

Power ground |

P2_7 |

|

GND |

— |

Power ground |

P2_8 |

|

GND |

— |

Power ground |

P2_17 |

|

GND |

— |

Power ground |

P2_18 |

|

GND |

— |

Power ground |

P2_27 |

|

GND |

— |

Power ground |

P2_30 |

|

GND |

— |

Power ground |

P2_31 |

|

GND |

— |

Power ground |

P2_41 |

|

GND |

— |

Power ground |

P2_42 |

|

GND |

— |

Power ground |

P2_47 |

|

GND |

— |

Power ground |

P2_48 |

|

GND |

— |

Power ground |

P2_61 |

|

GND |

— |

Power ground |

P2_62 |

|

GND |

— |

Power ground |

P2_71 |

|

GND |

— |

Power ground |

P2_75 |

|

GND |

— |

Power ground |

P2_80 |

|

GND |

— |

Power ground |

P2_79 |

|

GND |

— |

Power ground |

P2_80 |

|

GND |

— |

Power ground |

P3_1 |

|

GND |

— |

Power ground |

P3_2 |

|

GND |

— |

Power ground |

P3_6 |

|

GND |

— |

Power ground |

P3_8 |

|

GND |

— |

Power ground |

P3_9 |

|

GND |

— |

Power ground |

P3_15 |

|

GND |

— |

Power ground |

P3_21 |

|

GND |

— |

Power ground |

P3_26 |

|

GND |

— |

Power ground |

P3_31 |

|

GND |

— |

Power ground |

P3_37 |

|

GND |

— |

Power ground |

P3_44 |

|

GND |

— |

Power ground |

P3_47 |

|

GND |

— |

Power ground |

P3_53 |

|

GND |

— |

Power ground |

P3_62 |

|

GND |

— |

Power ground |

P3_63 |

|

GND |

— |

Power ground |

P3_69 |

|

GND |

— |

Power ground |

P3_79 |

|

GND |

— |

Power ground |

P3_80 |

|

GND |

— |

Power ground |

P4_1 |

|

GND |

— |

Power ground |

P4_2 |

|

GND |

— |

Power ground |

P4_11 |

|

GND |

— |

Power ground |

P4_12 |

|

GND |

— |

Power ground |

P4_21 |

|

GND |

— |

Power ground |

P4_22 |

|

GND |

— |

Power ground |

P4_31 |

|

GND |

— |

Power ground |

P4_32 |

|

GND |

— |

Power ground |

P4_35 |

|

GND |

— |

Power ground |

P4_39 |

|

GND |

— |

Power ground |

P4_42 |

|

GND |

— |

Power ground |

P4_43 |

|

GND |

— |

Power ground |

P4_46 |

|

GND |

— |

Power ground |

P4_49 |

|

GND |

— |

Power ground |

P4_56 |

|

GND |

— |

Power ground |

P4_59 |

|

GND |

— |

Power ground |

P4_62 |

|

GND |

— |

Power ground |

P4_64 |

|

GND |

— |

Power ground |

P4_66 |

|

GND |

— |

Power ground |

P4_68 |

|

GND |

— |

Power ground |

P4_70 |

|

GND |

— |

Power ground |

P4_75 |

|

GND |

— |

Power ground |

P4_79 |

2.7.2 Boot Control Pin

Note: Refer to “3.5.4 Boot Configuration” for boot startup configuration pin.

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

BOOTMODE |

BOOTMODE00 |

I |

BOOT Mode Configuration 0 |

P3_78 |

BOOTMODE01 |

I |

BOOT Mode Configuration 1 |

P3_76 |

|

BOOTMODE02 |

I |

BOOT Mode Configuration 2 |

P3_74 |

|

BOOTMODE03 |

I |

BOOT Mode Configuration 3 |

P3_72 |

|

BOOTMODE04 |

I |

BOOT Mode Configuration 4 |

P3_70 |

|

BOOTMODE05 |

I |

BOOT Mode Configuration 5 |

P3_68 |

|

BOOTMODE06 |

I |

BOOT Mode Configuration 6 |

P3_66 |

|

BOOTMODE07 |

I |

BOOT Mode Configuration 7 |

P3_64 |

|

BOOTMODE08 |

I |

BOOT Mode Configuration 8 |

P3_60 |

|

BOOTMODE09 |

I |

BOOT Mode Configuration 9 |

P3_58 |

|

BOOTMODE10 |

I |

BOOT Mode Configuration 10 |

P3_56 |

|

BOOTMODE11 |

I |

BOOT Mode Configuration 11 |

P3_54 |

|

BOOTMODE12 |

I |

BOOT Mode Configuration 12 |

P3_52 |

|

BOOTMODE13 |

I |

BOOT Mode Configuration 13 |

P3_50 |

|

BOOTMODE14 |

I |

BOOT Mode Configuration 14 |

P3_48 |

|

BOOTMODE15 |

I |

BOOT Mode Configuration 15 |

P3_46 |

2.7.3 LVDS Output Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

LVDS |

CH1_LVDS_A0P |

O |

CH1_LVDS data 0+ |

P1_3 |

CH1_LVDS_A0N |

O |

CH1_LVDS data bit 0- |

P1_5 |

|

CH1_LVDS_A1P |

O |

CH1_LVDS data 1+ |

P1_9 |

|

CH1_LVDS_A1N |

O |

CH1_LVDS data bit 1- |

P1_11 |

|

CH1_LVDS_A2P |

O |

CH1_LVDS data 2+ |

P1_15 |

|

CH1_LVDS_A2N |

O |

CH1_LVDS data bit 2- |

P1_17 |

|

CH1_LVDS_CLKP |

O |

CH1_LVDS clock+ |

P1_21 |

|

CH1_LVDS_CLKN |

O |

CH1_LVDS clock- |

P1_23 |

|

CH1_LVDS_A3P |

O |

CH1_LVDS data 3+ |

P1_27 |

|

CH1_LVDS_A3N |

O |

CH1_LVDS data bit 3- |

P1_29 |

|

CH2_LVDS_CLKN |

O |

CH2_LVDS clock- |

P1_33 |

|

CH2_LVDS_CLKP |

O |

CH2_LVDS clock+ |

P1_35 |

|

CH2_LVDS_A1N |

O |

CH2_LVDS data bit 1- |

P1_39 |

|

CH2_LVDS_A1P |

O |

CH2_LVDS data 1+ |

P1_41 |

|

CH2_LVDS_A2N |

O |

CH2_LVDS data bit 2- |

P1_45 |

|

CH2_LVDS_A2P |

O |

CH2_LVDS data 2+ |

P1_47 |

|

CH2_LVDS_A0P |

O |

CH2_LVDS data 0+ |

P1_51 |

|

CH2_LVDS_A0N |

O |

CH2_LVDS data bit 0- |

P1_53 |

|

CH2_LVDS_A3P |

O |

CH2_LVDS data 3+ |

P1_57 |

|

CH2_LVDS_A3N |

O |

CH2_LVDS data bit 3- |

P1_59 |

|

Backlight Adjustment |

EHRPWM1_A |

O |

EHRPWM1_A function |

P2_66 |

2.7.4 MIPI CSI Input Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

MIPI CSI |

CSI0_RXCLKP |

I |

CSI0 clock+ |

P1_4 |

CSI0_RXCLKN |

I |

CSI0 clock- |

P1_6 |

|

CSI0_RXP3 |

I |

CSI0 data receiving 3+ |

P1_10 |

|

CSI0_RXN3 |

I |

CSI0 data receiving 3- |

P1_12 |

|

CSI0_RXP1 |

I |

CSI0 data receiving 1+ |

P1_16 |

|

CSI0_RXN1 |

I |

CSI0 data receiving 1- |

P1_18 |

|

CSI0_RXP2 |

I |

CSI0 data receiving 2+ |

P1_22 |

|

CSI0_RXN2 |

I |

CSI0 data receiving 2- |

P1_24 |

|

CSI0_RXP0 |

I |

CSI0 data receiving 0+ |

P1_28 |

|

CSI0_RXN0 |

I |

CSI0 data receiving 0- |

P1_30 |

2.7.5 USB Function Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

USB0 |

USB0_DP |

I/O |

USB0 data+ |

P1_73 |

USB0_DM |

I/O |

USB0 data- |

P1_75 |

|

USB0_VBUS |

I |

USB0 VBUS detection |

P1_70 |

|

USB0_DRVBUS |

O |

USB0 VBUS enable |

P2_77 |

|

USB1 |

USB1_DP |

I/O |

USB1 data+ |

P1_65 |

USB1_DM |

I/O |

USB1 data- |

P1_67 |

|

USB1_VBUS |

I |

USB1 VBUS detection |

P1_76 |

|

USB1_DRVVBUS |

O |

USB1 VBUS enable |

P2_79 |

2.7.6 Ethernet Interface Control Pin

MAIN Domain: RGMII Signal Description

Default Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

RGMII1 |

CPSW_RGMII1_RXC |

I |

RGMII receive clock |

P3_17 |

CPSW_RGMII1_RX_CTL |

I |

RGMII receives control |

P3_19 |

|

CPSW_RGMII1_RD0 |

I |

RGMII receive data 0 |

P3_23 |

|

CPSW_RGMII1_RD1 |

I |

RGMII receive data 1 |

P3_25 |

|

CPSW_RGMII1_RD2 |

I |

RGMII receive data 2 |

P3_27 |

|

CPSW_RGMII1_RD3 |

I |

RGMII receive data 3 |

P3_29 |

|

CPSW_RGMII1_TXC |

O |

RGMII send clock |

P3_33 |

|

CPSW_RGMII1_TX_CTL |

O |

RGMII send control |

P3_35 |

|

CPSW_RGMII1_TD0 |

O |

RGMII send data 0 |

P3_39 |

|

CPSW_RGMII1_TD1 |

O |

RGMII send data 1 |

P3_41 |

|

CPSW_RGMII1_TD2 |

O |

RGMII send data 2 |

P3_43 |

|

CPSW_RGMII1_TD3 |

O |

RGMII send data 3 |

P3_45 |

|

RGMII2 |

CPSW_RGMII1_RXC |

I |

RGMII receive clock |

P3_49 |

CPSW_RGMII1_RX_CTL |

I |

RGMII receives control |

P3_51 |

|

CPSW_RGMII1_RD0 |

I |

RGMII receive data 0 |

P3_55 |

|

CPSW_RGMII1_RD1 |

I |

RGMII receive data 1 |

P3_57 |

|

CPSW_RGMII1_RD2 |

I |

RGMII receive data 2 |

P3_59 |

|

CPSW_RGMII1_RD3 |

I |

RGMII receive data 3 |

P3_61 |

|

CPSW_RGMII1_TXC |

O |

RGMII send clock |

P3_65 |

|

CPSW_RGMII1_TX_CTL |

O |

RGMII send control |

P3_67 |

|

CPSW_RGMII1_TD0 |

O |

RGMII send data 0 |

P3_71 |

|

CPSW_RGMII1_TD1 |

O |

RGMII send data 1 |

P3_73 |

|

CPSW_RGMII1_TD2 |

O |

RGMII send data 2 |

P3_75 |

|

CPSW_RGMII1_TD3 |

O |

RGMII send data 3 |

P3_77 |

MAIN Domain: RMII Signal Description

Default Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

RMII1 |

RMII1_CRS_DV |

I |

RMII Carrier Sense/Data Valid |

P3_33 |

RMII1_REF_CLK |

I |

RMII reference clock |

P3_17 |

|

RMII1_RX_ER |

I |

RMII receive data error |

P3_19 |

|

RMII1_TX_EN |

O |

RMII send enable |

P3_35 |

|

RMII1_RXD0 |

I |

RMII receive data 0 |

P3_23 |

|

RMII1_RXD1 |

I |

RMII receive data 1 |

P3_25 |

|

RMII1_TXD0 |

O |

RMII send data 0 |

P3_39 |

|

MII1_TXD1 |

O |

RMII send data 1 |

P3_41 |

|

RMII2 |

RMII2_CRS_DV |

I |

RMII Carrier Sense/Data Valid |

P3_65 |

RMII2_REF_CLK |

I |

RMII reference clock |

P3_49 |

|

RMII2_RX_ER |

I |

RMII receive data error |

P3_51 |

|

RMII2_TX_EN |

O |

RMII send enable |

P3_67 |

|

RMII2_RXD0 |

I |

RMII receive data 0 |

P3_55 |

|

RMII2_RXD1 |

I |

RMII receive data 1 |

P3_57 |

|

RMII2_TXD0 |

O |

RMII send data 0 |

P3_71 |

|

RMII2_TXD1 |

O |

RMII send data 1 |

P3_73 |

2.7.7 CPTS Interface Control Pin

MAIN Domain:

Default Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

CPTS |

CP_GEMAC_CPTS0_RFT_CLK |

I |

CPTS reference clock input |

P2_60 |

CP_GEMAC_CPTS0_TS_COMP |

O |

CPTS timestamp counter comparison output from CPSW3G0 CPTS |

P2_32, P4_6 |

|

CP_GEMAC_CPTS0_TS_SYNC |

O |

CPTS timestamp counter bits output from CPSW3G0 CPTS |

P2_38, P4_4 |

|

CP_GEMAC_CPTS0_HW1TSPUSH |

I |

CPTS hardware timestamp push input to time synchronization router |

P2_36, P4_18 |

|

CP_GEMAC_CPTS0_HW2TSPUSH |

I |

CPTS hardware timestamp push input to time synchronization router |

P4_16, P2_40 |

|

SYNC0_OUT |

O |

CPTS timestamp generator bit 0 output of time synchronization router |

P2_50 |

|

SYNC2_OUT |

O |

CPTS timestamp generator bit 2 output of time synchronization router |

P2_44 |

|

SYNC3_OUT |

O |

CPTS timestamp generator bit 3 output of time synchronization router |

P2_46 |

2.7.8 DSS(Display Subsystem)Signal Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

VOUT |

VOUT0_DE |

O |

Enable video output data |

P3_7 |

VOUT0_EXTPCLKIN |

I |

Video output external pixel clock input |

P4_47 |

|

VOUT0_HSYNC |

O |

Horizontal synchronization of video output |

P3_5 |

|

VOUT0_PCLK |

O |

Video output pixel clock Output |

P3_4 |

|

VOUT0_VSYNC |

O |

Vertical synchronization of video output |

P3_3 |

|

VOUT0_DATA0 |

O |

Video output data 0 |

P3_10 |

|

VOUT0_DATA1 |

O |

Video output data 1 |

P3_12 |

|

VOUT0_DATA2 |

O |

Video output data 2 |

P3_14 |

|

VOUT0_DATA3 |

O |

Video output data 3 |

P3_16 |

|

VOUT0_DATA4 |

O |

Video output data 4 |

P3_18 |

|

VOUT0_DATA5 |

O |

Video output data 5 |

P3_20 |

|

VOUT0_DATA6 |

O |

Video output data 6 |

P3_22 |

|

VOUT0_DATA7 |

O |

Video output data 7 |

P3_24 |

|

VOUT0_DATA8 |

O |

Video output data 8 |

P3_28 |

|

VOUT0_DATA9 |

O |

Video output data 9 |

P3_30 |

|

VOUT0_DATA10 |

O |

Video output data 10 |

P3_32 |

|

VOUT0_DATA11 |

O |

Video output data 11 |

P3_34 |

|

VOUT0_DATA12 |

O |

Video output data 12 |

P3_36 |

|

VOUT0_DATA13 |

O |

Video output data 13 |

P3_38 |

|

VOUT0_DATA14 |

O |

Video output data 14 |

P3_40 |

|

VOUT0_DATA15 |

O |

Video output data 15 |

P3_42 |

|

VOUT0_DATA16 |

O |

Video output data 16 |

P3_60 |

|

VOUT0_DATA17 |

O |

Video output data 17 |

P3_58 |

|

VOUT0_DATA18 |

O |

Video output data 18 |

P3_56 |

|

VOUT0_DATA19 |

O |

Video output data 19 |

P3_54 |

|

VOUT0_DATA20 |

O |

Video output data 20 |

P3_52 |

|

VOUT0_DATA21 |

O |

Video output data 21 |

P3_50 |

|

VOUT0_DATA22 |

O |

Video output data 22 |

P3_48 |

|

VOUT0_DATA23 |

O |

Video output data 23 |

P3_466 |

2.7.9 ECAP Control Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

ECAP0 |

ECAP0_IN_APWM_OUT |

IO |

Enhanced capture (ECAP) input or auxiliary PWM (PWM) output |

P2_32 |

ECAP1 |

ECAP1_IN_APWM_OUT |

IO |

Enhanced capture (ECAP) input or auxiliary PWM (PWM) output |

P2_50, P2_66, P2_70, |

ECAP2 |

ECAP2_IN_APWM_OUT |

IO |

Enhanced capture (ECAP) input or auxiliary PWM (PWM) output |

P2_52, P2_68, P4_16, |

2.7.10 Emulation and Debug Interface Control Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

Trace Signal |

TRC_CLK |

O |

Trace Clock |

P3_78 |

TRC_CTL |

O |

Trace Control |

P3_76 |

|

TRC_DATA0 |

O |

Trace data 0 |

P3_74 |

|

TRC_DATA1 |

O |

Trace data 1 |

P3_72 |

|

TRC_DATA2 |

O |

Trace data 2 |

P3_70 |

|

TRC_DATA3 |

O |

Trace data 3 |

P3_68 |

|

TRC_DATA4 |

O |

Trace data 4 |

P3_66 |

|

TRC_DATA5 |

O |

Trace data 5 |

P3_64 |

|

TRC_DATA6 |

O |

Trace data 6 |

P4_77 |

|

TRC_DATA7 |

O |

Trace data 7 |

P4_67 |

|

TRC_DATA8 |

O |

Trace data 8 |

P4_65 |

|

TRC_DATA9 |

O |

Trace data 9 |

P4_63 |

|

TRC_DATA10 |

O |

Trace data 10 |

P4_69 |

|

TRC_DATA11 |

O |

Trace data 11 |

P4_73 |

|

TRC_DATA12 |

O |

Trace data 12 |

P4_45 |

|

TRC_DATA13 |

O |

Trace data 13 |

P4_61 |

|

TRC_DATA14 |

O |

Trace data 14 |

P4_71 |

|

TRC_DATA15 |

O |

Trace data 15 |

P4_51 |

|

TRC_DATA16 |

O |

Trace data 16 |

P4_53 |

|

TRC_DATA17 |

O |

Trace data 17 |

P4_55 |

|

TRC_DATA18 |

O |

Trace data 18 |

P4_57 |

|

TRC_DATA19 |

O |

Trace data 19 |

P3_46 |

|

TRC_DATA20 |

O |

Trace data 20 |

P3_48 |

|

TRC_DATA21 |

O |

Trace data 21 |

P3_50 |

|

TRC_DATA22 |

O |

Trace data 22 |

P3_52 |

|

TRC_DATA23 |

O |

Trace data 23 |

P3_54 |

MCU Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

JTAG |

EMU0 |

IO |

Simulation control 0 |

P2_43 |

EMU1 |

IO |

Simulation control 1 |

P2_45 |

|

TCK |

I |

JTAG test clock input |

P2_53 |

|

TDI |

I |

JTAG test data input |

P2_57 |

|

TDO |

OZ |

JTAG test data output |

P2_59 |

|

TMS |

I |

JTAG test mode selection input |

P2_55 |

|

TRSTn |

I |

JTAG reset |

P2_51 |

2.7.11 EPWM Interface Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

EPWM |

EHRPWM_SOCA |

O |

EHRPWM starts converting A |

P2_50 |

EHRPWM_SOCB |

O |

EHRPWM starts converting B |

P2_52 |

|

EHRPWM_TZn_IN0 |

I |

EHRPWM trigger zone input 0 (active low) |

P2_40 |

|

EHRPWM_TZn_IN3 |

I |

EHRPWM trigger zone input 3 (active low) |

P2_44 |

|

EHRPWM_TZn_IN4 |

I |

EHRPWM trigger zone input 4 (active low) |

P2_46 |

|

EHRPWM_TZn_IN5 |

I |

EHRPWM trigger zone input 5 (active low) |

P2_32 |

|

EPWM0 |

EHRPWM0_A |

IO |

EHRPWM output A |

P2_34, |

EHRPWM0_B |

IO |

EHRPWM output B |

P2_72, P2_32, |

|

EHRPWM0_SYNCI |

I |

Synchronized input to the EHRPWM module from external pins |

P2_54 |

|

EHRPWM0_SYNCO |

O |

Synchronized input to the EHRPWM module from external pins |

P2_56, |

|

EPWM1 |

EHRPWM1_A |

IO |

EHRPWM output A |

P2_38, |

EHRPWM1_B |

IO |

EHRPWM output B |

P2_36, P2_64 |

|

EPWM2 |

EHRPWM2_A |

IO |

EHRPWM output A |

P2_54, P2_63 |

EHRPWM2_B |

IO |

EHRPWM output B |

P2_56, P2_65, |

2.7.12 EQEP Interface Pin

MAIN Domain:

Function |

Signal Name |

I/O |

Default Function |

Pin Number |

|---|---|---|---|---|

EQEP0 |

EQEP0_A |

I |

EQEP quadrature input A |

P2_70 |

EQEP0_B |

I |

EQEP quadrature input B |

P2_68 |

|

EQEP0_I |