User’s Hardware Manual_V3.3

Document classification: □ Top secret □ Secret □ Internal information ■ Open

Copyright

The copyright of this manual belongs to Baoding Folinx Embedded Technology Co., Ltd. Without the written permission of our company, no organizations or individuals have the right to copy, distribute, or reproduce any part of this manual in any form, and violators will be held legally responsible.

Forlinx adheres to copyrights of all graphics and texts used in all publications in original or license-free forms.

The drivers and utilities used for the components are subject to the copyrights of the respective manufacturers. The license conditions of the respective manufacturer are to be adhered to. Related license expenses for the operating system and applications should be calculated/declared separately by the related party or its representatives.

Application Scope

This manual is mainly applicable to the Forlinx OK3568-C platform. Other platforms can also refer to it, but there will be differences between different platforms. Please make modifications according to the actual conditions.

Revision History

Date |

Manual Version |

Revision History |

|---|---|---|

15/03/2022 |

V1.0 |

OK3568-C_User’s Hardware Manual Initial Version |

30/05/2022 |

V1.1 |

Adding the description of the industrial-grade parameters of FET3568J - C to the naming rules; 2. Adding the content about FET3568J - C to the ordering information; 3. Adding the description of the operating temperature to the working environment. |

03/09/2022 |

V1.2 |

Adding industrial 4G + 32G configuration information in the order information. |

07/04/2023 |

V1.3 |

Adding commercial 4G + 32G configuration information in the order information. |

13/04/2023 |

V1.4 |

1. Separating the description of USB2.0 and USB 3.0 interface resources in the “2.5 Core Board Interface Resources” section; |

19/04/2025 |

V1.5 |

Adding 2.4.5 “ESD Characteristics” in Chapter 2 “Introduction to FET3568 - C SoM”, supplementing a detailed description of the ESD characteristics of the SoM’s pins. |

01/06/2023 |

V1.6 |

1. Adding the configuration information of the industrial - grade 1GB + 8GB to the ordering information; |

07/06/2023 |

V1.7 |

Modifying the description of the supported CAN. |

01/12/2023 |

V1.8 |

1. Adding the design requirements for the peripheral circuit when employing the RTL8211FSI - CG chip into the Ethernet interface description on the carrier board; |

28/12/2023 |

V1.9 |

1. Improving the board design considerations in the audio section and FSPI section of the instructions for the OK3568 - C carrier board; |

19/03/2024 |

V2.0 |

1. Adding the image of the FET3568-C2 SoM; |

10/05/2024 |

V3.0 |

Adding FET3568-C2, OK3568-C2C configuration. |

22/09/2025 |

V3.1 |

Adding precautions for using the WIFI function (It is necessary to install an antenna before using the WIFI function). |

22/09/2025 |

V3.1 |

Adding precautions for using the WIFI function (It is necessary to install an antenna before using the WIFI function). |

21/11/2025 |

V3.2 |

Adding Section 2.6.2 SoM Vibration-Resistant Design Guidelines |

19/03/2026 |

V3.3 |

Updating Section 3.5.1 Carrier Board Power: Optimize the timing to ensure stable operation of relay control. |

Overview

This manual is designed to help you quickly familiarize yourselves with the product, understand interface functions and configuration, and primarily discusses the interface functions of the development board, interface introductions, product power consumption, and troubleshooting issues that may arise during use. Some commands were commented to make it easier for you to understand (adequate and practical for the purpose). For information on pin function multiplexing, hardware troubleshooting methods, etc., please refer to Forlinx’s “OK3568-C Pin Multiplexing Comparison Table” and “OK3568-C Design Guide.”

There are total four chapters:

Chapter 1. is CPU overview, briefly introducing its performance and applications;

Chapter 2. is comprehensive introduction to the SoM, including connector pins explanations and function introductions;

Chapter 3. is comprehensive introduction to the development board, divided into multiple chapters, including both hardware principles and simple design ideas;

Chapter 4. mainly describes the board’s power consumption performance and other considerations.

A description of some of the symbols and formats associated with this manual:

Format |

Meaning |

|---|---|

Note |

Note or information that requires special attention, be sure to read carefully. |

📚 |

Relevant notes on the test chapters. |

🛤️ ️️ |

Indicates the related path. |

Blue font on gray background |

Refers to commands entered at the command line (Manual input required). |

Black font |

Serial port output message after entering a command |

Bold black |

Key information in the serial port output message |

// |

Interpretation of input instructions or output information |

1. RK3568 Description

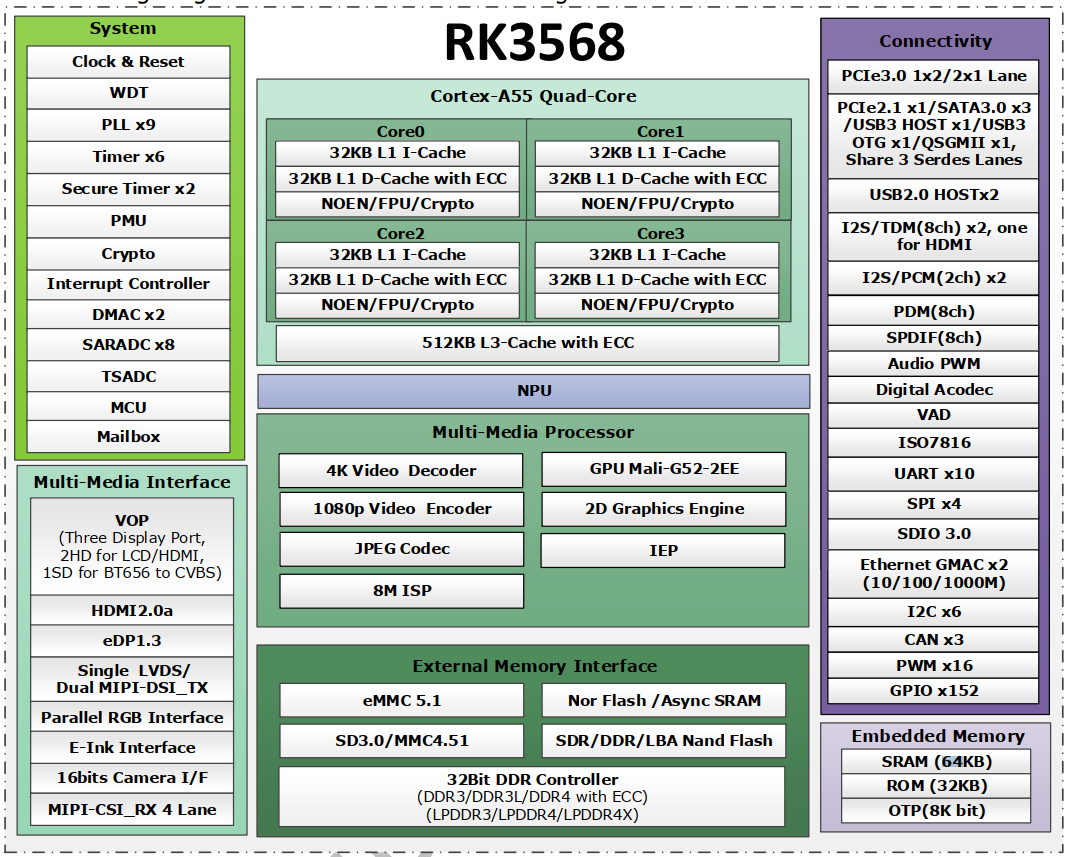

RK3568 is a high - performance, low - power, feature - rich application processor developed by Rockchip for the AIoT and industrial markets. It features a quad-core 64-bit Cortex-A55 architecture with a main frequency of up to 2.0 GHz, integrating Rockchip’s self-developed NPU and 1 TOPS computing power to support lightweight AI computing. It also provides an easy - to - use model conversion tool, RKNN - Toolkit, which supports one - click conversion of mainstream architecture models such as Caffe, TensorFlow, TF - Lite, ONNX, PyTorch, Keras, and Darknet.

The RK3568 supports five types of display interfaces, namely HDMI2.0, eDP, LVDS, RGB Parallel, and MIPI-DSI. It can simultaneously output three channels of display signals and offers high-definition hardware decoding for multiple formats such as 4K resolution H.264/H.265/VP9. Moreover, it is capable of decoding multiple video sources simultaneously and supports HDR10, delivering excellent performance in terms of color and dynamic range. It supports a variety of high - speed bus interfaces, such as PCIE 3.0, USB 3.0, RGMII/SGMII/QSGMII (2 MAC), and CAN.

Target Applications:

·Smart Healthcare

·Intelligent Transportation

·Security & Surveillance

·Power Industry

·Energy & Chemical Industry

·Smart City

……

RK3568 Series Block Diagram

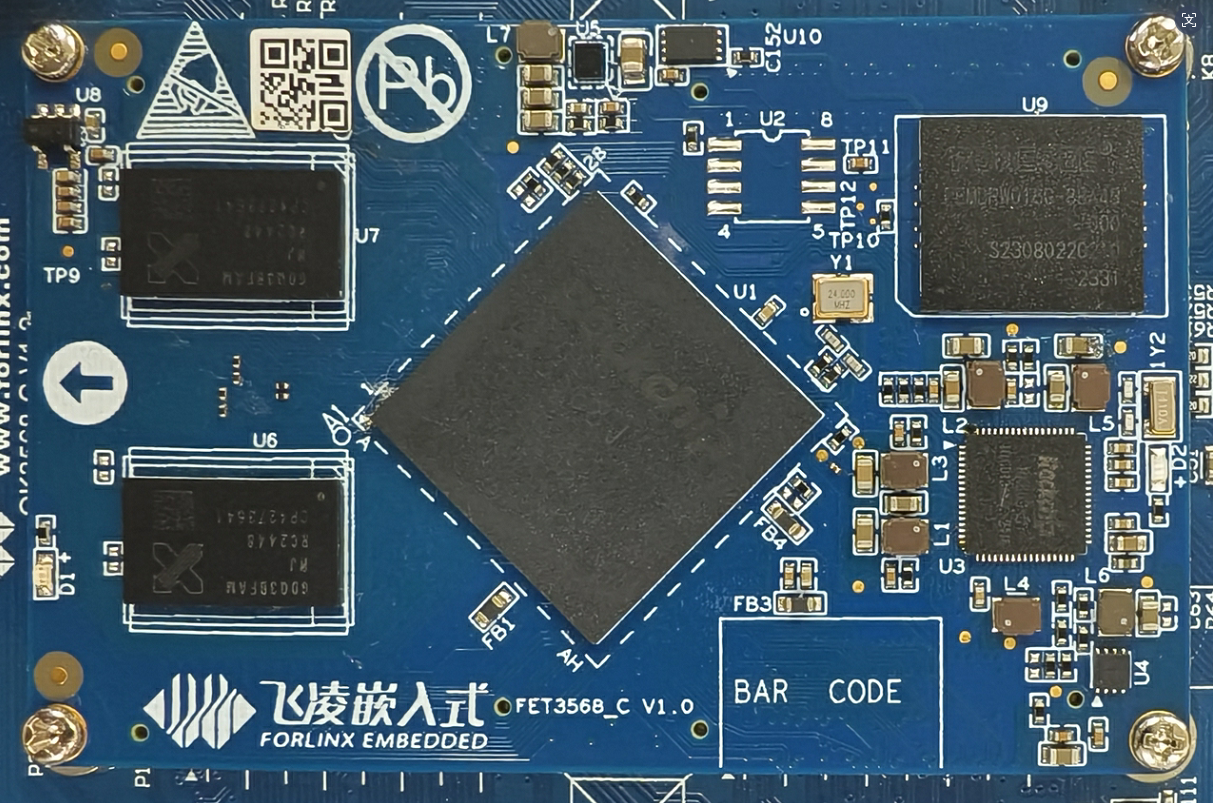

2. FET3568-C&C2 SoM Description

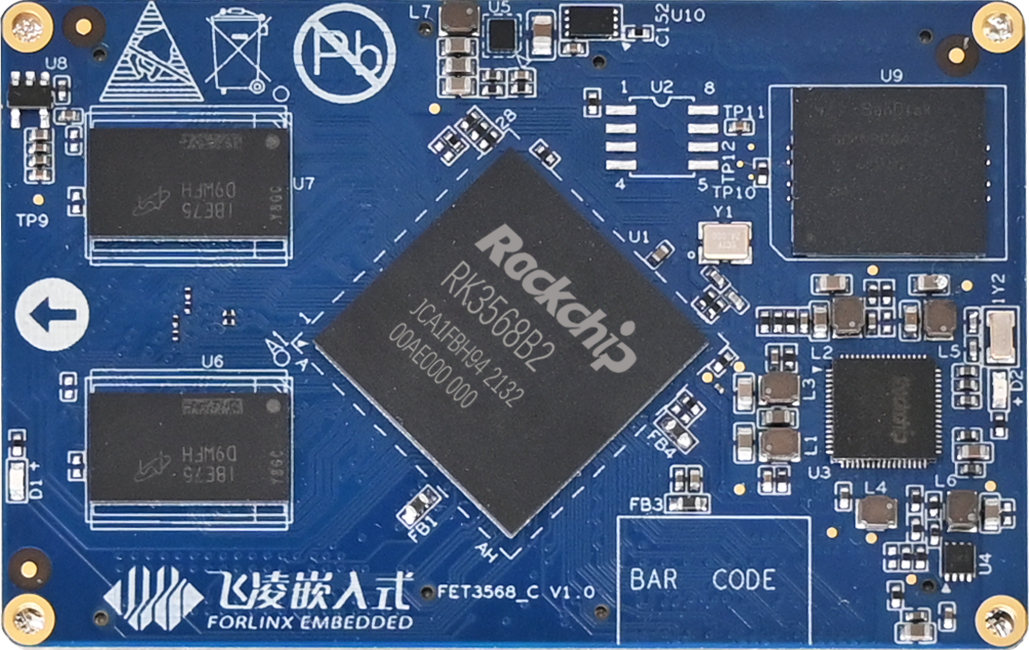

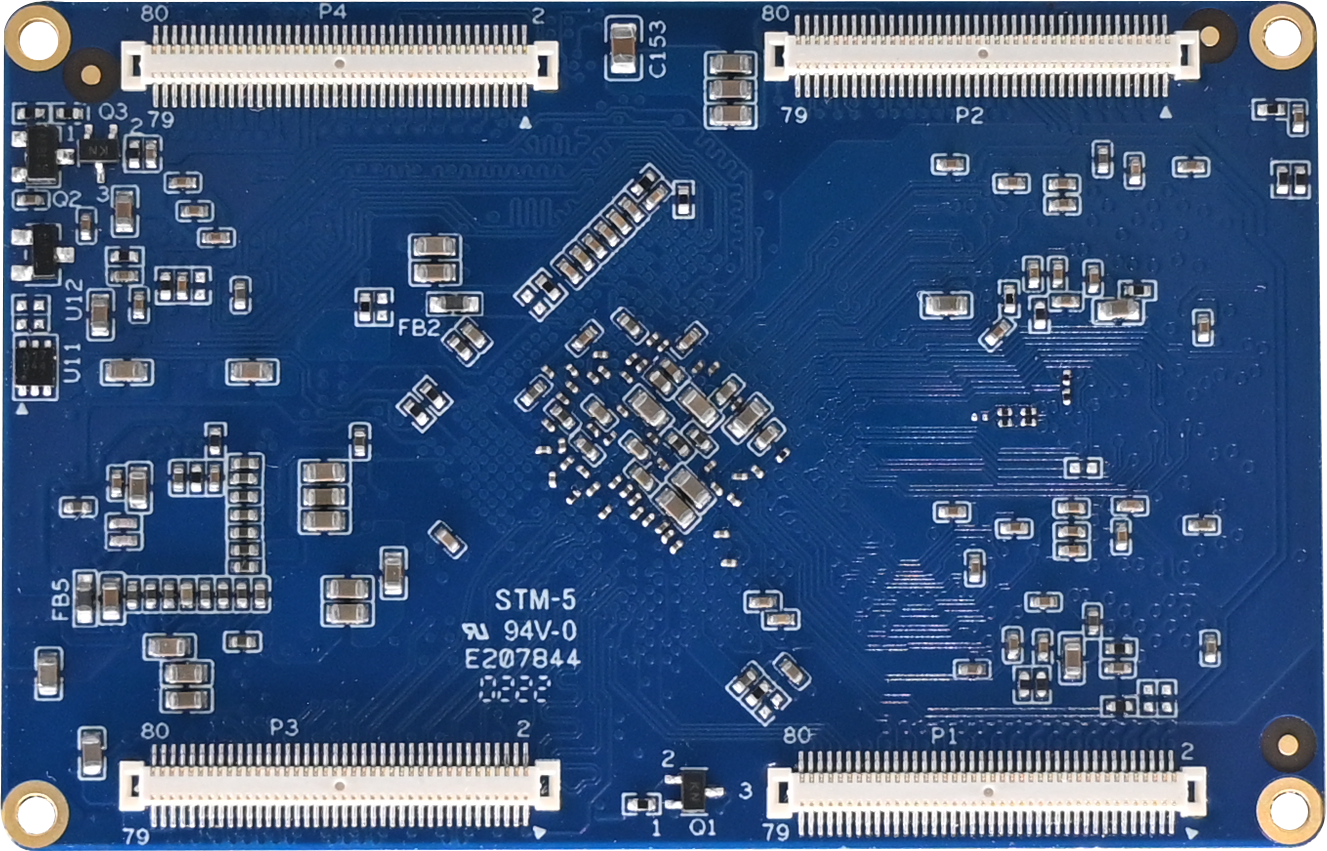

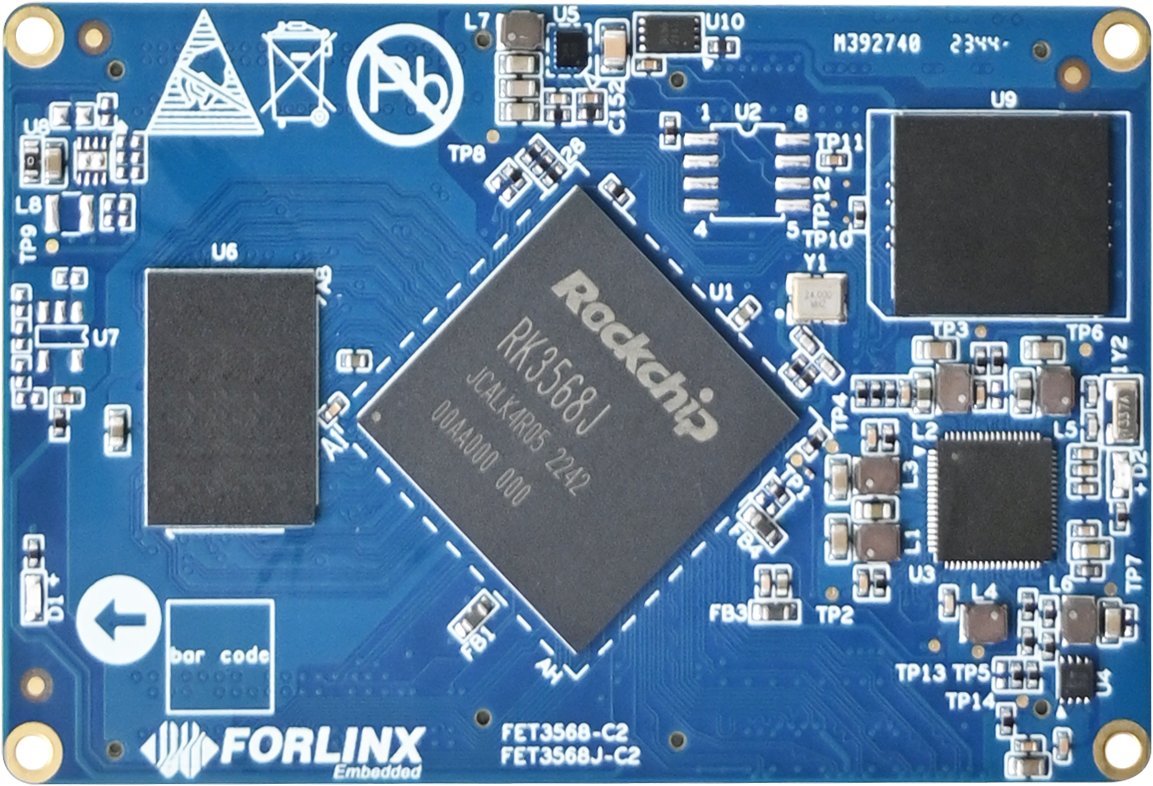

The pin definitions of the connectors for the FET3568-C/FET3568J-C and FET3568-C2/FET3568J-C2 SoMs are completely identical. The difference between them lies in the memory types used: the FET3568-C/FET3568J-C employs DDR4, while the FET3568-C2/FET3568J-C2 utilizes LPDDR4/LPDDR4X. Additionally, the FET3568-C2/FET3568J-C2 can support higher-capacity RAM (up to 8GB).

2.1 FET3568-C/C2 SoM

FET3568-C SoM

Front

Back

FET3568-C2 SoM

Front

Back

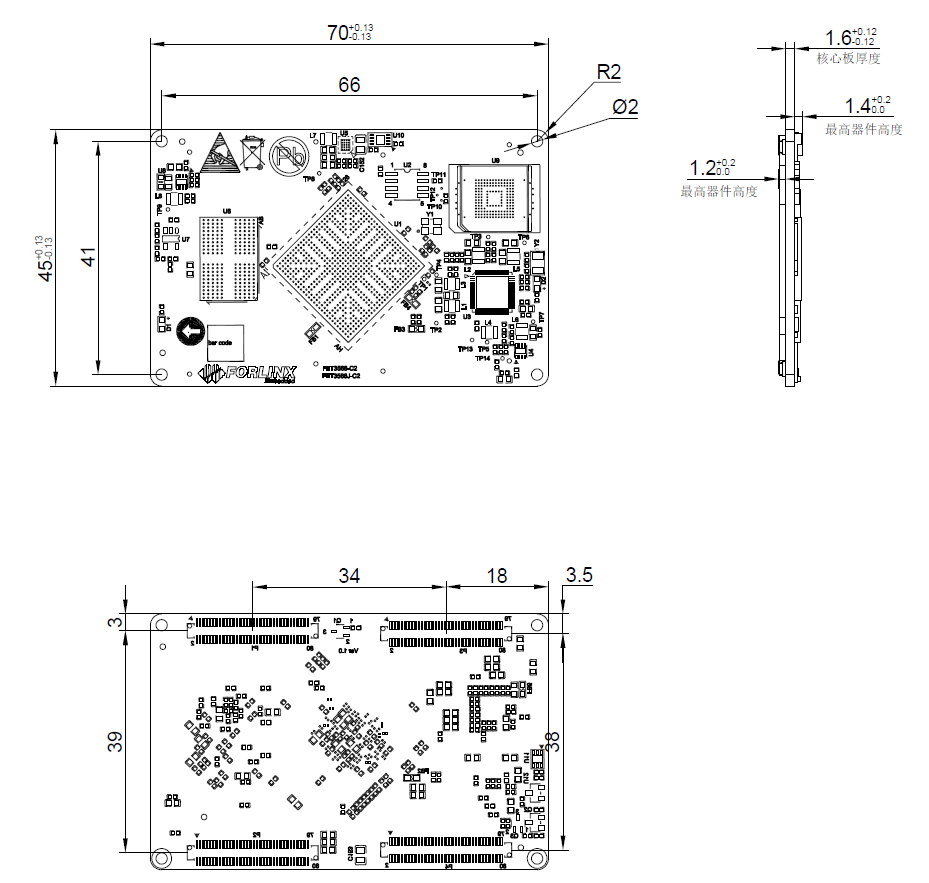

2.2 FET3568-C/ C2 SoM Dimension Diagram

FET3568-C SoM Dimension Diagram

Front, Top, Perspective

FET3568-C2 SoM Dimension Diagram

Front, Top, Perspective

Structure size: 45 mm × 70 mm. The dimensional tolerance is shown in the figure. For more dimensional information, please refer to the user data DXF file.

Plate making process: 1.6mm thickness, 10-layer immersion gold PCB.

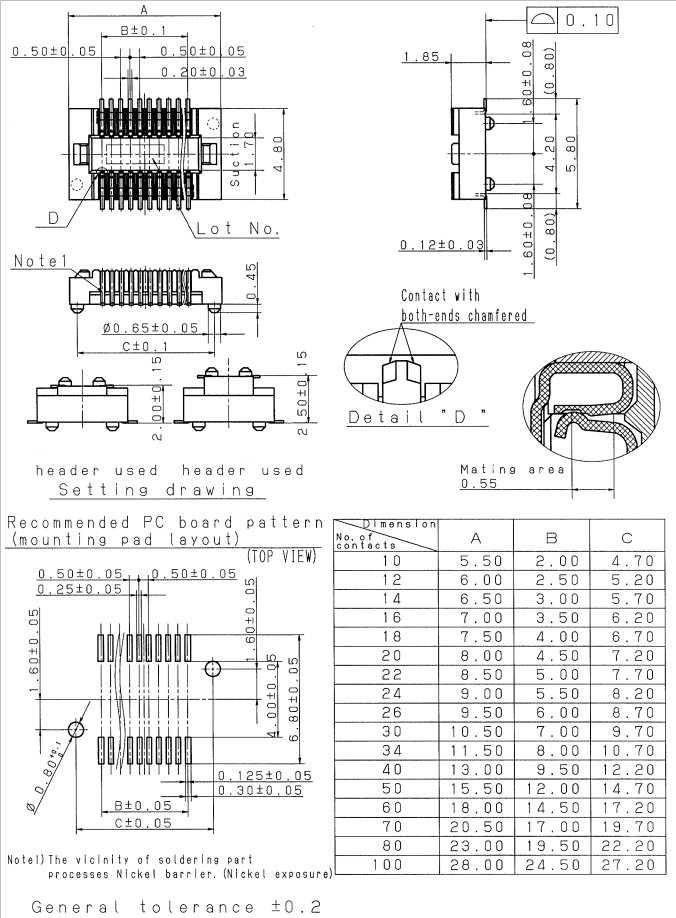

Connectors: Four 0.5mm pitch, 80pin board-to-board connectors. See the appendix for the connector dimension drawing.

SoM installation structure height: 5.4mm (including a SoM and carrier board connector height of 2mm, board thickness of 1.6mm, and the highest device height of the SoM of 1.8mm).

Four mounting holes (2.2mm) are reserved at the four corners of the SoM to facilitate the installation of fixing screws and to improve the reliability of the product connection so that the product can be used in vibration environments.

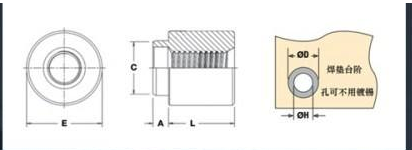

Please refer to the design of the development board and use M2, L=2mm patch nuts on the carrier board. The fixed screw specifications used between the SoM and the carrier board are M2, L=4mm. The specifications of the patch nuts are shown in the following figure:

2.3 Performance Parameters

2.3.1 System Main Frequency

Name |

Specification |

Description |

|||

|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

||

Cortex-A55 |

— |

— |

2.0 |

GHz |

Commercial level |

2.3.2 Power Parameter

Parameter |

Pin Number |

Specification |

Description |

|||

|---|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

|||

Main Power Supply Voltage |

5V |

4.5 |

5.0 |

5.5 |

V |

— |

2.3.3 Operating Environment

Parameter |

Specification |

Description |

||||

|---|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

|||

Operating Temperature |

Operating Environment |

0 |

25 |

+80 |

℃ |

FET3568-C |

Storage Environment |

-40 |

25 |

+125 |

℃ |

||

Operating Temperature |

Operating Environment |

-40 |

25 |

+85 |

℃ |

FET3568J-C |

Storage Environment |

-40 |

25 |

+125 |

℃ |

||

Humidity |

Operating Environment |

10 |

— |

90 |

%RH |

No condensation |

Storage Environment |

5 |

— |

95 |

%RH |

2.3.4 SoM Interface Speed

Parameter* |

Specification |

Description |

|||

|---|---|---|---|---|---|

Minimum |

Typical |

Maximum |

Unit |

||

Serial Port Communication Speed |

— |

115200 |

4M |

bps |

— |

IIC Communication Speed |

— |

100 |

400 |

Kbps |

— |

CAN Communication Speed |

1 |

Mbps |

|||

USB interface speed |

— |

— |

5 |

Gbps |

— |

PCIE interface speed |

— |

— |

8 |

Gbps |

— |

2.3.5 ESD Features

Parameter |

Specification |

Unit |

Application Scope |

|

|---|---|---|---|---|

Minimum |

Maximum |

|||

ESD HBM(ESDA/JEDEC JS-001-2017) |

-500 |

500 |

V |

Signals exported from SoM |

ESD CDM(ESDA/JEDEC JS-002-2018) |

-250 |

250 |

V |

Signals exported from SoM |

Note:

1. The above data is provided by Rockchip;

2. As all the signals exported from SoM are electrostatic sensitive signals, the interfaces should be well protected from static electricity in the carrier board design and the SoM transportation, assembling, and use.

2.4 SoM Interface Speed

FET3568-C/C2 SoM Interfaces:

Function |

Quantity |

Parameter |

|---|---|---|

USB 2.0 |

2 |

USB 2.0 Host, independent port, not multiplexed with USB 3.0 |

USB 3.01 |

2 |

1 x USB 3.0 Host can independently create a USB 2.0 host and use 1 x USB 3.0 OTG, which can also function independently with USB 2.0 OTG. |

SATA1 |

≤3 |

SATA 3.0 up to 6.0 Gb/s with eSATA support |

PCIe 2.11 |

≤1 |

PCIe 2.1 x1, up to 5.0 Gbps, RC Mode |

PCIe 3.0 |

≤2 |

PCIe 3.0, 1x2Lanes or 2x1Lane, up to 8.0 Gbps per Lane; 1Lane supports Root Complex (RC) mode only; 2 Lanes supports Root Complex (RC) and End Point (EP) model. |

Camera |

2 |

Supports 1 x DVP interface; 1 x 4Lanes MIPI-CSI |

MIPI_DSI2 |

2 |

2 x 4 - lane MIPI display serial interfaces, supporting MIPI V1.2 version. The maximum resolution of a single channel is 1920×1080@60Hz, and the maximum resolution of dual channels is 2560×1440@60Hz. Among them, MIPI DSI TX0 is multiplexed with LVDS TX PHY. |

HDMI2 |

1 |

Supports HDMI 2.0 up to 1080p @ 120Hz or 4096x2304 @ 60Hz |

LVDS2 |

1 |

Single channel (4 lanes) supports 1280 * 800 @ 60Hz, multiplexed with MIPI DSI TX0 pin |

eDP2 |

1 |

1 x 4-lane eDP display interface, supports eDP V1.3, and the maximum resolution is 2560 * 1600 @ 60Hz |

RGB2 |

1 |

RGB888 support, resolution up to 1920*1080 |

Ethernet |

≤2 |

Supports 2 x RGMII |

SDIO |

≤2 |

SD0, 4-bit, supports 1.8/3.3 V mode switching and can be used for system programming; SD2, 4-bit, only supports 1.8 V mode |

UART |

≤10 |

Baud rate up to 4Mbps |

SPI |

≤4 |

Supports both master and slave mode |

I2C |

≤5 |

Supports 7bits and 10bits address modes up to 1 Mbit/s |

CAN |

≤3 |

Supports CAN 2.0 B; data rate up to 1 Mbps |

Audio |

≤4 |

1X 8ch I2S/TDM; |

PWM |

≤16 |

Supports up to 16-channel PWM, 32bits timer/counter |

FSPI |

≤1 |

Supports serial NOR Flash/NAND Flash and Boot |

ADC |

≤8 |

The ADC has a sampling range of 0-1.8 V and a sampling resolution of 10 bits. |

Note:

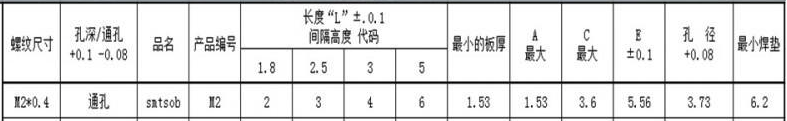

The quantity is marked as the maximum, utilizing a total of 3 groups of SerDes channels. Meanwhile, only 3 functional interfaces can be used simultaneously.

The multiplexing relationships of the 3 groups of SerDes are illustrated in the following diagram:

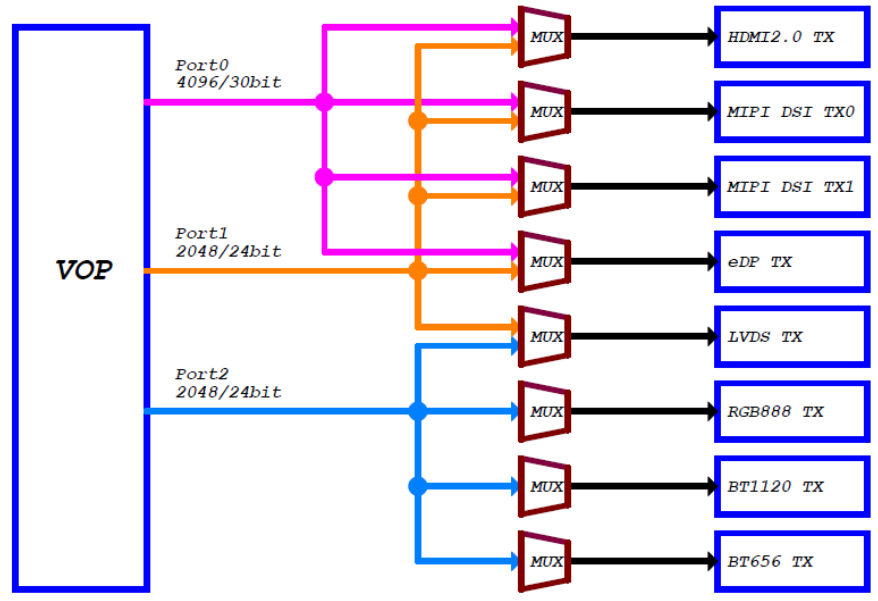

The RK3568 chip has a built-in VOP controller with three Port outputs, that is, the SoM can support up to three display outputs at the same time. The VOP and video interface output paths are shown in the following figure:

The parameters in the table are the theoretical values of hardware design or CPU;

2.5 FET3568-C/C2 SoM Pins Definition

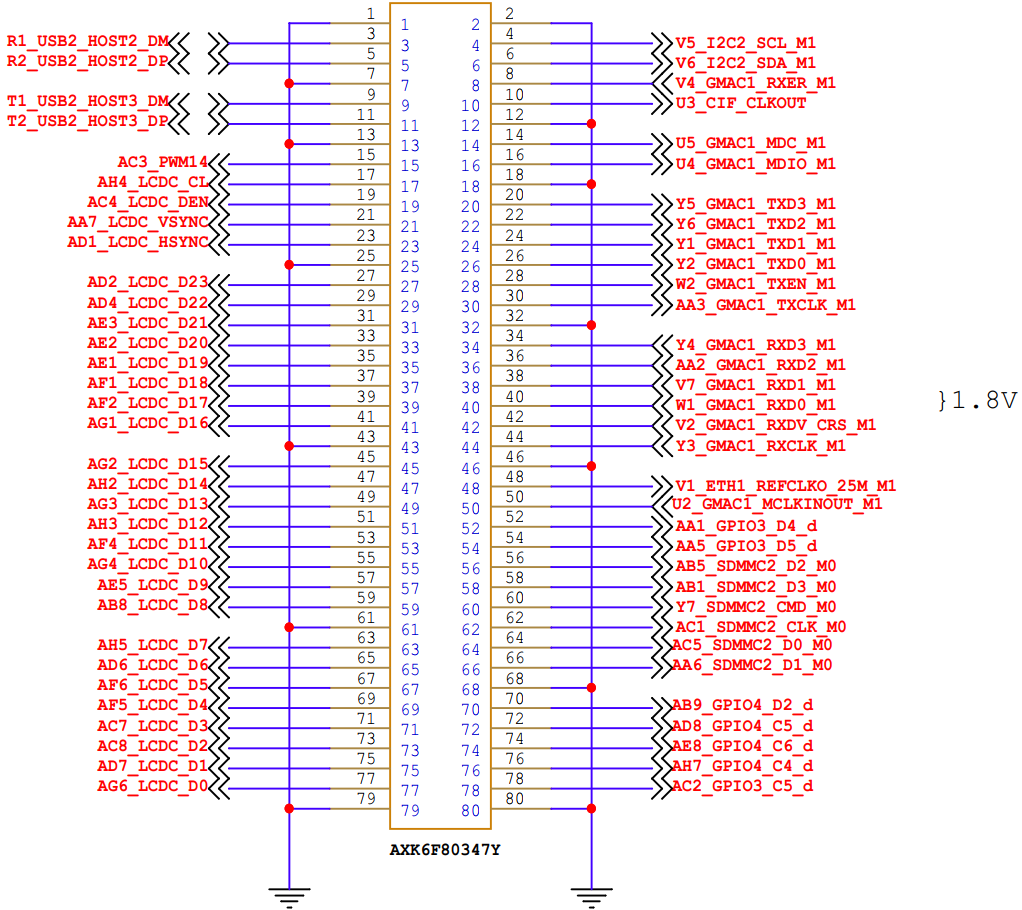

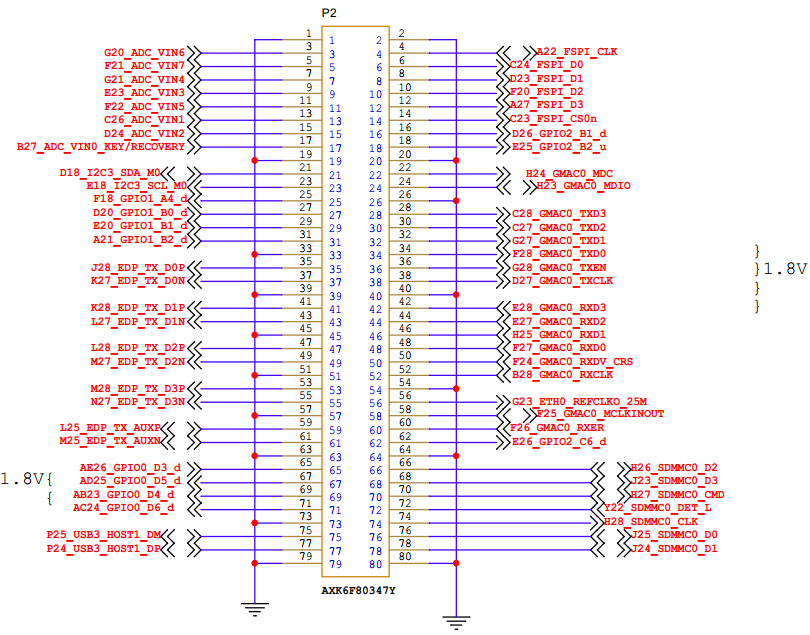

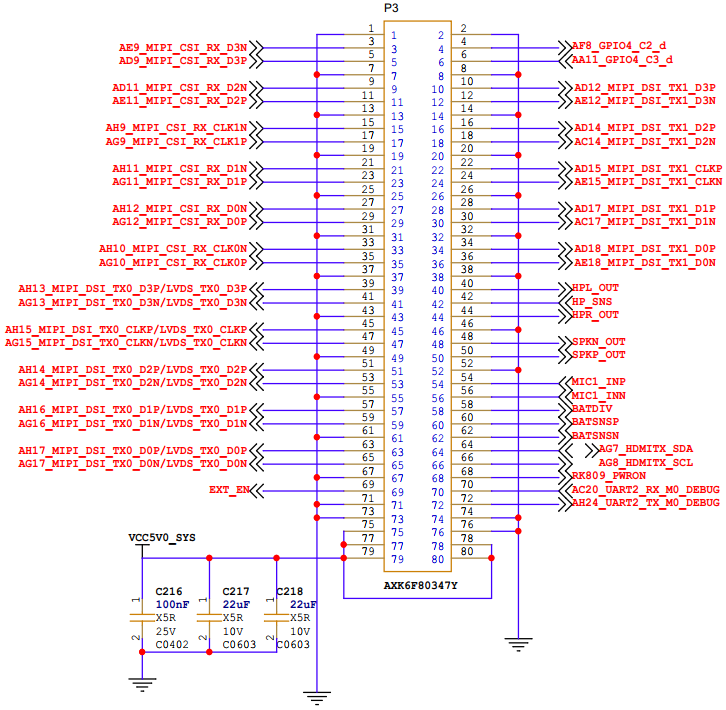

2.5.1 FET3568-C/C2 SoM Pins Schematic

2.5.2 FET3568-C/C2 SoM Pins Description

Note1:

Num ——SoM connector pin no.:

Ball —— CPU pin ball no.

GPIO ——CPU pin general I/O port serial number

Vol —— Pin signal level

Note2:

Signal Name——SoM connector network name

Pin Description—— SoM Pin Signal Descriptions

Default Function——Please don’t make any modifications for all SoM pin functions regulated in the “default functions” of the following table, otherwise, it may have conflicts with the factory driver. Please contact us with any questions in time.

**Note3: **

The pins marked with “Do not use for carrier board” in the “Pin Description” are those used by the SoM, and should not be used in the carrier board design.

Table 1 LEFT_UP(P1) Connector Interface(Odd) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

LU_1 |

- |

GND |

- |

- |

Ground |

GND |

LU_3 |

R1 |

R1_USB2_HOST2_DM |

- |

- |

USB2_HOST2 data- |

USB2_HOST2_DM |

LU_5 |

R2 |

R2_USB2_HOST2_DP |

- |

- |

USB2_HOST2 data+ |

USB2_HOST2_DP |

LU_7 |

- |

GND |

- |

- |

Ground |

GND |

LU_9 |

T1 |

T1_USB2_HOST3_DM |

- |

- |

USB2_HOST3 data- |

USB2_HOST3_DM |

LU_11 |

T2 |

T2_USB2_HOST3_DP |

- |

- |

USB2_HOST3 data+ |

USB2_HOST3_DP |

LU_13 |

- |

GND |

- |

- |

Ground |

GND |

LU_15 |

AC3 |

AC3_PWM14 |

GPIO3_C4 |

3.3V |

PWM14 |

PWM14 |

LU_17 |

AH4 |

AH4_LCDC_CL |

GPIO3_A0 |

3.3V |

LCD clock signal |

SPI2_CLK_M1 |

LU_19 |

AC4 |

AC4_LCDC_DEN |

GPIO3_C3 |

3.3V |

LCD data enable signal |

UART5_RX_M1 |

LU_21 |

AA7 |

AA7_LCDC_VSYNC |

GPIO3_C2 |

3.3V |

LCD field sync signal |

UART5_TX_M1 |

LU_23 |

AD1 |

AD1_LCDC_HSYNC |

GPIO3_C1 |

3.3V |

LCD line synchronization signal |

GPIO3_C1_d |

LU_25 |

- |

GND |

- |

- |

Ground |

GND |

LU_27 |

AD2 |

AD2_LCDC_D23 |

GPIO3_C0 |

3.3V |

LCD Data 23 |

UART3_RX_M1 |

LU_29 |

AD4 |

AD4_LCDC_D22 |

GPIO3_B7 |

3.3V |

LCD Data 22 |

UART3_TX_M1 |

LU_31 |

AE3 |

AE3_LCDC_D21 |

GPIO3_B6 |

3.3V |

LCD Data 21 |

GPIO3_B6_d |

LU_33 |

AE2 |

AE2_LCDC_D20 |

GPIO3_B5 |

3.3V |

LCD Data 20 |

GPIO3_B5_d |

LU_35 |

AE1 |

AE1_LCDC_D19 |

GPIO3_B4 |

3.3V |

LCD Data 19 |

GPIO3_B4_d |

LU_37 |

AF1 |

AF1_LCDC_D18 |

GPIO3_B3 |

3.3V |

LCD Data 18 |

GPIO3_B3_d |

LU_39 |

AF2 |

AF2_LCDC_D17 |

GPIO3_B2 |

3.3V |

LCD Data 17 |

UART4_TX_M1 |

LU_41 |

AG1 |

AG1_LCDC_D16 |

GPIO3_B1 |

3.3V |

LCD Data 16 |

UART4_RX_M1 |

LU_43 |

- |

GND |

- |

- |

Ground |

GND |

LU_45 |

AG2 |

AG2_LCDC_D15 |

GPIO3_B0 |

3.3V |

LCD Data 15 |

GPIO3_B0_d |

LU_47 |

AH2 |

AH2_LCDC_D14 |

GPIO3_A7 |

3.3V |

LCD Data 14 |

GPIO3_A7_d |

LU_49 |

AG3 |

AG3_LCDC_D13 |

GPIO3_A6 |

3.3V |

LCD Data 13 |

GPIO3_A6_d |

LU_51 |

AH3 |

AH3_LCDC_D12 |

GPIO3_A5 |

3.3V |

LCD Data 12 |

GPIO3_A5_d |

LU_53 |

AF4 |

AF4_LCDC_D11 |

GPIO3_A4 |

3.3V |

LCD Data 11 |

GPIO3_A4_d |

LU_55 |

AG4 |

AG4_LCDC_D10 |

GPIO3_A3 |

3.3V |

LCD Data 10 |

GPIO3_A3_d |

LU_57 |

AE5 |

AE5_LCDC_D9 |

GPIO3_A2 |

3.3V |

LCD Data 9 |

GPIO3_A2_d |

LU_59 |

AB8 |

AB8_LCDC_D8 |

GPIO3_A1 |

3.3V |

LCD Data 8 |

GPIO3_A1_d |

LU_61 |

- |

GND |

- |

- |

Ground |

GND |

LU_63 |

AH5 |

AH5_LCDC_D7 |

GPIO2_D7 |

3.3V |

LCD Data 7 |

SPI2_MISO_M1 |

LU_65 |

AD6 |

AD6_LCDC_D6 |

GPIO2_D6 |

3.3V |

LCD Data 6 |

SPI2_MOSI_M1 |

LU_67 |

AF6 |

AF6_LCDC_D5 |

GPIO2_D5 |

3.3V |

LCD Data 5 |

SPI2_CS0_M1 |

LU_69 |

AF5 |

AF5_LCDC_D4 |

GPIO2_D4 |

3.3V |

LCD Data 4 |

SPI2_CS1_M1 |

LU_71 |

AC7 |

AC7_LCDC_D3 |

GPIO2_D3 |

3.3V |

LCD Data 3 |

SPI0_CLK_M1 |

LU_73 |

AC8 |

AC8_LCDC_D2 |

GPIO2_D2 |

3.3V |

LCD Data 2 |

SPI0_CS0_M1 |

LU_75 |

AD7 |

AD7_LCDC_D1 |

GPIO2_D1 |

3.3V |

LCD Data 1 |

SPI0_MOSI_M1 |

LU_77 |

AG6 |

AG6_LCDC_D0 |

GPIO2_D0 |

3.3V |

LCD Data 0 |

SPI0_MISO_M1 |

LU_79 |

- |

GND |

- |

- |

Ground |

GND |

Table 2 LEFT_UP(P1) Connector Interface(Even) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

LU_2 |

- |

GND |

- |

- |

Ground |

GND |

LU_4 |

V5 |

V5_I2C2_SCL_M1 |

GPIO4_B5 |

1.8V |

I2C2 serial clock signal |

I2C2_SCL_M1 |

LU_6 |

V6 |

V6_I2C2_SDA_M1 |

GPIO4_B4 |

1.8V |

I2C2 serial data signal |

I2C2_SDA_M1 |

LU_8 |

V4 |

V4_GMAC1_RXER_M1 |

GPIO4_B2 |

1.8V |

GMAC1 receive error |

CAM0_PWRDN |

LU_10 |

U3 |

U3_CIF_CLKOUT |

GPIO4_C0 |

1.8V |

Camera reference clock output |

CIF_CLKOUT |

LU_12 |

- |

GND |

- |

- |

Ground |

GND |

LU_14 |

U5 |

U5_GMAC1_MDC_M1 |

GPIO4_B6 |

1.8V |

GMAC1 management data reference clock |

GMAC1_MDC_M1 |

LU_16 |

U4 |

U4_GMAC1_MDIO_M1 |

GPIO4_B7 |

1.8V |

GMAC1 management data input/output |

GMAC1_MDIO_M1 |

LU_18 |

- |

GND |

- |

- |

Ground |

GND |

LU_20 |

Y5 |

Y5_GMAC1_TXD3_M1 |

GPIO3_D7 |

1.8V |

GMAC1 sends data 3 |

GMAC1_TXD3_M1 |

LU_22 |

Y6 |

Y6_GMAC1_TXD2_M1 |

GPIO3_D6 |

1.8V |

GMAC1 sends data 2 |

GMAC1_TXD2_M1 |

LU_24 |

Y1 |

Y1_GMAC1_TXD1_M1 |

GPIO4_A5 |

1.8V |

GMAC1 sends data 1 |

GMAC1_TXD1_M1 |

LU_26 |

Y2 |

Y2_GMAC1_TXD0_M1 |

GPIO4_A4 |

1.8V |

GMAC1 sends data 0 |

GMAC1_TXD0_M1 |

LU_28 |

W2 |

W2_GMAC1_TXEN_M1 |

GPIO4_A6 |

1.8V |

GMAC1 sends control signal |

GMAC1_TXEN_M1 |

LU_30 |

AA3 |

AA3_GMAC1_TXCLK_M1 |

GPIO4_A0 |

1.8V |

GMAC1 sends reference clock |

GMAC1_TXCLK_M1 |

LU_32 |

- |

GND |

- |

- |

Ground |

GND |

LU_34 |

Y4 |

Y4_GMAC1_RXD3_M1 |

GPIO4_A2 |

1.8V |

GMAC1 receive data 3 |

GMAC1_RXD3_M1 |

LU_36 |

AA2 |

AA2_GMAC1_RXD2_M1 |

GPIO4_A1 |

1.8V |

GMAC1 receive data 2 |

GMAC1_RXD2_M1 |

LU_38 |

V7 |

V7_GMAC1_RXD1_M1 |

GPIO4_B0 |

1.8V |

GMAC1 receive data 1 |

GMAC1_RXD1_M1 |

LU_40 |

W1 |

W1_GMAC1_RXD0_M1 |

GPIO4_A7 |

1.8V |

GMAC1 receive data 0 |

GMAC1_RXD0_M1 |

LU_42 |

V2 |

V2_GMAC1_RXDV_CRS_M1 |

GPIO4_B1 |

1.8V |

GMAC1 receiving data is valid |

GMAC1_RXDV_CRS_M1 |

LU_44 |

Y3 |

Y3_GMAC1_RXCLK_M1 |

GPIO4_A3 |

1.8V |

GMAC1 receive reference clock |

GMAC1_RXCLK_M1 |

LU_46 |

- |

GND |

- |

- |

Ground |

GND |

LU_48 |

V1 |

V1_ETH1_REFCLKO_25M_M1 |

GPIO4_B3 |

1.8V |

Output 25Mhz to PHY |

ETH1_REFCLKO_25M_M1 |

LU_50 |

U2 |

U2_GMAC1_MCLKINOUT_M1 |

GPIO4_C1 |

1.8V |

125MHz inputs to GMAC1 |

GMAC1_MCLKINOUT_M1 |

LU_52 |

AA1 |

AA1_GPIO3_D4_d |

GPIO3_D4 |

1.8V |

General IO |

WIFI_REG_ON |

LU_54 |

AA5 |

AA5_GPIO3_D5_d |

GPIO3_D5 |

1.8V |

General IO |

BT_REG_ON |

LU_56 |

AB5 |

AB5_SDMMC2_D2 |

GPIO3_D0 |

1.8V |

SDMMC2 data bit 2- |

SDMMC2_D2 |

LU_58 |

AB1 |

AB1_SDMMC2_D3 |

GPIO3_D1 |

1.8V |

SDMMC2 data bit 3- |

SDMMC2_D3 |

LU_60 |

Y7 |

Y7_SDMMC2_CMD |

GPIO3_D2 |

1.8V |

SDMMC2 command signal |

SDMMC2_CMD |

LU_62 |

AC1 |

AC1_SDMMC2_CLK |

GPIO3_D3 |

1.8V |

SDMMC2 clock signal |

SDMMC2_CLK |

LU_64 |

AC5 |

AC5_SDMMC2_D0 |

GPIO3_C6 |

1.8V |

SDMMC2 data bit 0- |

SDMMC2_D0 |

LU_66 |

AA6 |

AA6_SDMMC2_D1 |

GPIO3_C7 |

1.8V |

SDMMC2 data bit 1- |

SDMMC2_D1 |

LU_68 |

- |

GND |

- |

- |

Ground |

GND |

LU_70 |

AB9 |

AB9_GPIO4_D2_d |

GPIO4_D2 |

3.3V |

General IO |

PHONE_DET |

LU_72 |

AD8 |

AD8_GPIO4_C5_d |

GPIO4_C5 |

3.3V |

General IO |

TP_RST |

LU_74 |

AE8 |

AE8_GPIO4_C6_d |

GPIO4_C6 |

3.3V |

General IO |

TP_INT |

LU_76 |

AH7 |

AH7_GPIO4_C4_d |

GPIO4_C4 |

3.3V |

General IO |

EDP_HPD_M0 |

LU_78 |

AC2 |

AC2_GPIO3_C5_d |

GPIO3_C5 |

3.3V |

General IO |

LCD_nPWREN |

LU_80 |

- |

GND |

- |

- |

Ground |

GND |

Table 3 RIGHT_UP(P2) Connector Interface(Odd) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

RU_1 |

- |

GND |

- |

- |

Ground |

GND |

RU_3 |

G20 |

G20_ADC_VIN6 |

- |

1.8V |

General ADC6 |

ADC_VIN6 |

RU_5 |

F21 |

F21_ADC_VIN7 |

- |

1.8V |

General ADC7 |

ADC_VIN7 |

RU_7 |

G21 |

G21_ADC_VIN4 |

- |

1.8V |

General ADC4 |

ADC_VIN4 |

RU_9 |

E23 |

E23_ADC_VIN3 |

- |

1.8V |

General ADC3 |

ADC_VIN3 |

RU_11 |

F22 |

F22_ADC_VIN5 |

- |

1.8V |

General ADC5 |

ADC_VIN5 |

RU_13 |

C26 |

C26_ADC_VIN1 |

- |

1.8V |

General ADC1 |

ADC_VIN1 |

RU_15 |

D24 |

D24_ADC_VIN2 |

- |

1.8V |

General ADC2 |

ADC_VIN2 |

RU_17 |

B27 |

B27_ADC_VIN0_KEY/RECOVERY |

- |

1.8V |

General ADC0 |

ADC_VIN0_KEY/RECOVERY |

RU_19 |

- |

GND |

- |

- |

Ground |

GND |

RU_21 |

D18 |

D18_I2C3_SDA_M0 |

GPIO1_A0 |

3.3V |

I2C3 serial data signal |

I2C3_SDA_M0 |

RU_23 |

E18 |

E18_I2C3_SCL_M0 |

GPIO1_A1 |

3.3V |

I2C3 serial clock signal |

I2C3_SCL_M0 |

RU_25 |

F18 |

F18_GPIO1_A4_d |

GPIO1_A4 |

3.3V |

General IO |

TP_INT_LVDS |

RU_27 |

D20 |

D20_GPIO1_B0_d |

GPIO1_B0 |

3.3V |

General IO |

TP_RST_LVDS |

RU_29 |

E20 |

E20_GPIO1_B1_d |

GPIO1_B1 |

3.3V |

General IO |

5G_PWR |

RU_31 |

A21 |

A21_GPIO1_B2_d |

GPIO1_B2 |

3.3V |

General IO |

5G_RESET |

RU_33 |

- |

GND |

- |

- |

Ground |

GND |

RU_35 |

J28 |

J28_EDP_TX_D0P |

- |

- |

EDP Data 0+ |

EDP_TX_D0P |

RU_37 |

K27 |

K27_EDP_TX_D0N |

- |

- |

EDP Data 0- |

EDP_TX_D0N |

RU_39 |

- |

GND |

- |

- |

Ground |

GND |

RU_41 |

K28 |

K28_EDP_TX_D1P |

- |

- |

EDP Data 1+ |

EDP_TX_D1P |

RU_43 |

L27 |

L27_EDP_TX_D1N |

- |

- |

EDP Data 1- |

EDP_TX_D1N |

RU_45 |

- |

GND |

- |

- |

Ground |

GND |

RU_47 |

L28 |

L28_EDP_TX_D2P |

- |

- |

EDP Data 2+ |

EDP_TX_D2P |

RU_49 |

M27 |

M27_EDP_TX_D2N |

- |

- |

EDP Data 2- |

EDP_TX_D2N |

RU_51 |

- |

GND |

- |

- |

Ground |

GND |

RU_53 |

M28 |

M28_EDP_TX_D3P |

- |

- |

EDP Data 3+ |

EDP_TX_D3P |

RU_55 |

N27 |

N27_EDP_TX_D3N |

- |

- |

EDP Data 3- |

EDP_TX_D3N |

RU_57 |

- |

GND |

- |

- |

Ground |

GND |

RU_59 |

L25 |

L25_EDP_TX_AUXP |

- |

- |

EDP auxiliary data+ |

EDP_TX_AUXP |

RU_61 |

M25 |

M25_EDP_TX_AUXN |

- |

- |

EDP auxiliary data- |

EDP_TX_AUXN |

RU_63 |

- |

GND |

- |

- |

Ground |

GND |

RU_65 |

AE26 |

AE26_GPIO0_D3_d |

GPIO0_D3 |

1.8V |

General IO |

BT_HOST_WAKE_B |

RU_67 |

AD25 |

AD25_GPIO0_D5_d |

GPIO0_D5 |

1.8V |

General IO |

BT_WAKE_B |

RU_69 |

AB23 |

AB23_GPIO0_D4_d |

GPIO0_D4 |

1.8V |

General IO |

WIFI_HOST_WAKE_B |

RU_71 |

AC24 |

AC24_GPIO0_D6_d |

GPIO0_D6 |

1.8V |

General IO |

CAM0_nRST |

RU_73 |

- |

GND |

- |

- |

Ground |

GND |

RU_75 |

P25 |

P25_USB3_HOST1_DM |

- |

- |

USB3_HOST1 data- |

USB3_HOST1_DM |

RU_77 |

P24 |

P24_USB3_HOST1_DP |

- |

- |

USB3_HOST1 data+ |

USB3_HOST1_DP |

RU_79 |

- |

GND |

- |

- |

Ground |

GNDGND |

Table 4 RIGHT_UP(P2) Connector Interface(Even) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

RU_2 |

- |

GND |

- |

- |

Ground |

GND |

RU_4 |

A22 |

A22_FSPI_CLK |

GPIO1_D0 |

1.8V |

FSPI reference clock |

FSPI_CLK |

RU_6 |

C24 |

C24_FSPI_D0 |

GPIO1_D1 |

1.8V |

FSPI Data 0 |

FSPI_D0 |

RU_8 |

D23 |

D23_FSPI_D1 |

GPIO1_D2 |

1.8V |

FSPI Data 1 |

FSPI_D1 |

RU_10 |

F20 |

F20_FSPI_D2 |

GPIO1_C7 |

1.8V |

FSPI Data 2 |

FSPI_D2 |

RU_12 |

A27 |

A27_FSPI_D3 |

GPIO1_D4 |

1.8V |

FSPI Data 3 |

FSPI_D3 |

RU_14 |

C23 |

C23_FSPI_CS0n |

GPIO1_D3 |

1.8V |

FSPI chip select signal 0 |

FSPI_CS0n |

RU_16 |

D26 |

D26_GPIO2_B1_d |

GPIO2_B1 |

1.8V |

General IO |

UART8_RTSn_M0 |

RU_18 |

E25 |

E25_GPIO2_B2_u |

GPIO2_B2 |

1.8V |

General IO |

UART8_CTSn_M0 |

RU_20 |

- |

GND |

- |

- |

Ground |

GND |

RU_22 |

H24 |

H24_GMAC0_MDC |

GPIO2_C3 |

1.8V |

GMAC0 management data reference clock |

GMAC0_MDC |

RU_24 |

H23 |

H23_GMAC0_MDIO |

GPIO2_C4 |

1.8V |

GMAC0 management data input/output |

GMAC0_MDIO |

RU_26 |

- |

GND |

- |

- |

Ground |

GND |

RU_28 |

C28 |

C28_GMAC0_TXD3 |

GPIO2_A7 |

1.8V |

GMAC0 sends data 3 |

GMAC0_TXD3 |

RU_30 |

C27 |

C27_GMAC0_TXD2 |

GPIO2_A6 |

1.8V |

GMAC0 sends data 2 |

GMAC0_TXD2 |

RU_32 |

G27 |

G27_GMAC0_TXD1 |

GPIO2_B4 |

1.8V |

GMAC0 sends data 1 |

GMAC0_TXD1 |

RU_34 |

F28 |

F28_GMAC0_TXD0 |

GPIO2_B3 |

1.8V |

GMAC0 sends data 0 |

GMAC0_TXD0 |

RU_36 |

G28 |

G28_GMAC0_TXEN |

GPIO2_B5 |

1.8V |

GMAC0 sends control signal |

GMAC0_TXEN |

RU_38 |

D27 |

D27_GMAC0_TXCLK |

GPIO2_B0 |

1.8V |

GMAC0 sends reference clock |

GMAC0_TXCLK |

RU_40 |

- |

GND |

- |

- |

Ground |

GND |

RU_42 |

E28 |

E28_GMAC0_RXD3 |

GPIO2_A4 |

1.8V |

GMAC0 receive data 3 |

GMAC0_RXD3 |

RU_44 |

E27 |

E27_GMAC0_RXD2 |

GPIO2_A3 |

1.8V |

GMAC0 receive data 2 |

GMAC0_RXD2 |

RU_46 |

H25 |

H25_GMAC0_RXD1 |

GPIO2_B7 |

1.8V |

GMAC0 receive data 1 |

GMAC0_RXD1 |

RU_48 |

F27 |

F27_GMAC0_RXD0 |

GPIO2_B6 |

1.8V |

GMAC0 receive data 0 |

GMAC0_RXD0 |

RU_50 |

F24 |

F24_GMAC0_RXDV_CRS |

GPIO2_C0 |

1.8V |

GMAC0 receiving data is valid |

GMAC0_RXDV_CRS |

RU_52 |

B28 |

B28_GMAC0_RXCLK |

GPIO2_A5 |

1.8V |

GMAC0 receive reference clock |

GMAC0_RXCLK |

RU_54 |

- |

GND |

- |

- |

Ground |

GND |

RU_56 |

G23 |

G23_ETH0_REFCLKO_25M |

GPIO2_C1 |

1.8V |

Output 25Mhz to PHY |

ETH0_REFCLKO_25M |

RU_58 |

F25 |

F25_GMAC0_MCLKINOUT |

GPIO2_C2 |

1.8V |

125MHz inputs to GMAC0 |

GMAC0_MCLKINOUT |

RU_60 |

F26 |

F26_GMAC0_RXER |

GPIO2_C5 |

1.8V |

GMAC0 receive error |

UART8_TX_M0 |

RU_62 |

E26 |

E26_GPIO2_C6_d |

GPIO2_C6 |

1.8V |

General IO |

UART8_RX_M0 |

RU_64 |

- |

GND |

- |

- |

Ground |

GND |

RU_66 |

H26 |

H26_SDMMC0_D2 |

GPIO1_D7 |

3.3V |

SDMMC0 data bit 2- |

SDMMC0_D2 |

RU_68 |

J23 |

J23_SDMMC0_D3 |

GPIO2_A0 |

3.3V |

SDMMC0 data bit 3- |

SDMMC0_D3 |

RU_70 |

H27 |

H27_SDMMC0_CMD |

GPIO2_A1 |

3.3V |

SDMMC0 command signal |

SDMMC0_CMD |

RU_72 |

Y22 |

Y22_SDMMC0_DET_L |

GPIO0_A4 |

3.3V |

SDMMC0 card detection signal |

SDMMC0_DET_L |

RU_74 |

H28 |

H28_SDMMC0_CLK |

GPIO2_A2 |

3.3V |

SDMMC0 clock signal |

SDMMC0_CLK |

RU_76 |

J25 |

J25_SDMMC0_D0 |

GPIO1_D5 |

3.3V |

SDMMC0 data bit 0- |

SDMMC0_D0 |

RU_78 |

J24 |

J24_SDMMC0_D1 |

GPIO1_D6 |

3.3V |

SDMMC0 data bit 1- |

SDMMC0_D1 |

RU_80 |

- |

GND |

- |

- |

Ground |

GND |

Table 5 LEFT _ DOWN (P3) Connector Interface (Odd) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

LD_1 |

- |

GND |

- |

- |

Ground |

GND |

LD_3 |

AE9 |

AE9_MIPI_CSI_RX_D3N |

- |

- |

MIPI _ CSI differential data 3- |

MIPI_CSI_RX_D3N |

LD_5 |

AD9 |

AD9_MIPI_CSI_RX_D3P |

- |

- |

MIPI _ CSI differential data 3 + |

MIPI_CSI_RX_D3P |

LD_7 |

- |

GND |

- |

- |

Ground |

GND |

LD_9 |

AD11 |

AD11_MIPI_CSI_RX_D2N |

- |

- |

MIPI _ CSI differential data 2- |

MIPI_CSI_RX_D2N |

LD_11 |

AE11 |

AE11_MIPI_CSI_RX_D2P |

- |

- |

MIPI _ CSI differential data 2 + |

MIPI_CSI_RX_D2P |

LD_13 |

- |

GND |

- |

- |

Ground |

GND |

LD_15 |

AH9 |

AH9_MIPI_CSI_RX_CLK1N |

- |

- |

MIPI _ CSI differential clock signal 1- |

MIPI_CSI_RX_CLK1N |

LD_17 |

AG9 |

AG9_MIPI_CSI_RX_CLK1P |

- |

- |

MIPI _ CSI differential clock signal 1+ |

MIPI_CSI_RX_CLK1P |

LD_19 |

- |

GND |

- |

- |

Ground |

GND |

LD_21 |

AH11 |

AH11_MIPI_CSI_RX_D1N |

- |

- |

MIPI _ CSI differential data 1- |

MIPI_CSI_RX_D1N |

LD_23 |

AG11 |

AG11_MIPI_CSI_RX_D1P |

- |

- |

MIPI _ CSI differential data 1 + |

MIPI_CSI_RX_D1P |

LD_25 |

- |

GND |

- |

- |

Ground |

GND |

LD_27 |

AH12 |

AH12_MIPI_CSI_RX_D0N |

- |

- |

MIPI _ CSI differential data 0- |

MIPI_CSI_RX_D0N |

LD_29 |

AG12 |

AG12_MIPI_CSI_RX_D0P |

- |

- |

MIPI _ CSI differential data 0 + |

MIPI_CSI_RX_D0P |

LD_31 |

- |

GND |

- |

- |

Ground |

GND |

LD_33 |

AH10 |

AH10_MIPI_CSI_RX_CLK0N |

- |

- |

MIPI _ CSI differential clock signal 0- |

MIPI_CSI_RX_CLK0N |

LD_35 |

AG10 |

AG10_MIPI_CSI_RX_CLK0P |

- |

- |

MIPI _ CSI differential clock signal 0+ |

MIPI_CSI_RX_CLK0P |

LD_37 |

- |

GND |

- |

- |

Ground |

GND |

LD_39 |

AH13 |

AH13_MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

- |

- |

LVDS differential data 3+ |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

LD_41 |

AG13 |

AG13_MIPI_DSI_TX0_D3N/LVDS_TX0_D3N |

- |

- |

LVDS differential data 3- |

MIPI_DSI_TX0_D3N/LVDS_TX0_D3N |

LD_43 |

- |

GND |

- |

- |

Ground |

GND |

LD_45 |

AH15 |

AH15_MIPI_DSI_TX0_CLKP/LVDS_TX0_CLKP |

- |

- |

LVDS Differential Clock Signals+ |

MIPI_DSI_TX0_CLKP/LVDS_TX0_CLKP |

LD_47 |

AG15 |

AG15_MIPI_DSI_TX0_CLKN/LVDS_TX0_CLKN |

- |

- |

LVDS Differential Clock Signals- |

MIPI_DSI_TX0_CLKN/LVDS_TX0_CLKN |

LD_49 |

- |

GND |

- |

- |

Ground |

GND |

LD_51 |

AH14 |

AH14_MIPI_DSI_TX0_D2P/LVDS_TX0_D2P |

- |

- |

LVDS differential data 2+ |

MIPI_DSI_TX0_D2P/LVDS_TX0_D2P |

LD_53 |

AG14 |

AG14_MIPI_DSI_TX0_D2N/LVDS_TX0_D2N |

- |

- |

LVDS differential data 2- |

MIPI_DSI_TX0_D2N/LVDS_TX0_D2N |

LD_55 |

- |

GND |

- |

- |

Ground |

GND |

LD_57 |

AH16 |

AH16_MIPI_DSI_TX0_D1P/LVDS_TX0_D1P |

- |

- |

LVDS differential data 1+ |

MIPI_DSI_TX0_D1P/LVDS_TX0_D1P |

LD_59 |

AG16 |

AG16_MIPI_DSI_TX0_D1N/LVDS_TX0_D1N |

- |

- |

LVDS differential data 1- |

MIPI_DSI_TX0_D1N/LVDS_TX0_D1N |

LD_61 |

- |

GND |

- |

- |

Ground |

GND |

LD_63 |

AH17 |

AH17_MIPI_DSI_TX0_D0P/LVDS_TX0_D0P |

- |

- |

LVDS differential data 0+ |

MIPI_DSI_TX0_D0P/LVDS_TX0_D0P |

LD_65 |

AG17 |

AG17_MIPI_DSI_TX0_D0N/LVDS_TX0_D0N |

- |

- |

LVDS differential data 0- |

MIPI_DSI_TX0_D0N/LVDS_TX0_D0N |

LD_67 |

- |

GND |

- |

- |

Ground |

GND |

LD_69 |

- |

EXT_EN |

- |

- |

External power enable Signal |

EXT_EN |

LD_71 |

- |

GND |

- |

- |

Ground |

GND |

LD_73 |

- |

GND |

- |

- |

Ground |

GND |

LD_75 |

- |

5V |

- |

5V |

5V |

5V |

LD_77 |

- |

5V |

- |

5V |

5V |

5V |

LD_79 |

- |

5V |

- |

5V |

5V |

Table 6 LEFT _ DOWN (P3) Connector Interface (Even) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

LD_2 |

- |

GND |

- |

- |

Ground |

GND |

LD_4 |

AF8 |

AF8_GPIO4_C2_d |

GPIO4_C2 |

3.3V |

General IO |

CAN1_RX_M1 |

LD_6 |

AA11 |

AA11_GPIO4_C3_d |

GPIO4_C3 |

3.3V |

General IO |

CAN1_TX_M1 |

LD_8 |

- |

GND |

- |

- |

Ground |

GND |

LD_10 |

AD12 |

AD12_MIPI_DSI_TX1_D3P |

- |

- |

MIPI _ CSI differential data 3 + |

MIPI_DSI_TX1_D3P |

LD_12 |

AE12 |

AE12_MIPI_DSI_TX1_D3N |

- |

- |

MIPI _ CSI differential data 3- |

MIPI_DSI_TX1_D3N |

LD_14 |

- |

GND |

- |

- |

Ground |

GND |

LD_16 |

AD14 |

AD14_MIPI_DSI_TX1_D2P |

- |

- |

MIPI _ CSI differential data 2+ |

MIPI_DSI_TX1_D2P |

LD_18 |

AC14 |

AC14_MIPI_DSI_TX1_D2N |

- |

- |

MIPI _ CSI differential data 2- |

MIPI_DSI_TX1_D2N |

LD_20 |

- |

GND |

- |

- |

Ground |

GND |

LD_22 |

AD15 |

AD15_MIPI_DSI_TX1_CLKP |

- |

- |

MIPI _ CSI differential clock signal+ |

MIPI_DSI_TX1_CLKP |

LD_24 |

AE15 |

AE15_MIPI_DSI_TX1_CLKN |

- |

- |

MIPI _ CSI differential clock signal- |

MIPI_DSI_TX1_CLKN |

LD_26 |

- |

GND |

- |

- |

Ground |

GND |

LD_28 |

AD17 |

AD17_MIPI_DSI_TX1_D1P |

- |

- |

MIPI _ CSI differential data 1 + |

MIPI_DSI_TX1_D1P |

LD_30 |

AC17 |

AC17_MIPI_DSI_TX1_D1N |

- |

- |

MIPI _ CSI differential data 1- |

MIPI_DSI_TX1_D1N |

LD_32 |

- |

GND |

- |

- |

Ground |

GND |

LD_34 |

AD18 |

AD18_MIPI_DSI_TX1_D0P |

- |

- |

MIPI _ CSI differential data 0 + |

MIPI_DSI_TX1_D0P |

LD_36 |

AE18 |

AE18_MIPI_DSI_TX1_D0N |

- |

- |

MIPI _ CSI differential data 0- |

MIPI_DSI_TX1_D0N |

LD_38 |

- |

GND |

- |

- |

Ground |

GND |

LD_40 |

HPL |

HPL_OUT |

- |

- |

HP left channel Output |

HPL_OUT |

LD_42 |

HP |

HP_SNS |

- |

- |

HP signal reference ground |

HP_SNS |

LD_44 |

HPR |

HPR_OUT |

- |

- |

HP right channel Output |

HPR_OUT |

LD_46 |

- |

GND |

- |

- |

Ground |

GND |

LD_48 |

SPKN |

SPKN_OUT |

- |

- |

SPK differential signal- |

SPKN_OUT |

LD_50 |

SPKP |

SPKP_OUT |

- |

- |

SPK differential signal+ |

SPKP_OUT |

LD_52 |

- |

GND |

- |

- |

Ground |

GND |

LD_54 |

MIC1 |

MIC1_INP |

- |

- |

MIC differential signal+ |

MIC1_INP |

LD_56 |

MIC1 |

MIC1_INN |

- |

- |

MIC differential signal- |

MIC1_INN |

LD_58 |

- |

BATDIV |

- |

- |

Lithium battery voltage input signal |

BATDIV |

LD_60 |

- |

BATSNSP |

- |

- |

Battery charging and discharging current detection signal + |

BATSNSP |

LD_62 |

- |

BATSNSN |

- |

- |

Battery charging and discharging current detection signal- |

BATSNSN |

LD_64 |

AG7 |

AG7_HDMITX_SDA |

- |

- |

HDMI serial data |

HDMITX_SDA |

LD_66 |

AG8 |

AG8_HDMITX_SCL |

- |

- |

HDMI Serial clock |

HDMITX_SCL |

LD_68 |

RK809 |

RK809_PWRON |

- |

- |

Power On/Off signal |

PWRON |

LD_70 |

AC20 |

AC20_UART2_RX_M0_DEBUG |

GPIO0_D0 |

3.3V |

UART2 receiving |

UART2_RX_M0 |

LD_72 |

AH24 |

AH24_UART2_TX_M0_DEBUG |

GPIO0_D1 |

3.3V |

UART2 sending |

UART2_TX_M0 |

LD_74 |

- |

GND |

- |

- |

Ground |

GND |

LD_76 |

- |

GND |

- |

- |

Ground |

GND |

LD_78 |

- |

5V |

- |

5V |

5V |

5V |

LD_80 |

- |

5V |

- |

5V |

5V |

5V |

Table 7 RIGHT _ DOWN (P4) Connector Interface (Odd) Pin Definition

Num** |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

RD_1 |

- |

GND |

- |

- |

Ground |

- |

RD_3 |

P27 |

P27_USB3_OTG0_DP |

- |

- |

USB3_OTG0 data+ |

USB3_OTG0_DP |

RD_5 |

P28 |

P28_USB3_OTG0_DM |

- |

- |

USB3_OTG0 data- |

USB3_OTG0_DM |

RD_7 |

- |

GND |

- |

- |

Ground |

- |

RD_9 |

M24 |

M24_USB3_OTG0_VBUSDET |

- |

- |

USB3_OTG0 VBUS detection signal |

USB3_OTG0_VBUSDET |

RD_11 |

L23 |

L23_USB3_OTG0_ID |

- |

- |

USB3_OTG0 ID signal |

USB3_OTG0_ID |

RD_13 |

- |

GND |

- |

- |

Ground |

- |

RD_15 |

AE24 |

AE24_GPIO0_A6_d |

GPIO0_A6 |

3.3V |

General IO |

PCIE30X2_CLKREQn_M0 |

RD_17 |

AH26 |

AH26_GPIO0_B7_HEART |

GPIO0_B7 |

3.3V |

General IO (SoM heartbeat lamp occupied) |

GPIO0_B7_HEART |

RD_19 |

AF25 |

AF25_GPIO0_A5_d |

GPIO0_A5 |

3.3V |

General IO |

PI6C_OE |

RD_21 |

AF23 |

AF23_GPIO0_C1_d |

GPIO0_C1 |

3.3V |

General IO |

PCIE30_PRSNT |

RD_23 |

AH25 |

AH25_GPIO0_C7_d |

GPIO0_C7 |

3.3V |

General IO |

EDP_LED_EN3.3 |

RD_25 |

AG23 |

AG23_PWM3 |

GPIO0_C2 |

3.3V |

PWM3 |

EDP_PWM3.3 |

RD_27 |

AE23 |

AE23_PWM4 |

GPIO0_C3 |

3.3V |

PWM4 |

PCIE20_PRSNT |

RD_29 |

AD21 |

AD21_PWM5 |

GPIO0_C4 |

3.3V |

PWM5 |

MIPI_PWM |

RD_31 |

AD23 |

AD23_GPIO0_B0_u |

GPIO0_B0 |

3.3V |

General IO |

MIPI_EN |

RD_33 |

AD22 |

AD22_GPIO0_C0_d |

GPIO0_C0 |

3.3V |

General IO |

MIPI_ACC_INT |

RD_35 |

AC22 |

AC22_GPIO0_B5_u |

GPIO0_B5 |

3.3V |

General IO |

PCIE20_WAKEN_M0 |

RD_37 |

AD20 |

AD20_GPIO0_C6_d |

GPIO0_C6 |

3.3V |

General IO |

PCIE30X2_PERSTn_M0 |

RD_39 |

AC21 |

AC21_GPIO0_C5_d |

GPIO0_C5 |

3.3V |

General IO |

PCIE30X2_WAKEn_M0 |

RD_41 |

AA20 |

AA20_GPIO0_B6_u |

GPIO0_B6 |

3.3V |

General IO |

PCIE20_PERSTN_M0 |

RD_43 |

AG27 |

AG27_REFCLK_OUT |

GPIO0_A0 |

3.3V |

Reference clock output |

MIPI_TP_INT |

RD_45 |

- |

GND |

- |

- |

Ground |

- |

RD_47 |

AH27 |

AH27_RESETn |

- |

- |

Reset signal |

RESETn |

RD_49 |

EMMC |

EMMC_BOOT |

- |

- |

Maskrom flashing control |

BOOT |

RD_51 |

AB18 |

AB18_HDMI_TX_HPDIN |

- |

- |

HDMI hot plug detection |

HDMI_TX_HPDIN |

RD_53 |

AH6 |

AH6_HDMITX_CEC_M0 |

- |

- |

HDMI-CEC signal |

HDMITX_CEC_M0 |

RD_55 |

- |

GND |

- |

- |

- |

Ground |

RD_57 |

AG19 |

AG19_HDMI_TXCLKN_PORT |

- |

- |

HDMI Differential Clock Signals- |

HDMI_TXCLKN_PORT |

RD_59 |

AH19 |

AH19_HDMI_TXCLKP_PORT |

- |

- |

HDMI Differential Clock Signals+ |

HDMI_TXCLKP_PORT |

RD_61 |

- |

GND |

- |

- |

- |

Ground |

RD_63 |

AH20 |

AH20_HDMI_TX0N_PORT |

- |

- |

HDMI differential data 0- |

HDMI_TX0N_PORT |

RD_65 |

AG20 |

AG20_HDMI_TX0P_PORT |

- |

- |

HDMI differential data 0+ |

HDMI_TX0P_PORT |

RD_67 |

- |

GND |

- |

- |

- |

Ground |

RD_69 |

AH21 |

AH21_HDMI_TX1N_PORT |

- |

- |

HDMI differential data 1- |

HDMI_TX1N_PORT |

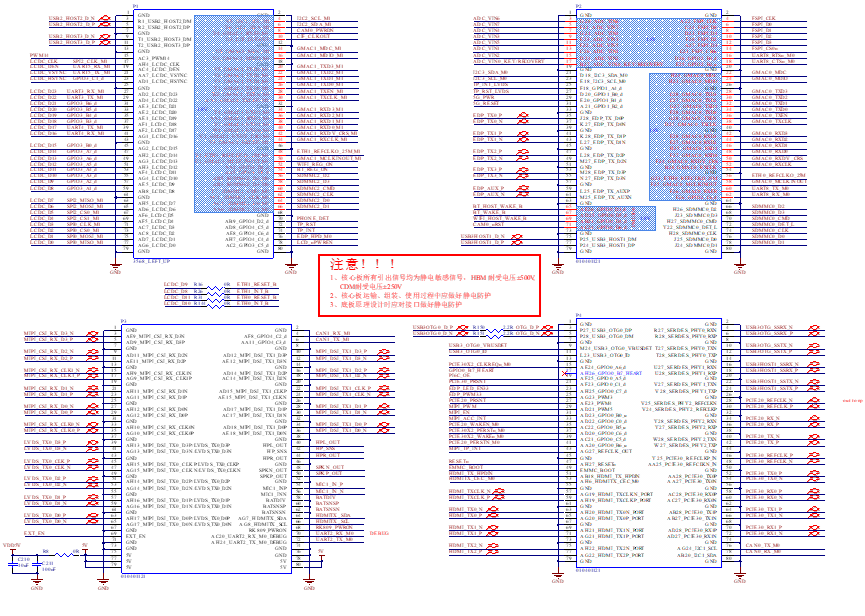

RD_71 |

AG21 |

AG21_HDMI_TX1P_PORT |

- |

- |

HDMI differential data 1+ |

HDMI_TX1P_PORT |

RD_73 |

- |

GND |

- |

- |

- |

Ground |

RD_75 |

AH22 |

AH22_HDMI_TX2N_PORT |

- |

- |

HDMI differential data 2- |

HDMI_TX2N_PORT |

RD_77 |

AG22 |

AG22_HDMI_TX2P_PORT |

- |

- |

HDMI differential data 2+ |

HDMI_TX2P_PORT |

RD_79 |

- |

GND |

- |

- |

Ground |

– |

Table 8 RIGHT _ DOWN (P4) Connector Interface (Even) Pin Definition

Num |

Ball |

Signal Name |

GPIO |

Vol |

Pin Description |

Default Function |

|---|---|---|---|---|---|---|

RD_2 |

- |

GND |

- |

- |

Ground |

- |

RD_4 |

R27 |

R27_SERDES_PHY0_RXN |

- |

- |

SERDES PHY0 receive- |

USB3OTG_SSRX_N |

RD_6 |

R28 |

R28_SERDES_PHY0_RXP |

- |

- |

SERDES PHY0 receive+ |

USB3OTG_SSRX_P |

RD_8 |

- |

GND |

- |

- |

Ground |

- |

RD_10 |

T27 |

T27_SERDES_PHY0_TXN |

- |

- |

SERDES PHY0 send- |

USB3OTG_SSTX_N |

RD_12 |

T28 |

T28_SERDES_PHY0_TXP |

- |

- |

SERDES PHY0 send+ |

USB3OTG_SSTX_P |

RD_14 |

- |

GND |

- |

- |

Ground |

- |

RD_16 |

U27 |

U27_SERDES_PHY1_RXN |

- |

- |

SERDES PHY1 receive- |

USB3HOST1_SSRX_N |

RD_18 |

U28 |

U28_SERDES_PHY1_RXP |

- |

- |

SERDES PHY1 receive+ |

USB3HOST1_SSRX_P |

RD_20 |

- |

GND |

- |

- |

Ground |

- |

RD_22 |

V27 |

V27_SERDES_PHY1_TXN |

- |

- |

SERDES PHY1 send- |

USB3HOST1_SSTX_N |

RD_24 |

V28 |

V28_SERDES_PHY1_TXP |

- |

- |

SERDES PHY1 send+ |

USB3HOST1_SSTX_P |

RD_26 |

- |

GND |

- |

- |

Ground |

- |

RD_28 |

V25 |

V25_SERDES_PHY2_REFCLKN |

- |

- |

SERDES PHY2 differential clock signal- |

PCIE20_REFCLK_N |

RD_30 |

V24 |

V24_SERDES_PHY2_REFCLKP |

- |

- |

SERDES PHY2 differential clock signal+ |

PCIE20_REFCLK_P |

RD_32 |

- |

GND |

- |

- |

Ground |

- |

RD_34 |

Y28 |

Y28_SERDES_PHY2_RXN |

- |

- |

SERDES PHY2 receive- |

PCIE20_RX_N |

RD_36 |

Y27 |

Y27_SERDES_PHY2_RXP |

- |

- |

SERDES PHY2 receive+ |

PCIE20_RX_P |

RD_38 |

- |

GND |

- |

- |

Ground |

- |

RD_40 |

W28 |

W28_SERDES_PHY2_TXN |

- |

- |

SERDES PHY2 send- |

PCIE20_TX_N |

RD_42 |

W27 |

W27_SERDES_PHY2_TXP |

- |

- |

SERDES PHY2 send+ |

PCIE20_TX_P |

RD_44 |

- |

GND |

- |

- |

Ground |

- |

RD_46 |

Y25 |

Y25_PCIE30_REFCLKP_IN |

- |

- |

PCIE3.0 differential clock signal+ |

PCIE30_REFCLK_P |

RD_48 |

AA25 |

AA25_PCIE30_REFCLKN_IN |

- |

- |

PCIE3.0 differential clock signal- |

PCIE30_REFCLK_N |

RD_50 |

- |

GND |

- |

- |

Ground |

- |

RD_52 |

AA28 |

AA28_PCIE30_TX0P |

- |

- |

PCIE3.0 sends data 0+ |

PCIE30_TX0_P |

RD_54 |

AA27 |

AA27_PCIE30_TX0N |

- |

- |

PCIE3.0 sends data 0- |

PCIE30_TX0N |

RD_56 |

- |

GND |

- |

- |

Ground |

- |

RD_58 |

AC28 |

AC28_PCIE30_RX0P |

- |

- |

PCIE3.0 Receiving data 0+ |

PCIE30_RX0P |

RD_60 |

AC27 |

AC27_PCIE30_RX0N |

- |

- |

PCIE3.0 Receiving data 0- |

PCIE30_RX0N |

RD_62 |

- |

GND |

- |

- |

Ground |

- |

RD_64 |

AB28 |

AB28_PCIE30_TX1P |

- |

- |

PCIE3.0 sends data 1+ |

PCIE30_TX1P |

RD_66 |

AB27 |

AB27_PCIE30_TX1N |

- |

- |

PCIE3.0 sends data 1- |

PCIE30_TX1N |

RD_68 |

- |

GND |

- |

- |

Ground |

- |

RD_70 |

AD28 |

AD28_PCIE30_RX1P |

- |

- |

PCIE3.0 Receiving data1+ |

PCIE30_RX1P |

RD_72 |

AD27 |

AD27_PCIE30_RX1N |

- |

- |

PCIE3.0 Receiving data1- |

PCIE30_RX1N |

RD_74 |

- |

GND |

- |

- |

Ground |

- |

RD_76 |

AG24 |

AG24_I2C1_SCL |

GPIO0_B3 |

3.3V |

I2C1 clock |

CAN0_TX_M0 |

RD_78 |

AB20 |

AB20_I2C1_SDA |

GPIO0_B4 |

3.3V |

I2C1 data |

CAN0_RX_M0 |

RD_80 |

- |

GND |

- |

- |

Ground |

- |

2.6 SoM Hardware Design Description

2.6.1 SoM Circuit Design Guidelines

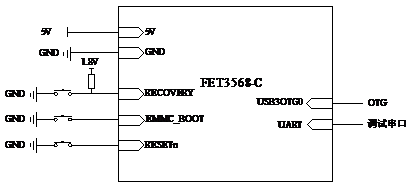

The FET3568-C/C2 SoM integrates the power supply, reset monitoring circuit, and memory circuitry into a compact module. The required external circuitry is minimal. To build a basic system, only a 5V power supply, a reset button, and the boot configuration are needed for operation, as shown in the figure below:

The schematic of the minimal system can be found in Appendix 4. In general usage, it is recommended to connect additional external devices beyond the minimal system, such as:

Debug serial port: for monitoring printed output

Reserved OTG interface: for system programming

After implementing these basic functions, additional user-required features can be added based on the default SoM interface definitions provided by Forlinx.

2.6.2 SoM Vibration-Resistant Design Guidelines

This product uses M2 anti-fall screws to secure the four pre-drilled mounting holes at the corners of the SoM. The tightening torque should be controlled at 0.15 N·m. The assembly illustration is shown below.

The design has been validated through vibration testing in accordance with GB/T 2423.10-2008 / IEC 60068-2-6:1995, achieving the following specifications:

Frequency range: 10 Hz – 150 Hz

Test axes: X, Y, Z

Displacement amplitude: 0.35 mm

Acceleration amplitude: 5 g

The performance data listed in this manual are obtained under standard laboratory conditions and are applicable to general industrial equipment. Actual performance may vary depending on installation methods, combined stresses, and other operational factors.

3. OK3568-C&C2C Development Platform Description

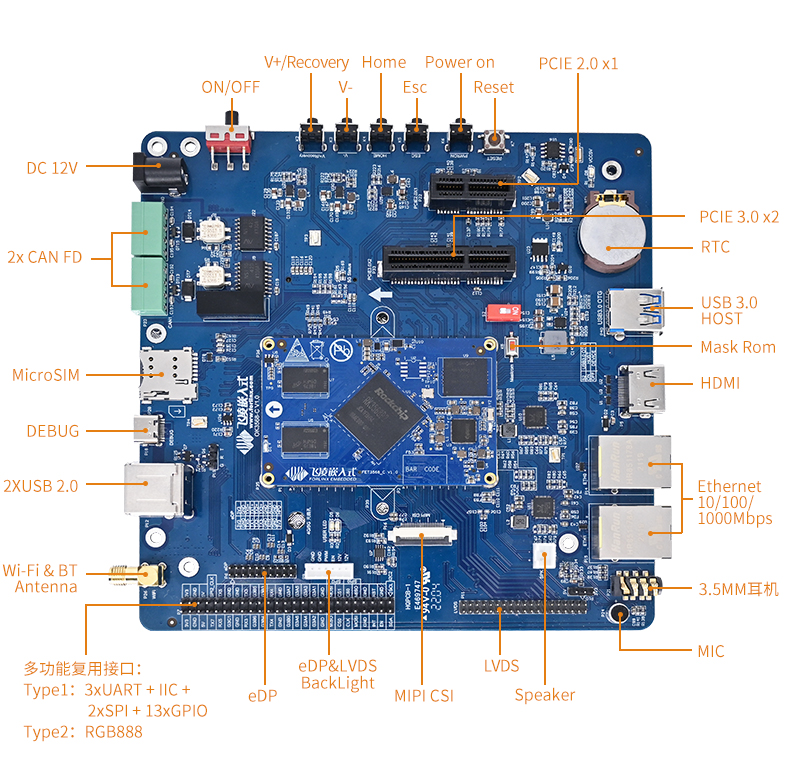

3.1 OK3568-C/C2C Development Board Interface Diagram

FET3568-C and FET3568-C2 SoM have the same pin definition and can share a common carrier board. When FET3568-C is combined with the OK3568-C carrier board, the development board name is OK3568-C development board; when FET3568-C2 is combined with the OK3568-C carrier board, the development board name is OK3568-C2C development board.

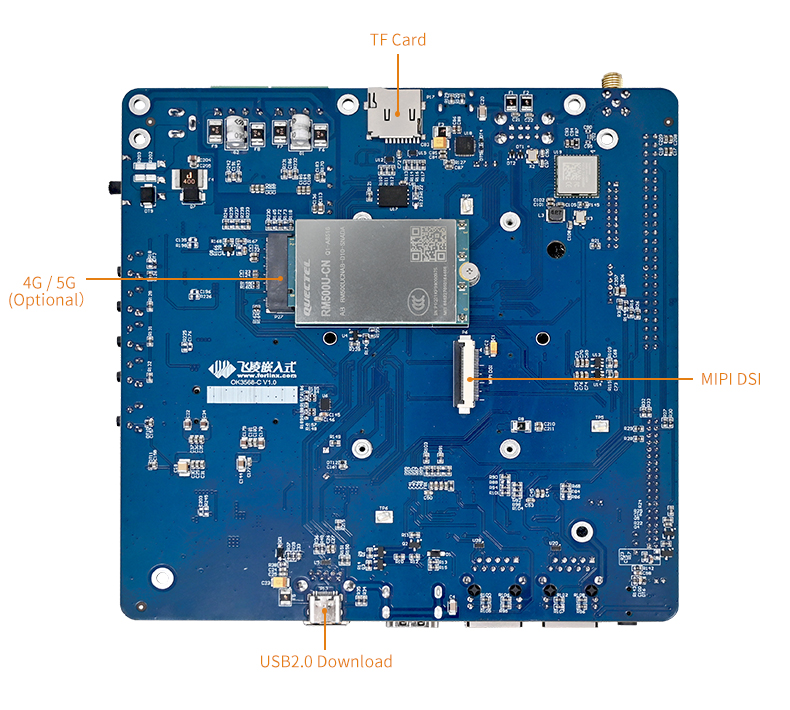

The connection between SoM and the carrier board is board-to-board, and the main interfaces are shown as follows:

Front

Back

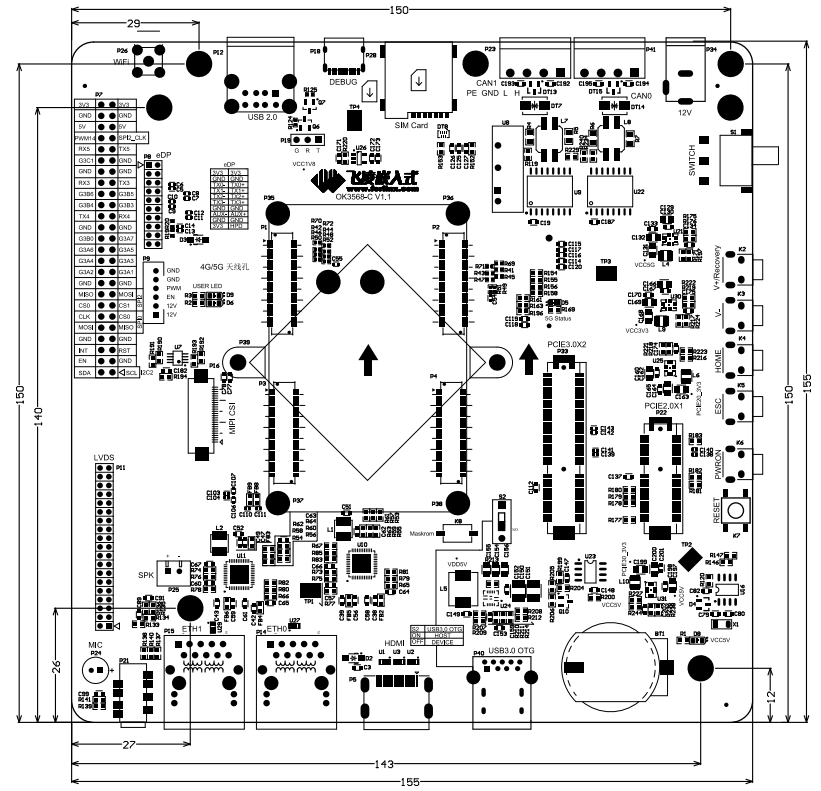

3.2 OK3568-C/C2C Development Board Dimension Diagram

OK3568-C/ C2C development board and antenna board are as follows:

Carrier board PCB size: 155mm × 155mm. For more detailed dimensions, please refer to the user information DXF file;

Fixing hole diameter: 3.2mm;

Plate making process: thickness 1.6mm, 4-layer PCB.

Power supply voltage: DC 12V.

The antenna board is used for the installation and fixation of 4G and 5G antennas. Its external dimensions are 20mm×140mm. For more detailed dimensions, please refer to the figure below:

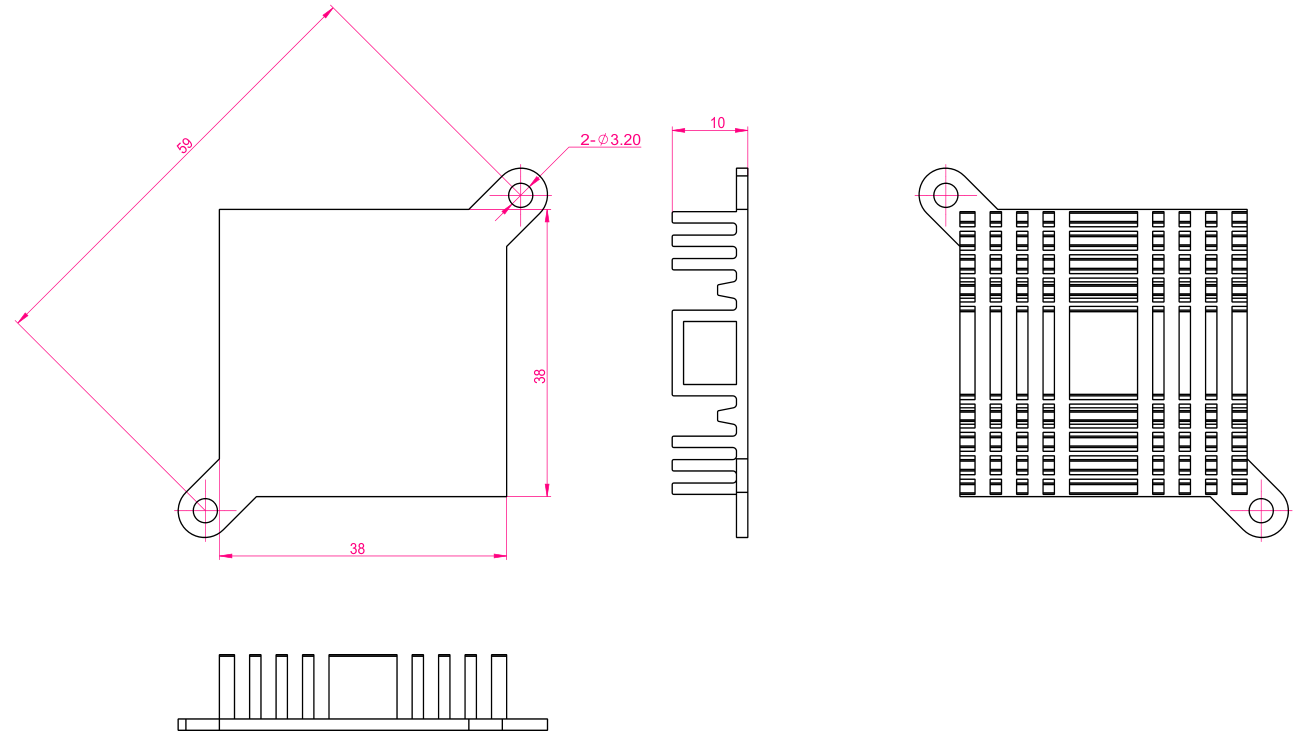

Two mounting holes with a diameter of 3.2mm are reserved on the carrier board. You can select and install the heat sink according to the site environment. Please add a layer of insulated heat-conducting silicone pad on the contact surface between the heat sink and the core board. 38Mm×38mm×10mm. For more detailed dimensions, please refer to the following figure.

3.3 Carrier Board Naming Rules

A B-C+D E F :G-H

Field |

Field Description |

Value |

Description |

|---|---|---|---|

A |

Product Line Identification |

OK |

Forlinx Embedded carrier board/development board |

TCU |

Forlinx embedded charging control unit |

||

B |

CPU Name |

3568 |

RK3568 |

- |

Segment Identification |

- |

Parameter segment sign |

C |

Connection |

C |

Board to Board Connector |

+ |

Segment Identification |

+ |

The configuration parameter section follows this identifier. |

D |

Type |

M |

Carrier board (Note: carrier board identification M, not filled by default) |

E |

Operating Temperature |

C |

0 to 80℃ Commercial-grade |

F |

PCB Version |

10 |

V1.0 |

xx |

Vx.x |

||

: |

Separator |

: |

It’s followed by the manufacture’s internal identification. |

G |

Connector origin |

1 |

Imported connector |

3.4 Carrier Board Resources

Function |

Quantity |

Parameter |

|---|---|---|

USB2.0 |

1 |

The Type-C interface shares USB 2.0 pins with the USB 3.0 HOST, and can operate in device mode for firmware flashing and ADB debugging. |

USB 2.0 |

2 |

USB 2.0 Host, Type-A |

USB3.0 |

1 |

USB 3.0 Host, Type-A The USB 2.0 signal is multiplexed with the USB 2.0 download pin, and the function is switched through the S2 DIP switch. |

Camera |

1 |

MIPI-CSI, adapted to OV13850 |

MIPI_DSI |

1 |

Single-channel output, the default is adapted to the Forlinx 7-inch MIPI screen of Forlinx, with a resolution of 1024 X 600 |

LVDS |

1 |

Single-channel output, the default is adapted to the Forlinx 10.1-inch LVDS screen, with a resolution up to 1280x800 |

HDMI |

1 |

Resolution is up to 1080p@120Hz or 4096x2304@60Hz |

LCD |

1 |

Supports RGB888, resolution up to 1920x1080; multiplexed with SPI0, SPI2, UART3, UART4, UART5, UART7; the development board defaults to the above functions, can be set to RGB function by modifying the software |

eDP |

1 |

Supports eDP 1.3, resolution up to 2560x1600 @ 60Hz |

Ethernet |

2 |

2 x 10/100/1000Mbps adaptive network port, RJ45 lead-out |

4G/5G |

1 |

M.2 Key-B, equipped with USB 3.0/2.0, it can be used to expand 4G/5G modules and is compatible with EM05-CE (4G, EC20 compatible driver) and RM500U-CN (5G) drivers |

PCIE 2.1 |

1 |

Standard PCIe x1 socket; this function pin can be multiplexed as SATA function by modifying the software. |

PCIE 3.0 |

1 |

Standard PCIe x4 socket; it can be configured as 2 PCIe x1 channels through software. |

TF Card |

1 |

Supports extended storage and system flashing |

WiFi |

1 |

On-board AW-CM358SM, 2.4G/5G dual band Wi Fi, BT5.0, no audio function. Wi-Fi function occupies 1 x SDIO interface; BT function occupies 1 x UART interface. |

Bluetooth |

1 |

|

Audio |

1 |

1 x stereo headphone output, 1 x 1.3W Class-D amplifier output, and 1 x MIC input. |

I2C |

1 |

3.3V TTL Led out via a 2.54mm pitch pin; |

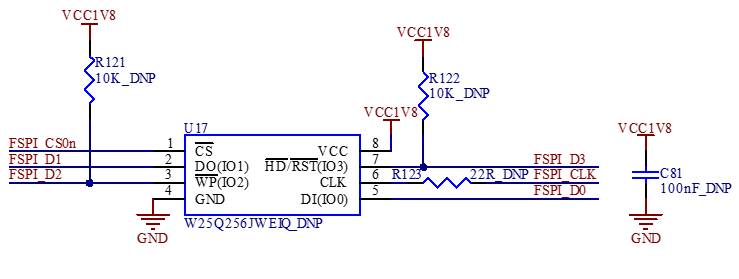

FSPI |

1 |

Default: not soldered (functionality is temporarily unsupported). |

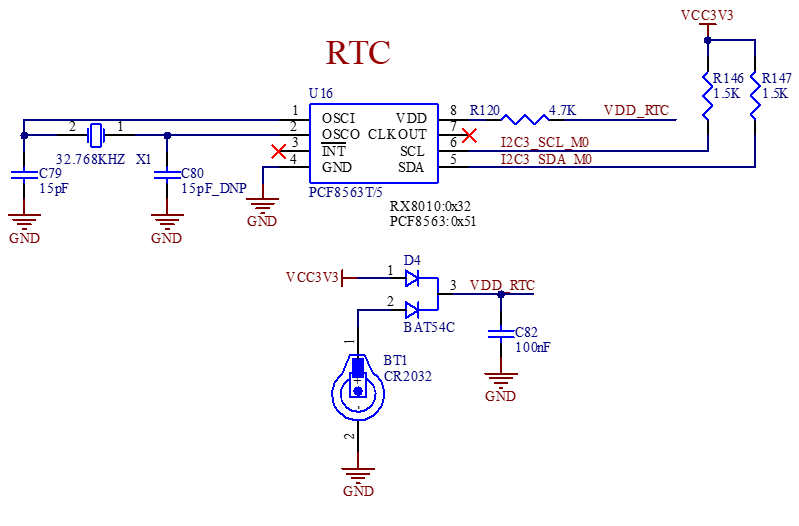

RTC |

1 |

On-board CR2032 battery, keep going when power is off |

UART |

3 |

3.3V TTL Led out via a 2.54mm pitch pin; |

SPI |

2 |

3.3V TTL Led out via a 2.54mm pitch pin; |

CAN |

2 |

CAN, up to 1Mbps; with quarantine and ESD protection |

KEY |

8 |

Reset; Power on/off; OTG programming; Maskrom; VOL +, VOL-; HOME,; SC |

LED |

2 |

User-defined LED light |

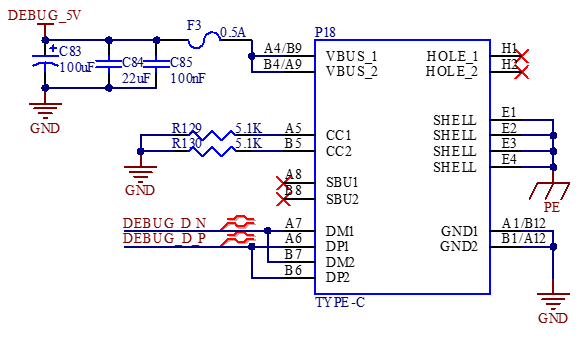

DEBUG |

1 |

On-board USB to serial port chip, led out via Type-C, which is convenient for laptop debugging. Default baud rate (115200) |

Note: The parameters in the table are the theoretical values of hardware design or CPU;

3.5 OK3568-C Carrier Board Description

Note:

The component UID with “_DNP” mark in the diagram below represents it is not soldered by default;

The schematic diagram in this chapter is only for the easy reading and may be subject to changes. Please make sure to follow the source file schematic diagram when designing.

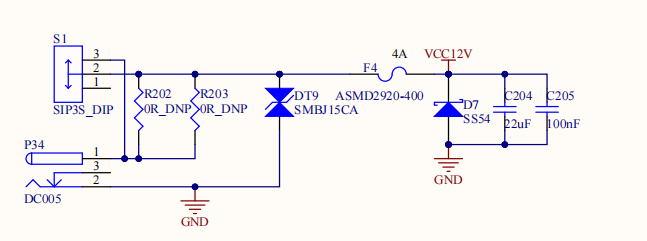

3.5.1 Carrier Board Power

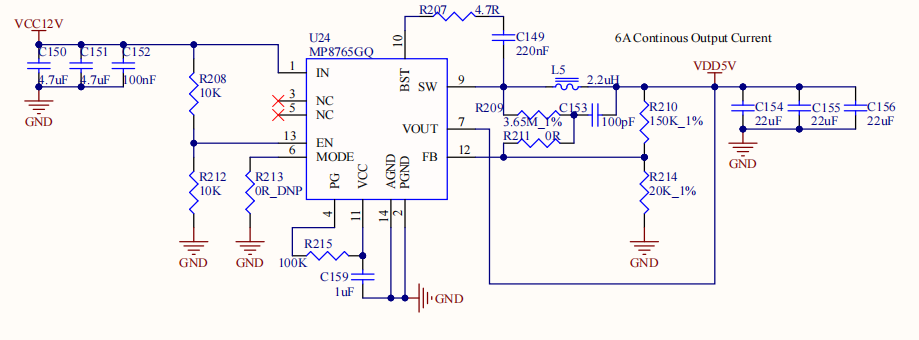

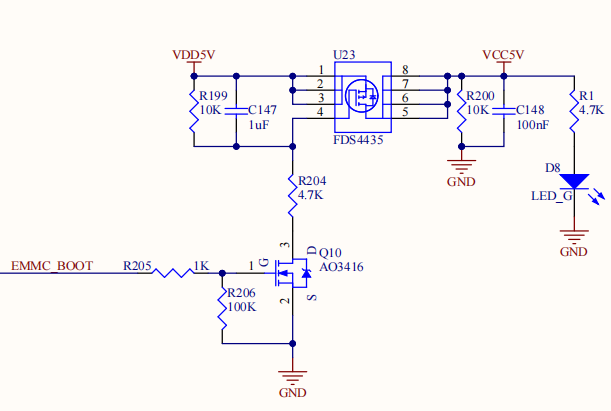

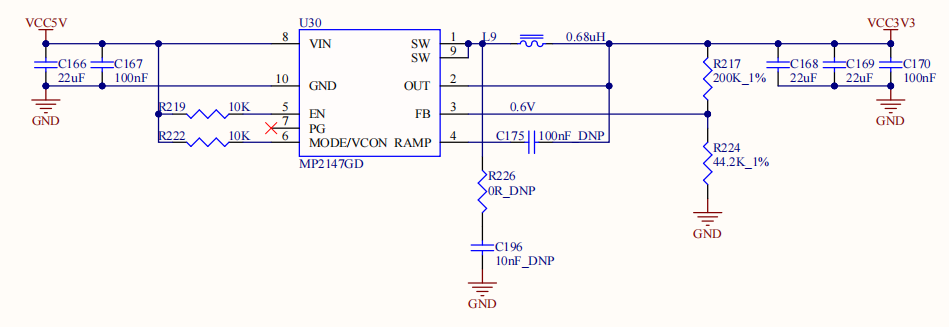

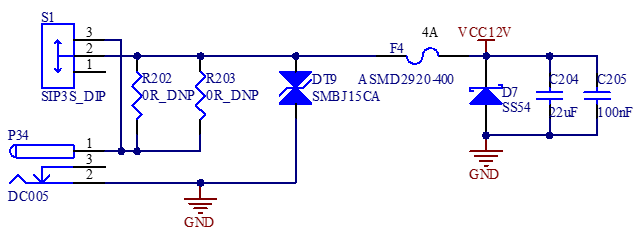

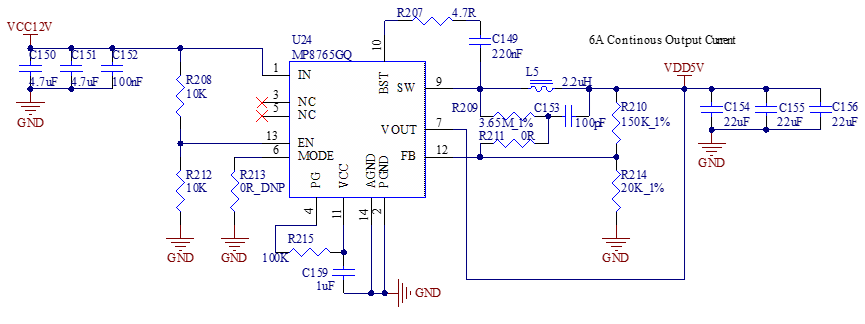

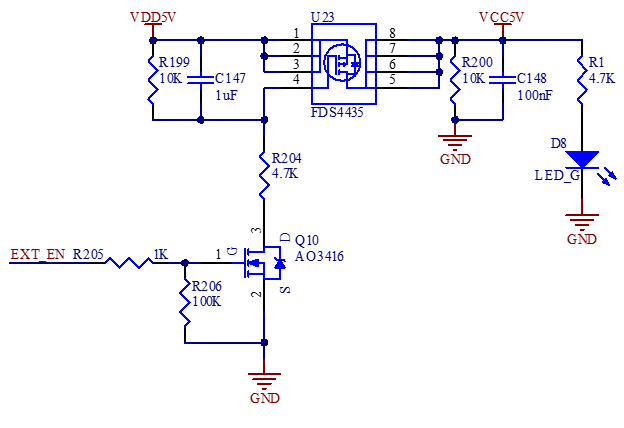

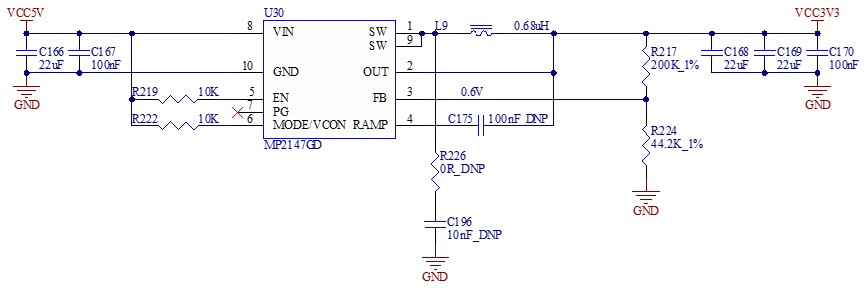

As shown in the figure, a 12V adapter provides power to the development board through the P34 power connector. VCC12V is stepped down to VDD5V via U24, supplying power to the SoM. After the SoM is powered on, it outputs the EMMC_BOOT signal, which controls the power-on of the carrier board VCC5V.

The EMMC_BOOT signal ensures that the SoM powers on before the carrier board.

If the S1 DIP switch is removed due to structural requirements, you can solder resistors R202 and R203 to enable automatic hardware power-on.

Note: When designing hardware, please refer to the development board power-on sequence. Specifically, the EMMC_BOOT output from the SoM should serve as the enable signal for the carrier board VCC5V power supply, ensuring that the SoM powers on first, followed by the carrier board.

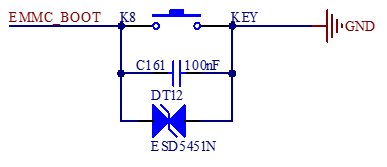

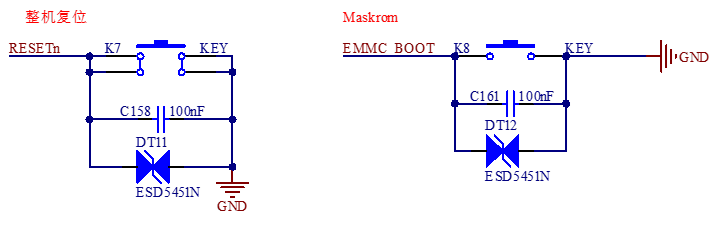

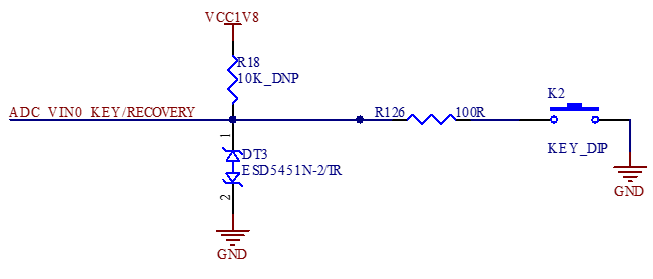

3.5.2 Keys

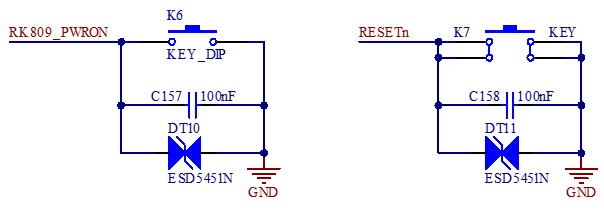

As shown in the figure, RESETn is the system reset button. Pressing it will cause the development board to power down and reset. RK809 _ PWRON is the power on/off key. Short press it to enter the sleep state, and then short press it to wake up the system. Long press, the system shuts down.

Note: Please float the RESETn and RK809 _ PWRON pins when they are not used, and do not pull them up or down.

3.5.3 Boot Configuration

The system boot order priority of the RK3568 chip from high to low is:

Serial Nor Flash(FSPI)

Serial Nand Flash(FSPI)

Nand Flash

eMMC

SDMMC0 Card

There are three methods for flashing the development board:

1. When no image is flashed onto the FET3568-C SoM or its loader is corrupted, press and hold the BOOT button K8, then press the reset button K7 to enter maskrom mode for image flashing via the USB Type C interface P13;

2. When the FET3568-C SoM already has a built-in loader, press and hold the Recovery button K2, then press the reset button K7 to enter USB flashing mode;

3. Before powering on, insert the prepared TF card for flashing into the OK3568-C carrier board, then power on to enter TF card flashing mode;

Currently, the development board does not support FSPI Flash booting. Please do not connect storage devices to the FSPI controller to avoid system boot abnormalities. If users need to use the FSPI booting method, please contact a software engineer for configuration modifications.

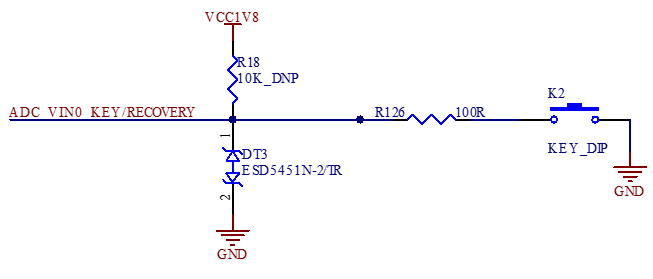

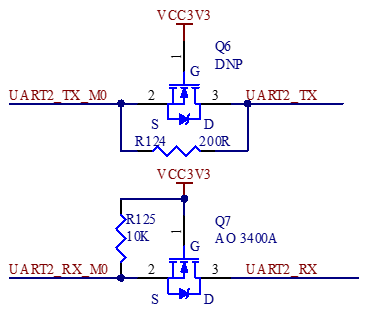

3.5.4 Debugging Serial Port

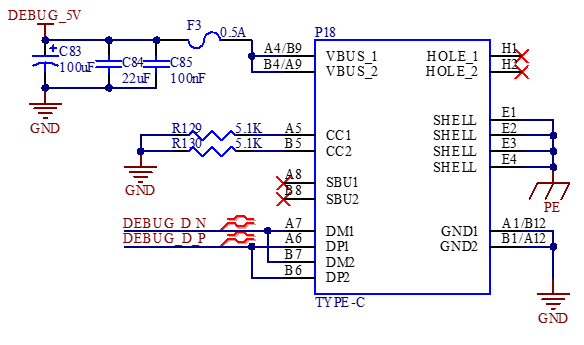

UART2 serves as the debug serial port for the SoM, with its TTL level signals routed through P19. For the convenience, the development board employs a USB-to-serial chip CP2102 to convert the debug serial port to a USB Type C interface.

Before using the debug serial port, install the CP2102 driver on your computer. The driver package DriverAssitant_v5.11.zip can be found and installed in the user data\Linux\tools\ directory. Next, connect the development board’s P18 interface to the computer’s USB port using a USB-to-TypeC cable. A COM port will appear in the computer’s Device Manager, which is the debug serial port.

Open a debug terminal tool on the computer, such as Putty. Set the baud rate to 115200, the data bits to 8, no parity bit, and the stop bits to 1. Select the correct COM port, power on the development board, and you can see the debug serial port information.

You can also prepare your own UART-to-serial conversion cable for the computer side and connect it to the P19 interface.

Note:

For the convenience of later debugging, please lead out the debugging serial port when designing the carrier board;

The debug serial ports on the carrier board are designed to prevent electric leakage. It is recommended that users refer to this design.

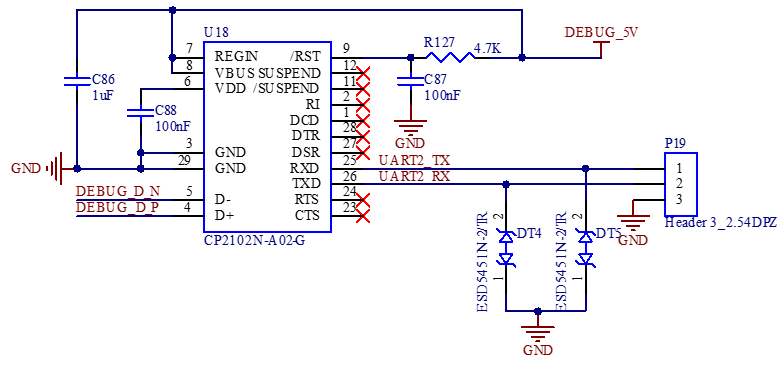

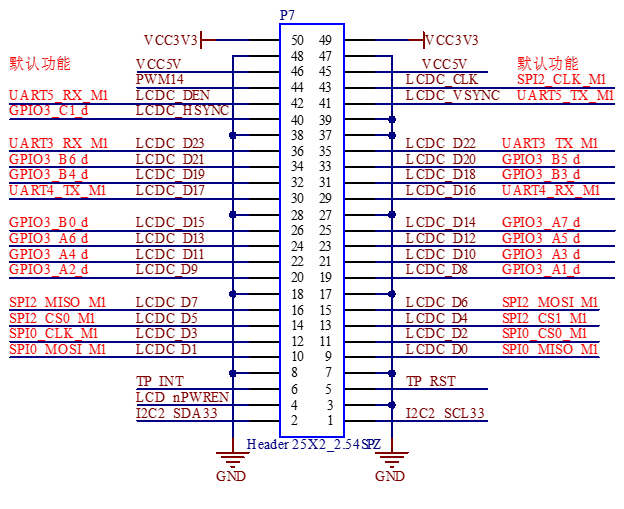

3.5.5 General Serial Ports

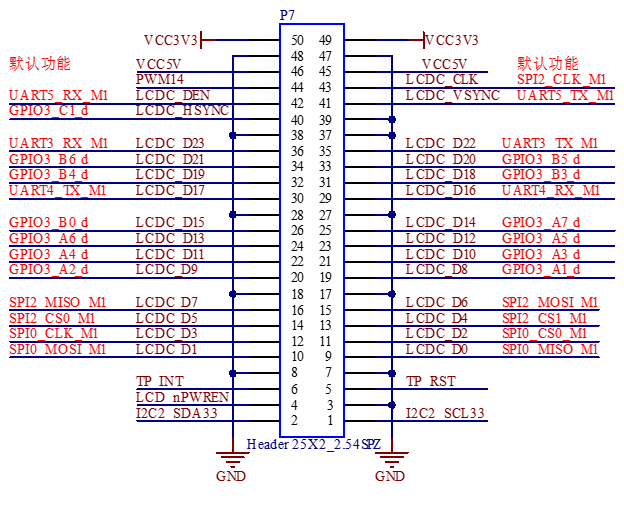

As shown in the figure above, the UART3/4/5 are functionally multiplexed with the LCD pins, which are led out through the carrier board P7 2.54 mm double row of pins.

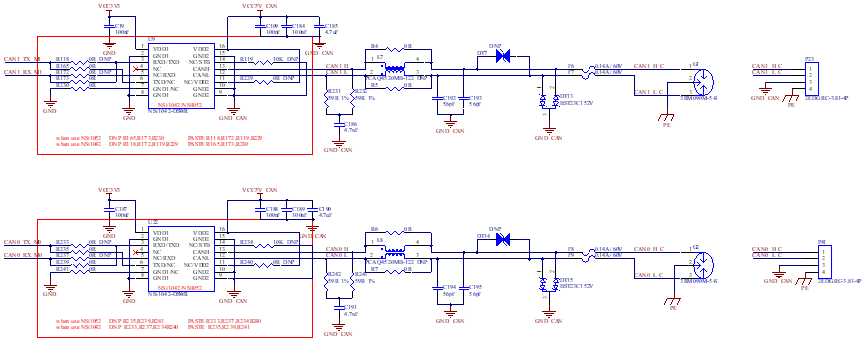

3.5.6 CAN

The development board provides 2 x CAN with a maximum speed of 1 Mbps, 1500 VDC electrical isolation, and Level 4 electrostatic protection.

This circuit is compatible with both Nsi1042 and Nsi1052 CAN transceivers. When using different chips, the peripheral circuit needs to be modified according to the specific chip model.

P23 and P41 wiring terminals are led out, and it is recommended to ground the equipment when CAN communication is used.

3.5.7 FSPI

The development board provides 1 x FSPI interface, which can be externally connected with NOR FLASH chip.

Currently, the development board does not support FSPI Flash booting. Please do not connect storage devices to the FSPI controller to avoid system boot abnormalities. The circuit components related to the development board are empty soldered by default.

By default, when the SoM starts from the eMMC, the FSPI _ D2 signal line is not connected to the CPU by default. Therefore, when using the FSPI, only the single-wire or two-wire mode can be used.

3.5.8 SPI

As shown in the figure above, SPI0 and SPI2 are multiplexed with the LCD pin function and are led out through a P7 2.54 mm pitch double row of pins.

3.5.9 TF Card

As shown in the figure above, the TF Card of the development board is the SD0 channel of the CPU, which supports the TF card of UHS-I up to 104MB/s.

Note:

The pull-up resistor on the bus has been adapted on the SoM, so the pull-up can not be processed on the carrier board;

The TF card is a hot-swappable device, so ESD protection should be implemented;

SD signals must be length-matched;

This group of pins is multiplexed for JTAG and SDMMC0, and the switching is controlled by the SDMMC0_DET_L pin. Therefore, this pin needs to be configured before power - on. Please refer to the development board design for this part;

It is recommended to reserve an 18pF capacitor to ground for the SDMMC0_CLK pin. Otherwise, there may be a problem of probabilistic failure in writing to the TF card.

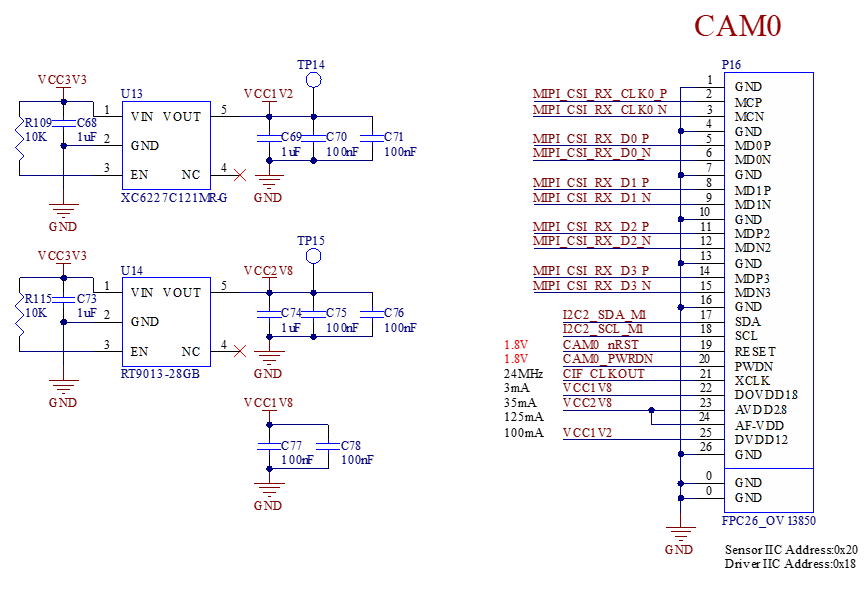

3.5.10 MIPI_CSI Interface

There are two sets of MIPI_CSI.

It supports the x 4 lane mode. The data of MIPI_CSI_RX_D[3:0] refers to MIPI_CSI_RX_CLK0.

It supports the x 2 lane + x2 lane mode. The data of MIPI_CSI_RX_D[1:0] refers to MIPI_CSI_RX_CLK0, and the data of MIPI_CSI_RX_D[3:2] refers to MIPI_CSI_RX_CLK1.

The MIPI _ CSI on the development board is x4 lane mode, which is led out through P16 and can be connected to the OV13850 camera module.

Note:

When designing the carrier board using other camera modules, please pay attention to the IO voltage and make level conversion;

For MIPI, the data and clock lines need to be of equal length, and the differential impedance should be controlled at 100Ω.

3.5.11 MIPI_DSI Interface

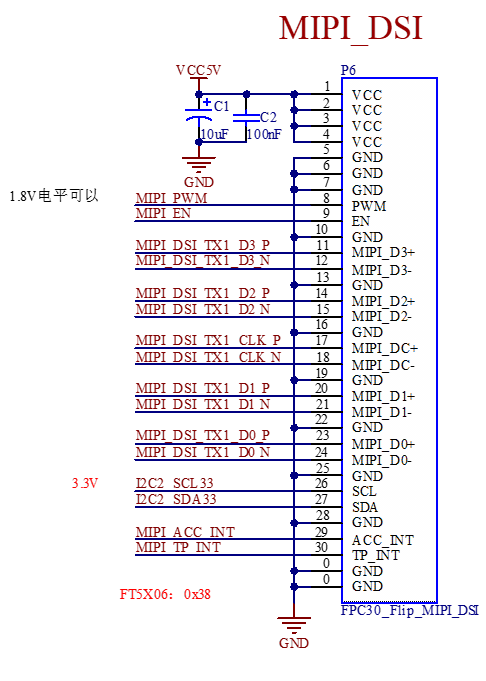

The SoM supports 2 x MIPI DSI. Among them, MIPI_DSI0 is used for LVDS output, and MIPI_DSI1 is output through the P6 terminal. Its maximum output resolution can reach 1920*1080@60Hz. It is suitable for the 7-inch MIPI screen of Forlinx by default, and supports screen brightness adjustment and capacitive touch.

Note:

For MIPI, the data and clock lines need to be of equal length, and the differential impedance should be controlled at 100Ω;

When designing the carrier board using other display screens, please pay attention to the IO voltage and make level conversion.

3.5.12 LVDS Interface

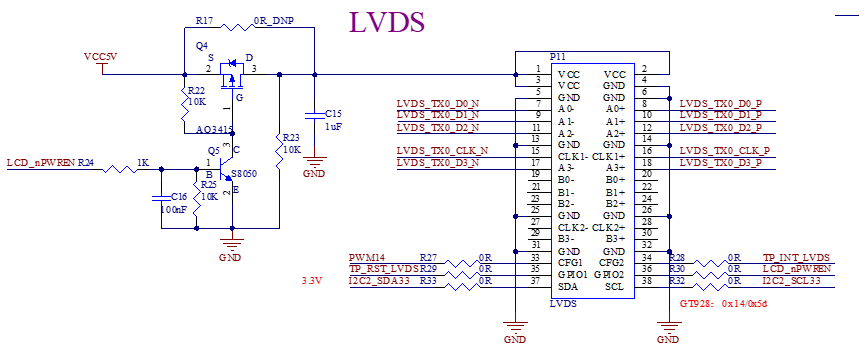

The MIPI_DSI0 led out from the SoM is a MIPI_DSI_TX0 and LVDS_TX Combo PHY. The development board uses it for LVDS output, which is led out through the P11 terminal. The pin - to - pin spacing is 2.0mm, and it can be adapted to the Forlinx 10.1 - inch LVDS screen, supporting screen brightness adjustment and capacitive touch.

Note: For LVDS, the data and clock lines need to be of equal length, and the differential impedance should be controlled at 100Ω.

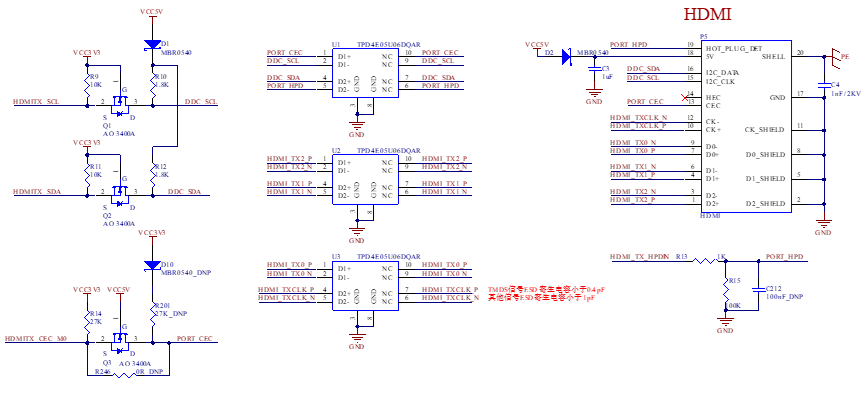

3.5.13 HDMI Interface

As shown in the figure above, 1 x HDMI is led out through P5 on the carrier board, supporting HDMI 2.0 with a display resolution up to 4096*2160@60. The HDMI circuit includes a level - conversion circuit. Please refer to the development - board design.

Note:

For HDMI, the data and clock lines need to be of equal length, and the differential impedance should be controlled at 100Ω;

HDMI is a hot - pluggable interface. Please design an ESD protection circuit, and the ESD device selection should support the HDMI2.0 rate;

Since 4K resolution display has relatively high requirements for signal quality, please use standard - compliant cables to connect the display.

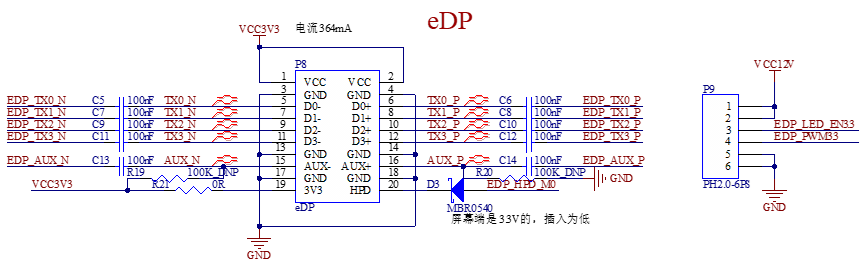

3.5.14 eDP Interface

There is an eDP interface on the development board, which is led out through the P8 terminal and is adapted to the Forlinx 10.1 - inch eDP screen. The backlight of the screen is provided by the P9 terminal.

3.5.15 Audio

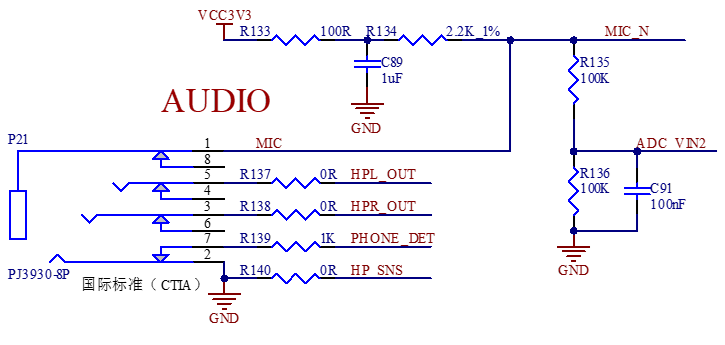

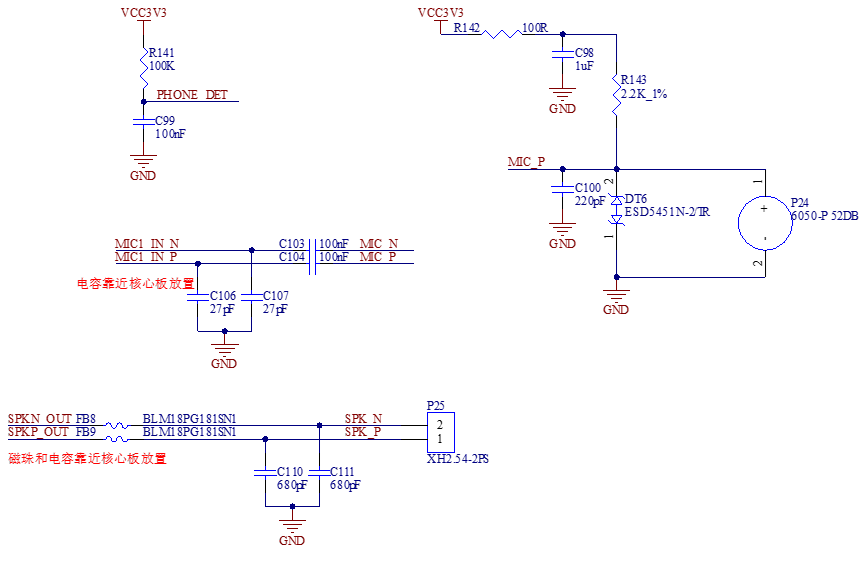

The PMIC on the SoM comes with a Codec, which can achieve headphone output, 1.3W mono speaker output, and one - way differential or two - way single - ended audio input functions.

The 3.5mm audio socket P32 is designed according to the CTIA standard. If an OMTP headphone is inserted, the playback and recording functions will fail. It supports headphone hot - plug detection. When a headphone is inserted, the headphone will be used for sound playback preferentially.

The maximum power of the Speaker is 1.3W (8Ω). If you need to connect an external larger power amplifier, you can only obtain the signal from the headphone socket, not from the speaker interface.

Note:

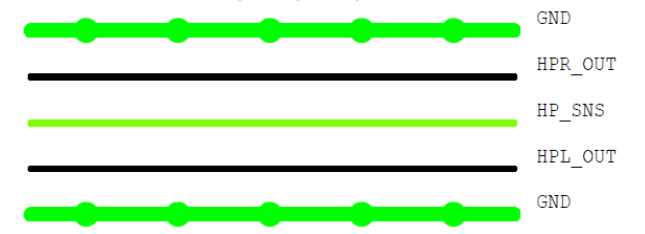

HP_SNS serves as an internal offset reference. This pin needs to be externally connected to GND for reference. When HPOUT is used as LINEOUT to connect an external power amplifier, HPSNS can be grounded near RK809 - 5. In the case of headphone output, HPSNS needs to be routed separately to the headphone socket and connected to GND to reduce the level difference with the headphone GND. When routing, it should be routed between HPR/HPL to avoid interference from other signals. The routing is shown in the figure below;

In addition, ESD devices need to be added to HPR_OUT and HPL_OUT to enhance the anti - static ability;

For the HP_DET of the headphone socket, add a 1K ohm resistor in series and a 100nF capacitor in parallel, and reserve ESD devices to enhance the anti - static surge ability;

The filtering circuit for speaker output should be close to the SoM

, while the ESD protection devices should be close to the connection socket. Pay attention to the specifications of the magnetic beads FB8 and FB9 in the figure. The current should be no less than 1.5A. The maximum power of the speaker is 1.3W (8Ω). If you need higher power or better output sound quality, it is recommended to obtain the signal from the headphone and expand an analog or digital power amplifier externally;The DC - blocking capacitors C103 and C104 of the MIC must not be deleted and should be placed close to the core board during layout.

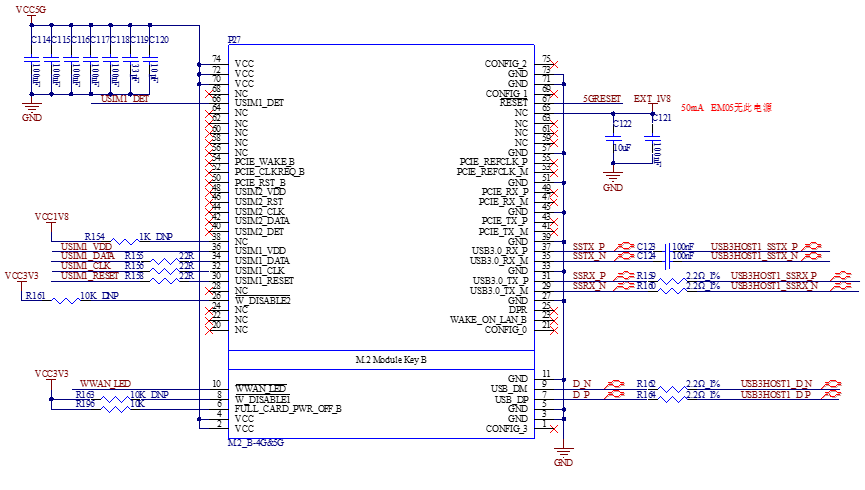

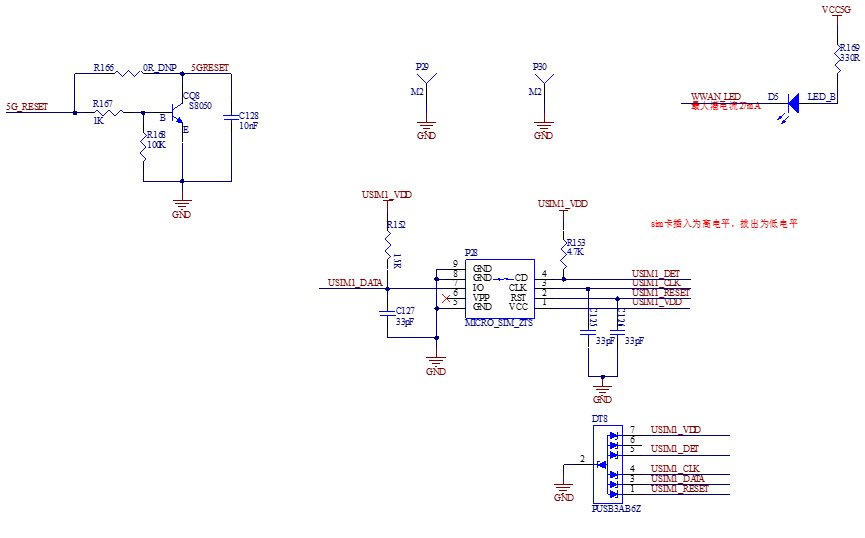

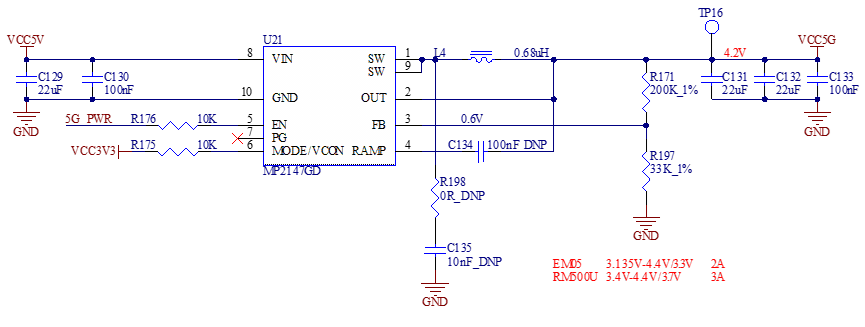

3.5.16 4G/5G

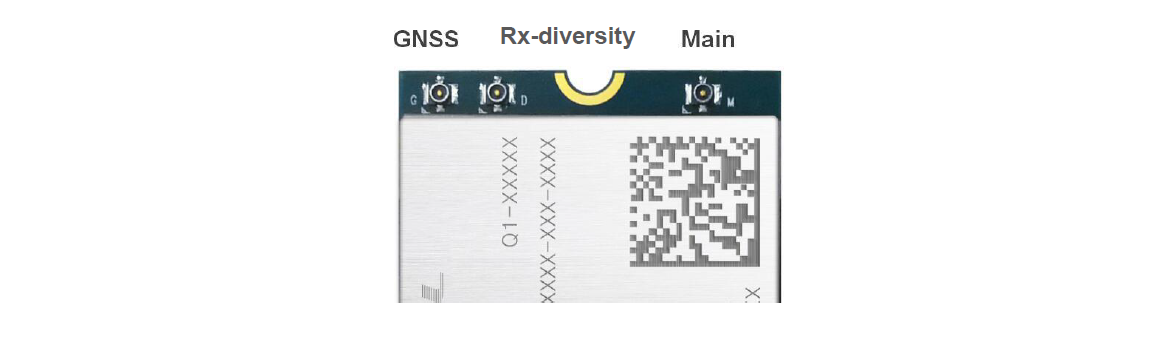

The development board can be externally connected with either a 4G module or a 5G module (choose one of the two). It supports the use of 4G/5G modules with an M.2 B-key socket. By default, the Quectel EM05 or RM500U modules are used. When you opt for Forlinx optional 4G module EM05, just connect the two provided 4G antennas to the Main and Rx-diversity ports.

The 4G and 5G modules share a DCDC power supply and a SIM card holder. Please install the module first and then power on the development board.

It uses a MicroSIM card. Please pay attention to the card insertion direction.

The RM500U is prone to unstable connections when operating at a low supply voltage, so the power supply voltage is set to 4.2V.

3.5.17 WiFi&Bluetooth

Development board onboard WIFI&BT module set, default welding AW-CM358SM, WLAN: IEEE 802.11 a/b/g/n/ac dual-band WIFI, up to 433.3 Mbps transceiver rate; Bluetooth: Bluetooth 5, up to 3Mbps speed. To enhance signal quality, use a 2.4 & 5GHz dual-band antenna.

AW - CM358SM needs to configure registers through the SDIO bus. Even if only the Bluetooth function is used, the SDIO bus needs to be connected to the SoM; otherwise, the Bluetooth initialization will fail.

Note:

The bluetooth does not support audio;

SD signals must be length-matched;

Antenna needs to be installed before using WIFI function!

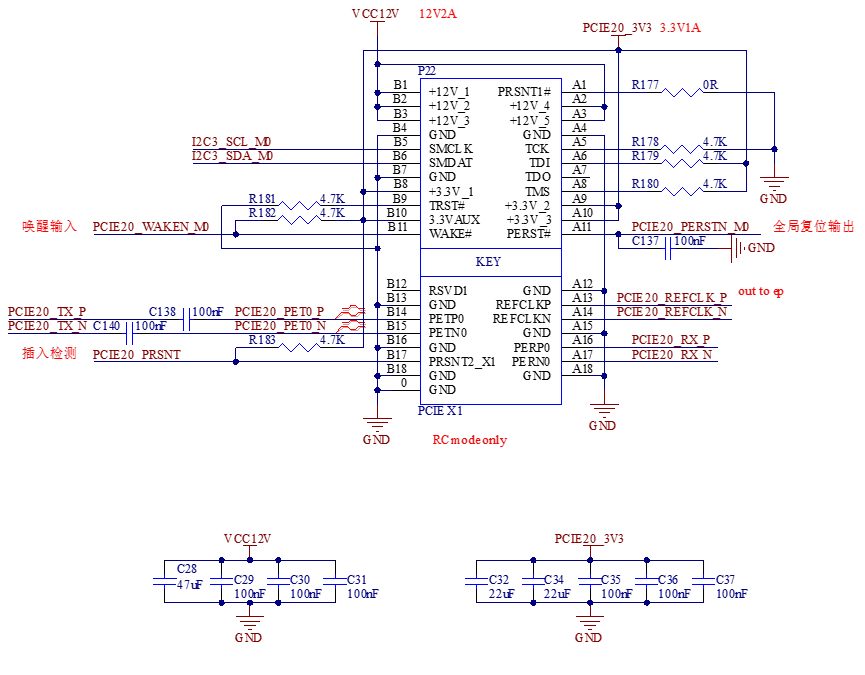

3.5.18 PCIE2.1 Interface

The development board supports one PCIE 2.1 X1 interface, which is led out through a PCIE X1 standard adapter card socket, making it convenient for you to connect various PCIE devices.

Since PCIE devices do not support hot - plug and have high requirements for power supply stability, a BUCK - type DCDC is used to provide 3.3V power.

Note:

The PCIE 2.1 only supports the RC mode;

The reference clock PCIE20 _ REFCLKP/N supports both output and input, and the default output is provided to the EP device.

PCIE20_CLKREQn and PCIE20_WAKEn must use function pins and cannot use GPIO instead. Special note: M0, M1 and M2 can be used independently, but the combination (M0+M1or M0+M1 or M1+M2) for multiplexing is not allowed.

PCIE20_PERSTn can choose the function pin or use GPIO instead, when choosing the function pin, it must be the same set of _Mx as PCIE20_CLKREQn and PCIE20_WAKEn;

PCIE20_PRSNT is the Add In Card insertion detection pin, which can use GPIO;

An 85 Ω differential impedance is required for PCIe TX/RX data and a 100 Ω differential impedance is required for the CLK reference clock.

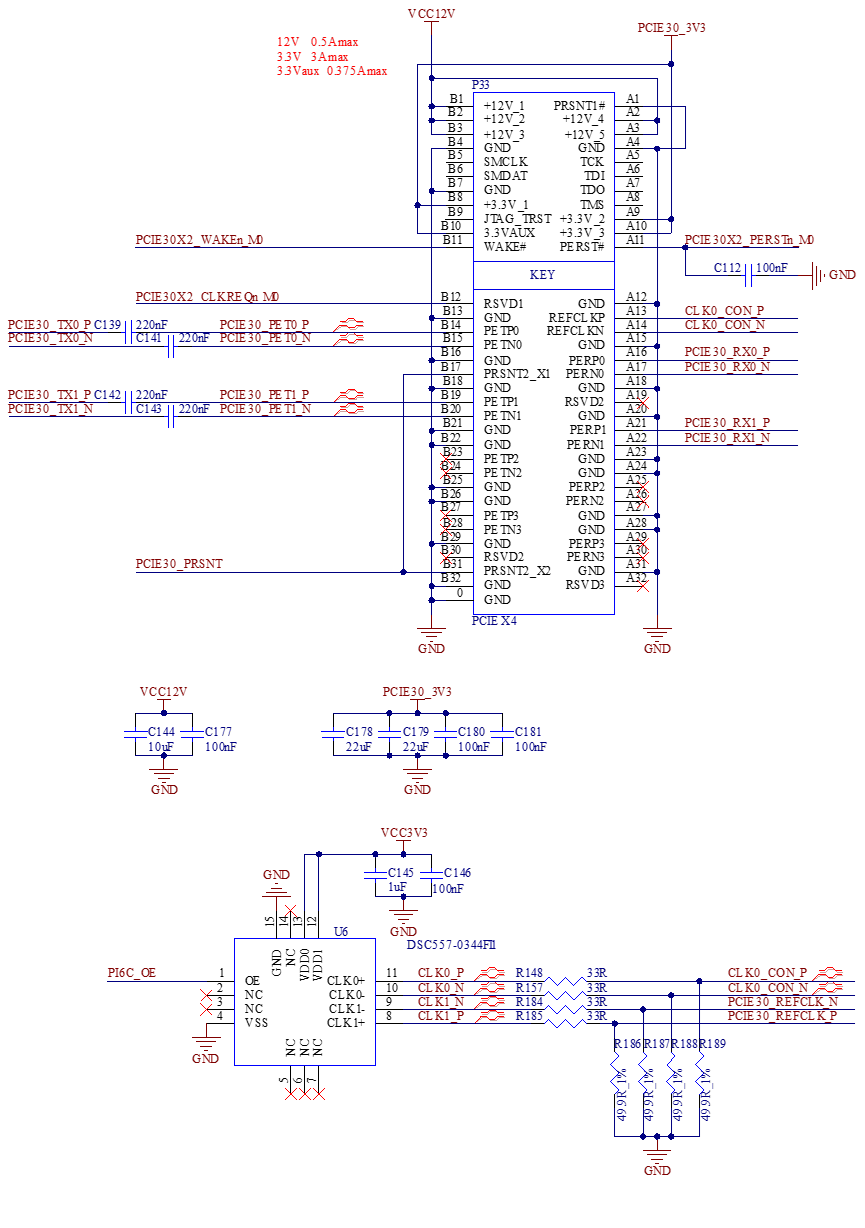

3.5.19 PCIE3.0 Interface

The development board supports one PCIE 3.0 X2 interface, which is led out through a PCIE X4 standard adapter card socket, making it convenient for you to connect various PCIE devices.

Since PCIE devices do not support hot - plug and have high requirements for power supply stability, a BUCK - type DCDC is used to provide 3.3V power.

Note:

The PCIE30_REFCLK_P/N on the SoM only supports input clock. The clock chip U6 on the carrier board is required to provide a bidirectional HCSL level clock of the same source for RC and EP;

PCIE30X2_CLKREQn, PCIE30X1_CLKREQn, PCIE30X2_WAKEn, and PCIE30X1_WAKEn must use function pins and cannot be replaced by GPIO. Specifically, when making a selection, you must choose all _M0 or _M1 or _M2, not one _M0 and one _M1;

PCIE30X2_PERSTn and PCIE30X1_PERSTn can either use function pins or be replaced by GPIO. When choosing function pins, they must be in the same group _Mx as PCIE30X2_CLKREQn, PCIE30X2_WAKEn, PCIE30X1_CLKREQn, and PCIE30X1_WAKEn;

PCIE30_PRSNT is the Add In Card insertion detection pin, which can use GPIO;

An 85 Ω differential impedance is required for PCIe TX/RX data and a 100 Ω differential impedance is required for the CLK reference clock.

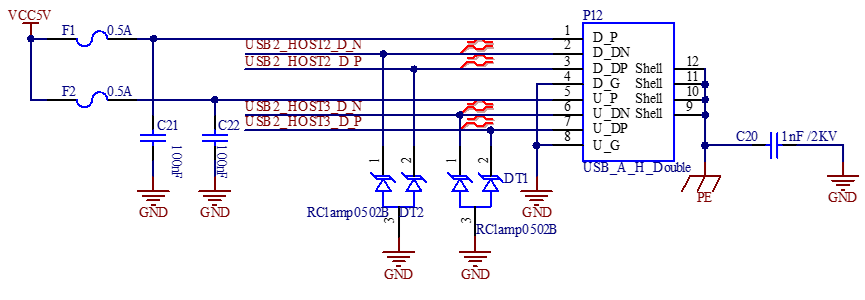

3.5.20 USB HOST Interface

The development board provides two USB2.0 interfaces, which are led out through the USB Type-A socket with A current limit of 0.5A.

Note:

All USB data cables need to have a 90Ω differential impedance;

Please select appropriate ESD devices.

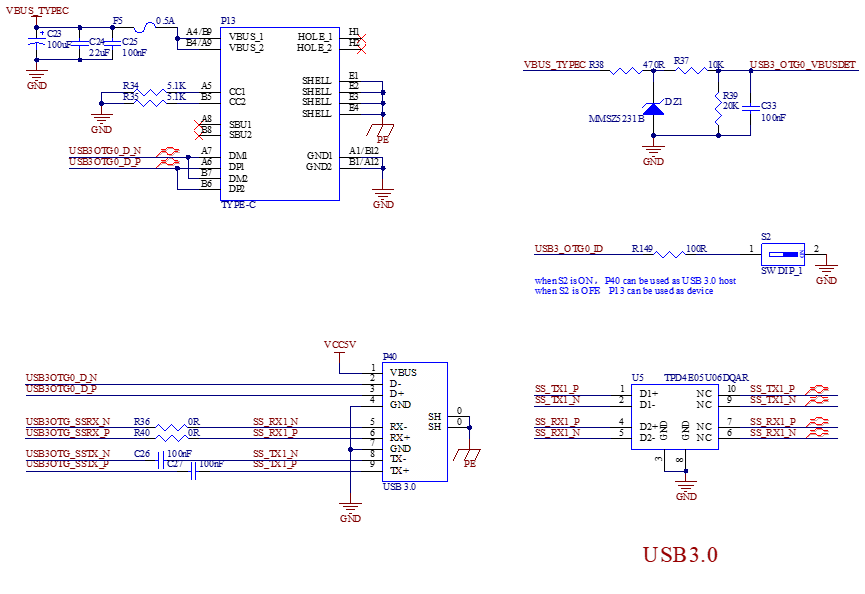

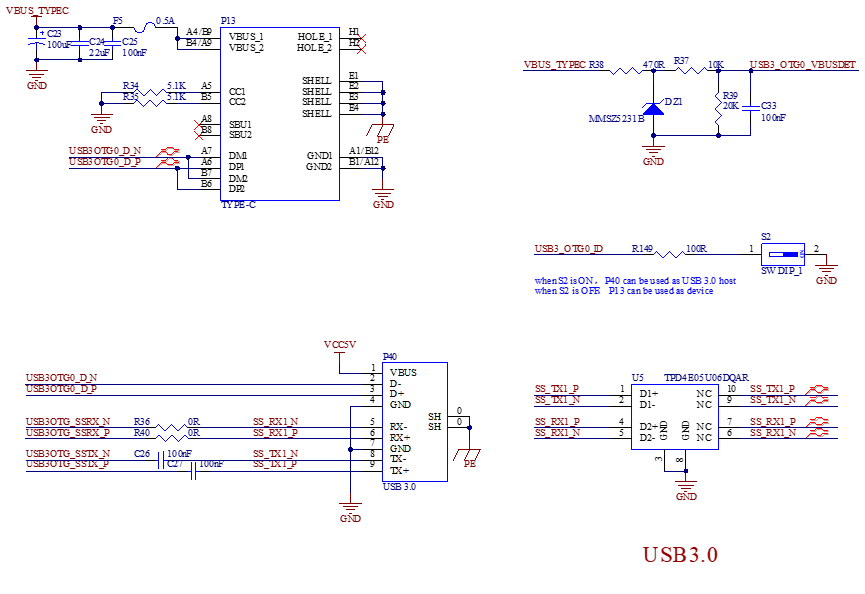

3.5.21 USB3.0 Interface

As shown in the figure above, the USB 2.0 signal line in the USB3.0 interface is multiplexed with the download interface. Before the SoM is started, the USB3.0 OTG defaults to the device mode. When the USB 2.0 signal line is used to flash the image, the USB-TYPE-C line is connected to the P13 socket of the development board. There is no need to configure the ID pin. Press and hold the K2/K8 button and power on to enter the recovery/maskrom mode programming system.

After the SoM starts, you can switch between the host and device modes through S2. When using the USB 3.0 function, switch S2 to ON and insert the USB device into the P40 socket on the development board.

Note:

**Only the native USB3.0 OTG of the SoM supports USB system flashing; **

All USB data cables need to have a 90Ω differential impedance;

Please select appropriate ESD devices;

The USB3_OTG0_VBUSDET needs to detect voltage to enable the USB function normally.

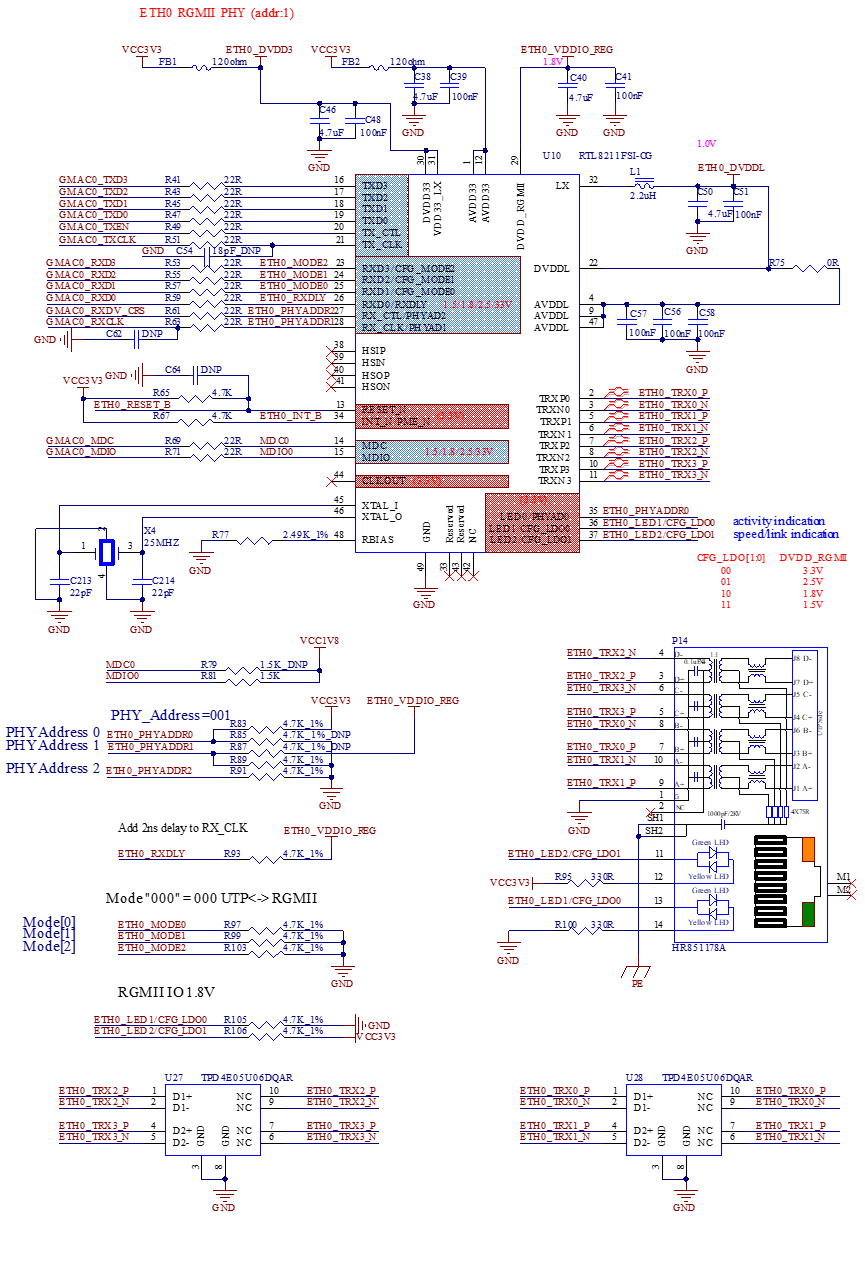

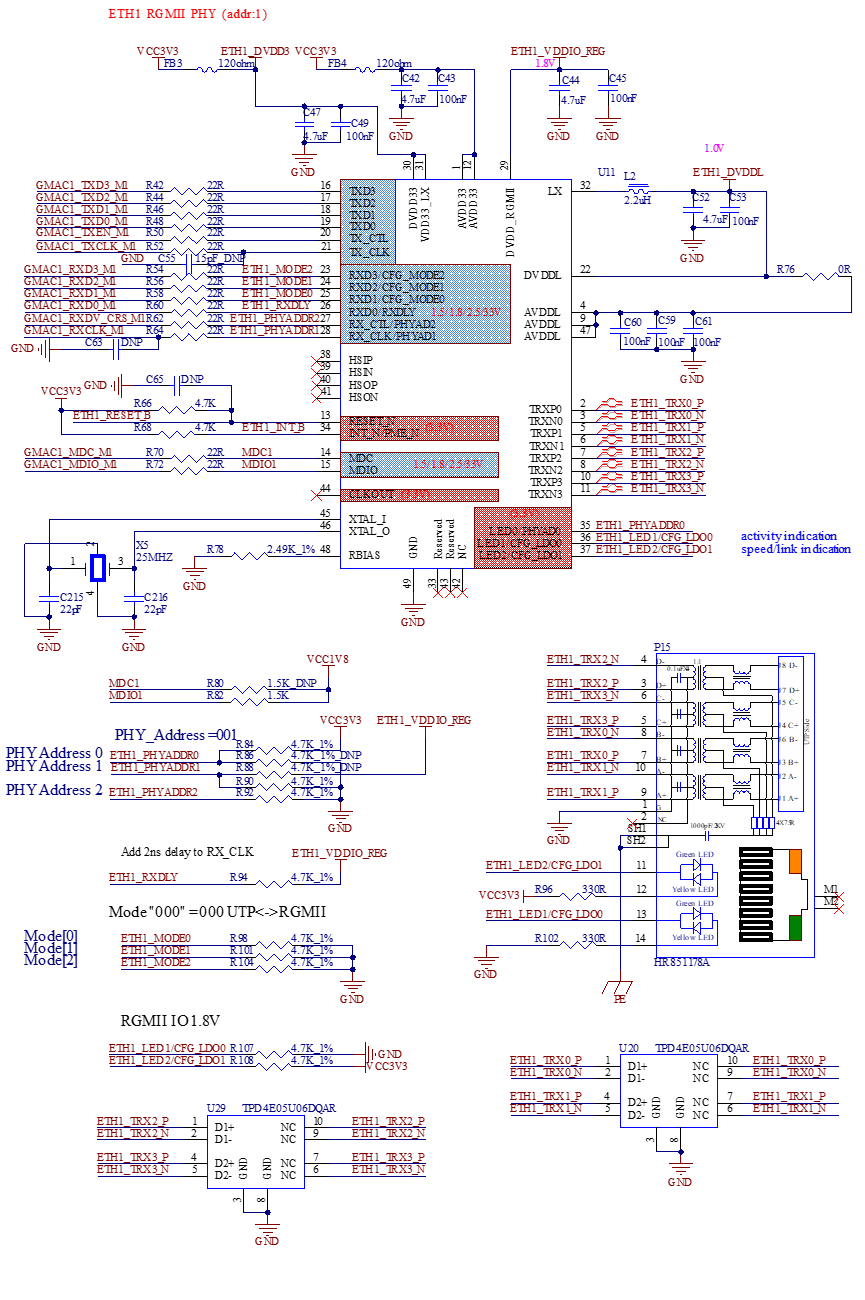

3.5.22 Ethernet Interface

The development board supports 2 x Ethernet with 10/100/1000Mbps adaptive speed, which are led out through P14 and P15 respectively.

Note:

**The TX and RX groups of the RGMII signals need to be equal - length within the group; **

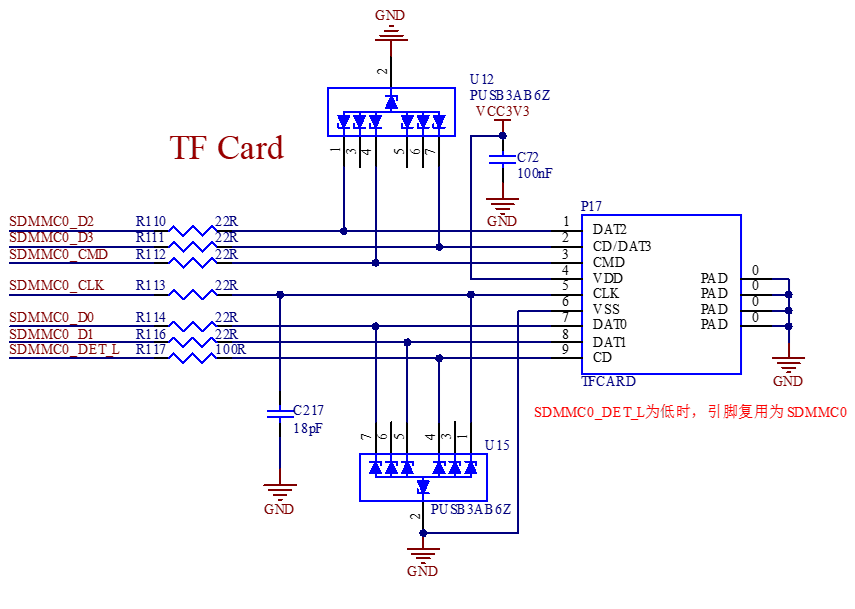

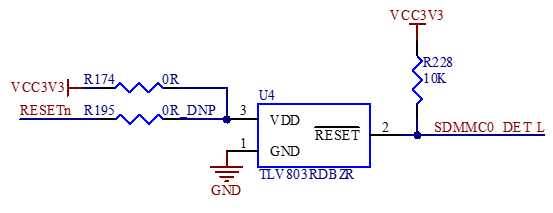

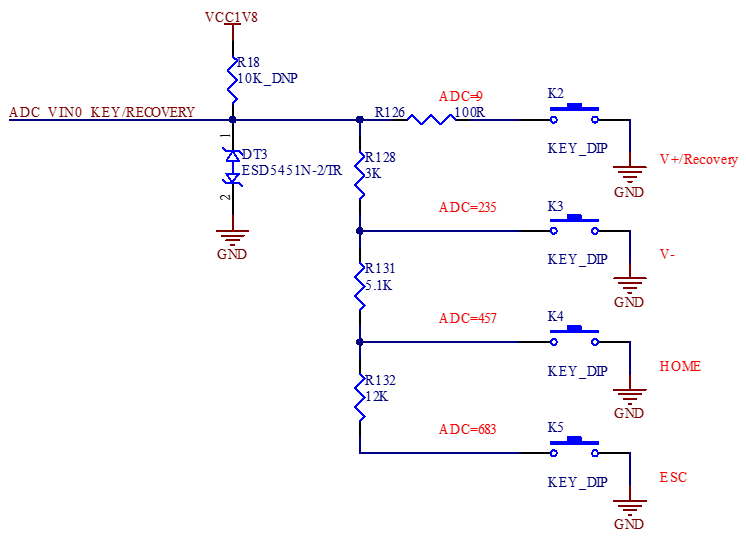

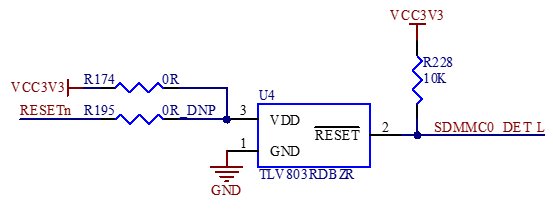

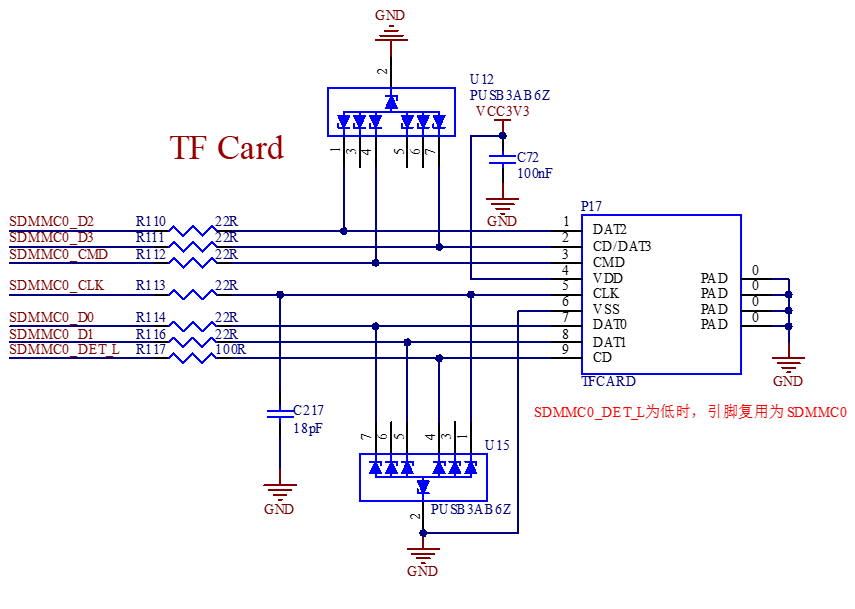

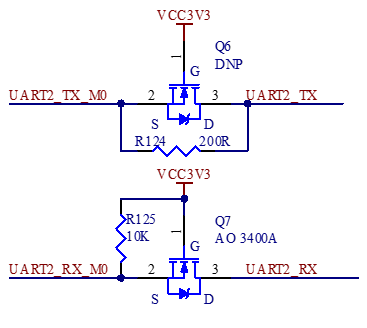

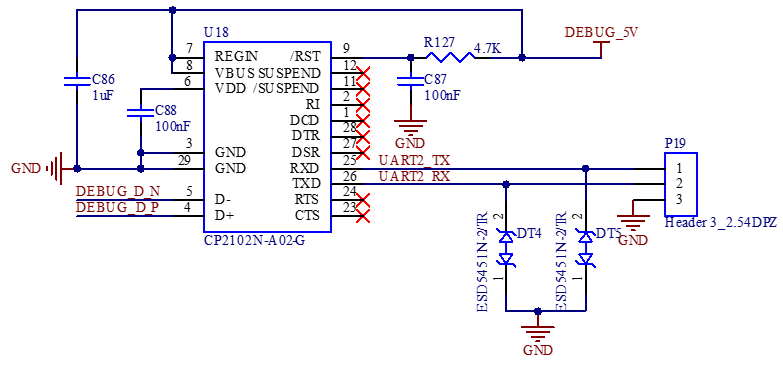

**The RGMII and MDIO/MDC have the same level, which can be configured by CFG_LDO[1:0]; **